# **RP2040** Datasheet

A microcontroller by Raspberry Pi

# Colophon

Copyright © 2020 Raspberry Pi (Trading) Ltd.

The documentation of the RP2040 microcontroller is licensed under a Creative Commons Attribution-NoDerivatives 4.0 International (CC BY-ND).

Portions Copyright © 2019 Synopsys, Inc.

All rights reserved. Used with permission. Synopsys & DesignWare are registered trademarks of Synopsys, Inc.

Portions Copyright © 2000-2001, 2005, 2007, 2009, 2011-2012, 2016 ARM Limited.

All rights reserved. Used with permission.

build-date: 2021-04-13 build-version: cb97422-clean

#### About the SDK

Throughout the text "the SDK" refers to our Raspberry Pi Pico SDK. More details about the SDK can be found in the Raspberry Pi Pico C/C++ SDK book. Source code included in the documentation is Copyright © 2020 Raspberry Pi (Trading) Ltd. and licensed under the 3-Clause BSD license.

## Legal Disclaimer Notice

TECHNICAL AND RELIABILITY DATA FOR RASPBERRY PI PRODUCTS (INCLUDING DATASHEETS) AS MODIFIED FROM TIME TO TIME ("RESOURCES") ARE PROVIDED BY RASPBERRY PI (TRADING) LTD ("RPTL) "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW IN NO EVENT SHALL RPTL BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THE RESOURCES, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

RPTL reserves the right to make any enhancements, improvements, corrections or any other modifications to the RESOURCES or any products described in them at any time and without further notice.

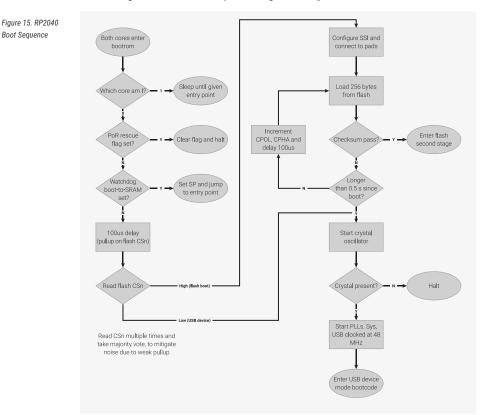

The RESOURCES are intended for skilled users with suitable levels of design knowledge. Users are solely responsible for their selection and use of the RESOURCES and any application of the products described in them. User agrees to indemnify and hold RPTL harmless against all liabilities, costs, damages or other losses arising out of their use of the RESOURCES.

RPTL grants users permission to use the RESOURCES solely in conjunction with the Raspberry Pi products. All other use of the RESOURCES is prohibited. No licence is granted to any other RPTL or other third party intellectual property right.

HIGH RISK ACTIVITIES. Raspberry Pi products are not designed, manufactured or intended for use in hazardous environments requiring fail safe performance, such as in the operation of nuclear facilities, aircraft navigation or communication systems, air traffic control, weapons systems or safety-critical applications (including life support systems and other medical devices), in which the failure of the products could lead directly to death, personal injury or severe physical or environmental damage ("High Risk Activities"). RPTL specifically disclaims any express or implied warranty of fitness for High Risk Activities and accepts no liability for use or inclusions of Raspberry Pi products in High Risk Activities.

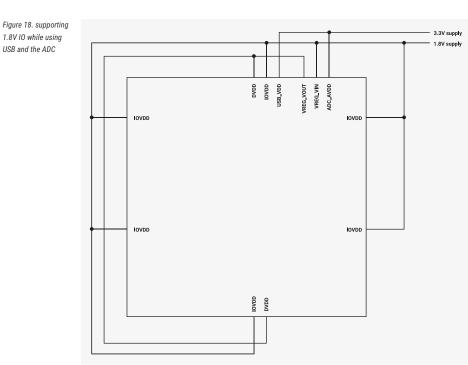

Raspberry Pi products are provided subject to RPTL's Standard Terms. RPTL's provision of the RESOURCES does not

expand or otherwise modify RPTL's Standard Terms including but not limited to the disclaimers and warranties expressed in them.

# **Table of Contents**

| Colophon                                                                                  | . 1 |

|-------------------------------------------------------------------------------------------|-----|

| Legal Disclaimer Notice                                                                   | . 1 |

| 1. Introduction                                                                           | . 9 |

| 1.1. Why is the chip called RP2040?                                                       |     |

| 1.2. Summary                                                                              | 10  |

| 1.3. The Chip                                                                             | 10  |

| 1.4. Pinout Reference.                                                                    | 11  |

| 1.4.1. Pin Locations                                                                      | 11  |

| 1.4.2. Pin Descriptions                                                                   | 12  |

| 1.4.3. GPIO Functions                                                                     |     |

| 2. System Description                                                                     | 15  |

| 2.1. Bus Fabric                                                                           | 15  |

| 2.1.1. AHB-Lite Crossbar                                                                  | 16  |

| 2.1.2. Atomic Register Access                                                             | 18  |

| 2.1.3. APB Bridge                                                                         | 18  |

| 2.1.4. Narrow IO Register Writes                                                          | 18  |

| 2.1.5. List of Registers                                                                  | 19  |

| 2.2. Address Map                                                                          | 24  |

| 2.2.1. Summary.                                                                           | 24  |

| 2.2.2. Detail                                                                             |     |

| 2.3. Processor subsystem                                                                  |     |

| 2.3.1. SIO                                                                                |     |

| 2.3.2. Interrupts.                                                                        | 60  |

| 2.3.3. Event Signals                                                                      |     |

| 2.3.4. Debug                                                                              |     |

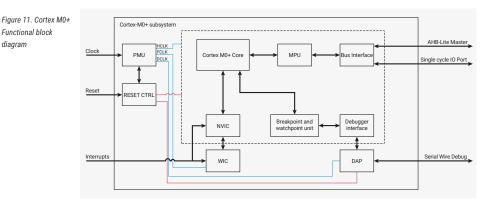

| 2.4. Cortex-M0+                                                                           |     |

| 2.4.1. Features                                                                           |     |

| 2.4.2. Functional Description                                                             |     |

| 2.4.3. Programmer's model                                                                 |     |

| 2.4.4. System control                                                                     |     |

| 2.4.5. NVIC.                                                                              |     |

| 2.4.6. MPU                                                                                |     |

| 2.4.7. Debug                                                                              |     |

| 2.4.8. List of Registers                                                                  |     |

| 2.5. DMA                                                                                  |     |

| 2.5.1. Configuring Channels                                                               |     |

| 2.5.2. Starting Channels                                                                  |     |

| 2.5.3. Data Request (DREQ).                                                               |     |

|                                                                                           | 97  |

| 2.5.5. Additional Features                                                                |     |

| 2.5.6. Example Use Cases                                                                  |     |

| 2.5.7. List of Registers                                                                  |     |

| 2.6. Memory                                                                               |     |

| 2.6.1. ROM                                                                                |     |

| 2.6.2. SRAM                                                                               |     |

| 2.6.3. Flash                                                                              |     |

| 2.0.3. Flash                                                                              |     |

| 2.8. Bootrom                                                                              |     |

|                                                                                           |     |

| 2.8.1. Processor Controlled Boot Sequence       1         2.8.2. Bootrom Contents       1 |     |

| 2.8.2. Bootrom Contents                                                                   |     |

| 2.8.4. USB Mass Storage Interface 1                                                       |     |

|                                                                                           |     |

| 2.9. Power Supplies                                                                       |     |

| 2.9.1. Digital IO Supply (IOVDD)                                                          |     |

| 2.9.2. Digital Core Supply (DVDD)                                                         | /9  |

| 2.9.3. On-Chip Voltage Regulator Input Supply (VREG_VIN) | . 179 |

|----------------------------------------------------------|-------|

| 2.9.4. USB PHY Supply (USB_VDD)                          |       |

| 2.9.5. ADC Supply (ADC_AVDD)                             | . 179 |

| 2.9.6. Power Supply Sequencing                           |       |

| 2.9.7. Power Supply Schemes                              | . 180 |

| 2.10. Core Supply Regulator                              |       |

| 2.10.1. Application Circuit                              |       |

| 2.10.2. Operating Modes                                  |       |

| 2.10.3. Output Voltage Select                            |       |

| 2.10.4. Status                                           |       |

| 2.10.5. Current Limit                                    |       |

| 2.10.6. List of Registers                                |       |

| 2.10.7. Detailed Specifications                          |       |

| 2.11. Power Control                                      |       |

| 2.11.2. SLEEP State                                      |       |

| 2.11.2. SLEEP State<br>2.11.3. DORMANT State             |       |

| 2.11.4. Memory Power Down                                |       |

| 2.11.5. Programmer's Model                               |       |

| 2.12. Chip-Level Reset                                   |       |

| 2.12.1. Overview                                         |       |

| 2.12.2. Power-on Reset                                   |       |

| 2.12.3. Brown-out Detection                              |       |

| 2.12.4. Supply Monitor                                   | . 194 |

| 2.12.5. External Reset                                   | . 194 |

| 2.12.6. Rescue Debug Port Reset                          | . 194 |

| 2.12.7. Source of Last Reset                             | . 194 |

| 2.12.8. List of Registers.                               | . 195 |

| 2.13. Power-On State Machine                             | . 195 |

| 2.13.1. Overview                                         |       |

| 2.13.2. Power On Sequence                                |       |

| 2.13.3. Register Control                                 |       |

| 2.13.4. Interaction with Watchdog                        |       |

| 2.13.5. List of Registers                                |       |

| 2.14. Subsystem Resets                                   |       |

| 2.14.1. Overview                                         |       |

| 2.14.2. Programmer's Model                               |       |

| 2.14.3. List of Registers.                               |       |

| 2.15. Clocks                                             |       |

| 2.15.2. Clock sources                                    |       |

| 2.15.3. Clock Sources<br>2.15.3. Clock Generators        |       |

| 2.15.4. Frequency Counter                                |       |

| 2.15.5. Resus                                            |       |

| 2.15.6. Programmer's Model                               |       |

| 2.15.7. List of Registers                                | . 218 |

| 2.16. Crystal Oscillator (XOSC)                          |       |

| 2.16.1. Overview                                         | . 240 |

| 2.16.2. Usage                                            | . 240 |

| 2.16.3. Startup Delay                                    | . 240 |

| 2.16.4. XOSC Counter                                     | . 241 |

| 2.16.5. DORMANT mode                                     |       |

| 2.16.6. Programmer's Model                               |       |

| 2.16.7. List of Registers                                |       |

| 2.17. Ring Oscillator (ROSC)                             |       |

| 2.17.1. Overview                                         |       |

| 2.17.2. ROSC/XOSC trade-offs                             |       |

| 2.17.3. Modifying the frequency                          |       |

| 2.17.4. ROSC divider                                     |       |

| 2.17.5. Random Number Generator                          | . 246 |

| 2.17.6. ROSC Counter                       | . 246 |

|--------------------------------------------|-------|

| 2.17.7. DORMANT mode                       | . 246 |

| 2.17.8. List of Registers                  | . 247 |

| 2.18. PLL                                  | . 251 |

| 2.18.1. Overview                           | . 251 |

| 2.18.2. Calculating PLL parameters         | . 251 |

| 2.18.3. Configuration                      |       |

| 2.18.4. List of Registers                  |       |

| 2.19. GPI0                                 |       |

| 2.19.1. Overview                           |       |

| 2.19.2. Function Select                    |       |

| 2.19.3. Interrupts                         |       |

| 2.19.4. Pads                               |       |

| 2.19.5. Software Examples                  |       |

| 2.19.6. List of Registers                  |       |

| •                                          |       |

| 2.20. Sysinfo                              |       |

| 2.20.1. Overview                           |       |

| 2.20.2. List of Registers                  |       |

| 2.21. Syscfg                               |       |

| 2.21.1. Overview                           |       |

| 2.21.2. List of Registers                  |       |

| 2.22. TBMAN.                               |       |

| 2.22.1. List of Registers                  |       |

| 3. PIO.                                    |       |

| 3.1. Overview                              |       |

| 3.2. Programmer's Model                    |       |

| 3.2.1. PIO Programs.                       |       |

| 3.2.2. Control Flow                        |       |

| 3.2.3. Registers                           |       |

| 3.2.4. Stalling                            | . 336 |

| 3.2.5. Pin Mapping                         | . 337 |

| 3.2.6. IRQ Flags                           | . 337 |

| 3.2.7. Interactions Between State Machines |       |

| 3.3. PIO Assembler (pioasm)                | . 338 |

| 3.3.1. Directives                          | . 338 |

| 3.3.2. Values                              | . 339 |

| 3.3.3. Expressions                         | . 339 |

| 3.3.4. Comments                            | . 339 |

| 3.3.5. Labels                              | . 339 |

| 3.3.6. Instructions                        | . 340 |

| 3.3.7. Pseudoinstructions                  | . 340 |

| 3.4. Instruction Set                       | . 340 |

| 3.4.1. Summary                             | . 340 |

| 3.4.2. JMP                                 | . 341 |

| 3.4.3. WAIT                                | . 342 |

| 3.4.4. IN                                  | . 343 |

| 3.4.5. OUT                                 | . 344 |

| 3.4.6. PUSH                                | . 345 |

| 3.4.7. PULL                                | . 346 |

| 3.4.8. MOV                                 | . 347 |

| 3.4.9. IRQ                                 | . 348 |

| 3.4.10. SET                                | . 349 |

| 3.5. Functional Details                    | . 350 |

| 3.5.1. Side-set                            |       |

| 3.5.2. Program Wrapping                    |       |

| 3.5.3. FIFO Joining                        |       |

| 3.5.4. Autopush and Autopull               |       |

| 3.5.5. Clock Dividers                      |       |

| 3.5.6. GPIO Mapping                        |       |

| 3.5.7. Forced and EXEC'd Instructions.     |       |

| 0.0.7.1 01000 and EAEO a matractions.      |       |

| 3.6. Examples                                                    |     |

|------------------------------------------------------------------|-----|

| 3.6.1. Duplex SPI                                                | 363 |

| 3.6.2. WS2812 LEDs.                                              | 367 |

| 3.6.3. UART TX                                                   | 369 |

| 3.6.4. UART RX                                                   |     |

| 3.6.5. Manchester Serial TX and RX                               |     |

| 3.6.6. Differential Manchester (BMC) TX and RX                   |     |

| 3.6.7. I2C                                                       |     |

| 3.6.8. PWM                                                       |     |

| 3.6.9. Addition                                                  |     |

| 3.6.10. Further Examples.                                        |     |

| 3.7. List of Registers                                           |     |

| 4. Peripherals                                                   |     |

| •                                                                |     |

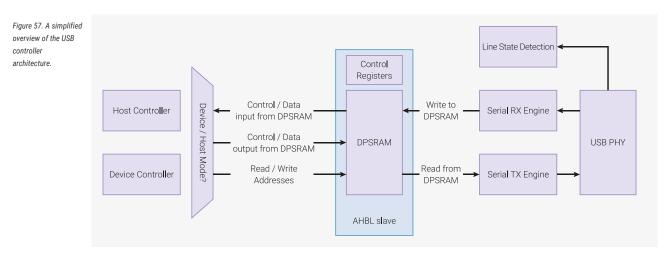

| 4.1. USB.                                                        |     |

| 4.1.1. Overview                                                  |     |

| 4.1.2. Architecture                                              |     |

| 4.1.3. Programmer's Model                                        |     |

| 4.1.4. List of Registers                                         |     |

| References                                                       | 435 |

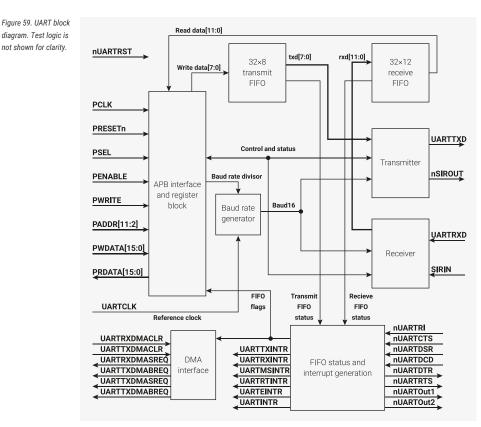

| 4.2. UART                                                        | 435 |

| 4.2.1. Overview                                                  | 436 |

| 4.2.2. Functional description                                    | 436 |

| 4.2.3. Operation                                                 | 438 |

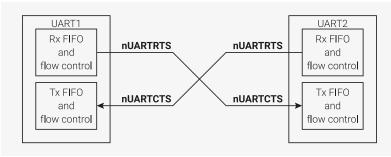

| 4.2.4. UART hardware flow control                                | 441 |

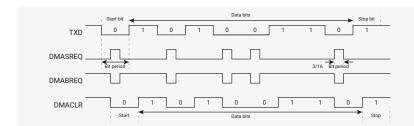

| 4.2.5. UART DMA Interface                                        |     |

| 4.2.6. Interrupts                                                |     |

| 4.2.7. Programmer's Model                                        |     |

| 4.2.8. List of Registers                                         |     |

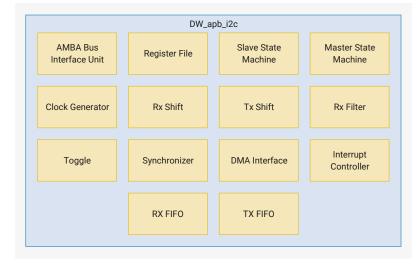

| 4.3. I2C.                                                        |     |

| 4.3.1. Features                                                  |     |

| 4.3.2. IP Configuration                                          |     |

| 4.3.3. I2C Overview.                                             |     |

| 4.3.4. I2C Terminology                                           |     |

|                                                                  |     |

| 4.3.5. I2C Behaviour                                             |     |

| 4.3.6. I2C Protocols                                             |     |

| 4.3.7. Tx FIFO Management and START, STOP and RESTART Generation |     |

| 4.3.8. Multiple Master Arbitration                               |     |

| 4.3.9. Clock Synchronization.                                    |     |

| 4.3.10. Operation Modes                                          |     |

| 4.3.11. Spike Suppression                                        |     |

| 4.3.12. Fast Mode Plus Operation                                 |     |

| 4.3.13. Bus Clear Feature                                        | 478 |

| 4.3.14. IC_CLK Frequency Configuration                           | 479 |

| 4.3.15. DMA Controller Interface                                 | 483 |

| 4.3.16. Operation of Interrupt Registers                         | 484 |

| 4.3.17. List of Registers                                        |     |

| 4.4. SPI                                                         |     |

| 4.4.1. Overview                                                  |     |

| 4.4.2. Functional Description                                    |     |

| 4.4.3. Operation                                                 |     |

| 4.4.4. List of Registers                                         |     |

| 4.5. PWM                                                         |     |

| 4.5.1. Overview                                                  |     |

|                                                                  |     |

| 4.5.2. Programmer's Model.                                       |     |

| 4.5.3. List of Registers                                         |     |

| 4.6. Timer                                                       |     |

| 4.6.1. Overview                                                  |     |

| 4.6.2. Counter                                                   |     |

| 4.6.3. Alarms                                                    |     |

| 4.6.4. Programmer's Model.                                       | 557 |

| 4.6.5. List of Registers                  |  |

|-------------------------------------------|--|

| 4.7. Watchdog                             |  |

| 4.7.1. Overview                           |  |

| 4.7.2. Tick generation                    |  |

| 4.7.3. Watchdog Counter                   |  |

| 4.7.4. Scratch Registers                  |  |

| 4.7.5. Programmer's Model                 |  |

| 4.7.6. List of Registers                  |  |

| 4.8. RTC                                  |  |

| 4.8.1. Storage Format                     |  |

| 4.8.2. Leap year                          |  |

| 4.8.3. Interrupts                         |  |

| 4.8.4. Reference clock                    |  |

| 4.8.5. Programmer's Model                 |  |

| 4.8.6. List of Registers                  |  |

| 4.9. ADC and Temperature Sensor           |  |

| 4.9.1. Features                           |  |

| 4.9.2. ADC controller                     |  |

| 4.9.3. SAR ADC                            |  |

| 4.9.4. Temperature Sensor                 |  |

| 4.9.5. List of Registers                  |  |

| 4.9.3. List of Registers.<br>4.10. SSI    |  |

| 4.10.1. Overview                          |  |

| 4.10.2. Features                          |  |

| 4.10.3. IP Modifications.                 |  |

| 4.10.4. Clock Ratios                      |  |

| 4.10.5. Transmit and Receive FIFO Buffers |  |

| 4.10.6. 32-Bit Frame Size Support         |  |

| 4.10.7. SSI Interrupts                    |  |

| 4.10.8. Transfer Modes                    |  |

|                                           |  |

| 4.10.9. Operation Modes                   |  |

| 4.10.10. Partner Connection Interfaces    |  |

| 4.10.11. DMA Controller Interface         |  |

| 4.10.12. APB Interface                    |  |

| 4.10.13. List of Registers.               |  |

| 5. Electrical and Mechanical              |  |

| 5.1. Package                              |  |

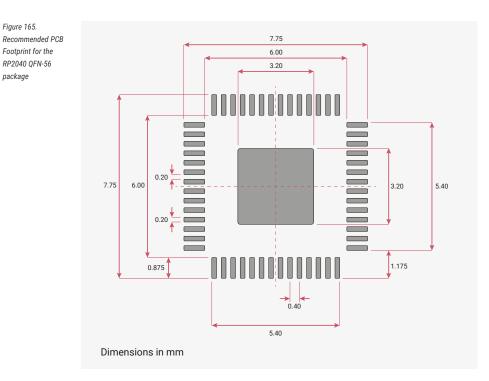

| 5.1.1. Recommended PCB Footprint          |  |

| 5.1.2. Compliance                         |  |

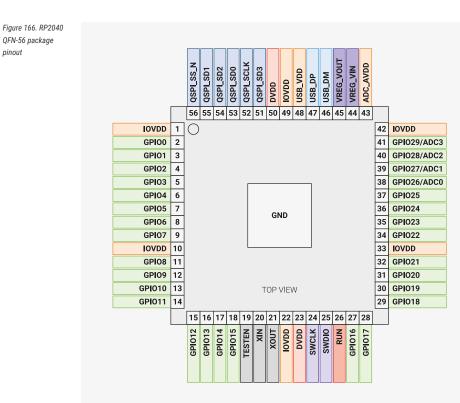

| 5.2. Pinout                               |  |

| 5.2.1. Pin Locations                      |  |

| 5.2.2. Pin Definitions                    |  |

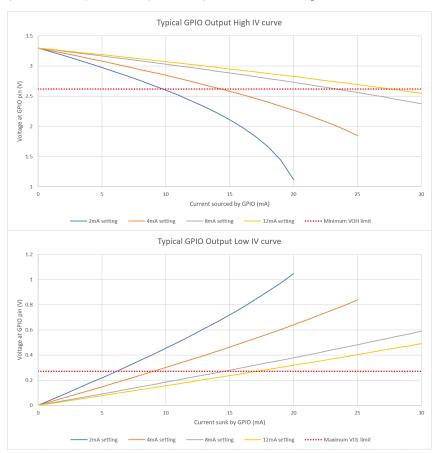

| 5.2.3. Pin Specifications                 |  |

| 5.3. Power Supplies                       |  |

| 5.4. Power Consumption                    |  |

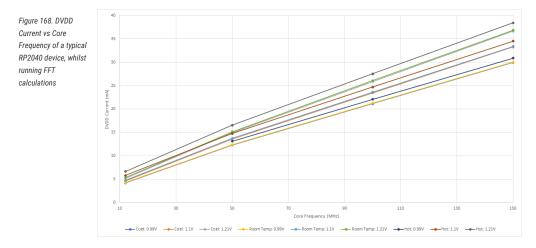

| 5.4.1. Power Consumption versus frequency |  |

| Appendix A: Register Field Types          |  |

| Standard types                            |  |

| RW                                        |  |

| RO                                        |  |

| WO                                        |  |

| Clear types                               |  |

| SC                                        |  |

|                                           |  |

| FIFO types                                |  |

| RF                                        |  |

| WF                                        |  |

| RWF                                       |  |

| Appendix B: Errata                        |  |

| Bootrom                                   |  |

| RP2040-E9          |                          | <br>. 63 |

|--------------------|--------------------------|----------|

| Clocks             |                          | <br>. 63 |

| RP2040-E7          |                          | <br>. 63 |

| RP2040-E10         |                          | <br>. 64 |

| GPIO / ADC         |                          | <br>. 64 |

| RP2040-E6          |                          | <br>. 64 |

| USB                |                          | <br>. 64 |

| RP2040-E2          |                          | <br>. 64 |

| RP2040-E3          |                          | <br>. 64 |

| RP2040-E4          |                          | <br>. 64 |

| RP2040-E5          |                          | <br>. 64 |

| Watchdog           |                          | <br>. 64 |

| RP2040-E1          |                          | <br>. 64 |

| XIP Flash          |                          | <br>. 64 |

| RP2040-E8          |                          | <br>. 64 |

| Appendix C: Docume | entation Release History | <br>. 64 |

# **Chapter 1. Introduction**

Microcontrollers connect the world of software to the world of hardware. They allow developers to write software which interacts with the physical world in the same deterministic, cycle-accurate manner as digital logic. They occupy the bottom left corner of the price/performance space, outselling their more powerful brethren by a factor of ten to one. They are the workhorses that power the digital transformation of our world.

RP2040 is the debut microcontroller from Raspberry Pi. It brings our signature values of high performance, low cost, and ease of use to the microcontroller space.

With a large on-chip memory, symmetric dual-core processor complex, deterministic bus fabric, and rich peripheral set augmented with our unique Programmable I/O (PIO) subsystem, it provides professional users with unrivalled power and flexibility. With detailed documentation, a polished MicroPython port, and a UF2 bootloader in ROM, it has the lowest possible barrier to entry for beginner and hobbyist users.

RP2040 is a stateless device, with support for cached execute-in-place from external QSPI memory. This design decision allows you to choose the appropriate density of non-volatile storage for your application, and to benefit from the low pricing of commodity Flash parts.

RP2040 is manufactured on a modern 40nm process node, delivering high performance, low dynamic power consumption, and low leakage, with a variety of low-power modes to support extended-duration operation on battery power.

Key features:

- Dual ARM Cortex-M0+ @ 133MHz

- · 264kB on-chip SRAM in six independent banks

- Support for up to 16MB of off-chip Flash memory via dedicated QSPI bus

- DMA controller

- Fully-connected AHB crossbar

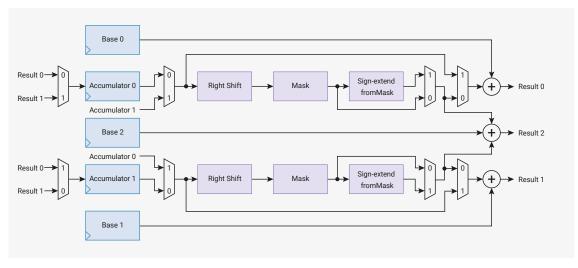

- · Interpolator and integer divider peripherals

- On-chip programmable LDO to generate core voltage

- · 2 on-chip PLLs to generate USB and core clocks

- · 30 GPIO pins, 4 of which can be used as analogue inputs

- Peripherals

- 2 UARTs

- 2 SPI controllers

- 2 I2C controllers

- 16 PWM channels

- USB 1.1 controller and PHY, with host and device support

- 8 PIO state machines

Whatever your microcontroller application, from machine learning to motor control, from agriculture to audio, RP2040 has the performance, feature set, and support to make your product fly.

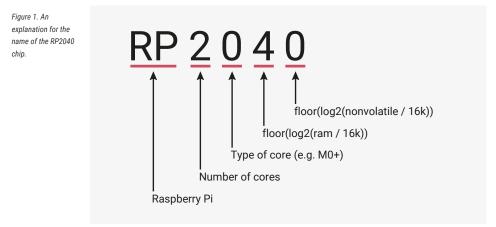

## 1.1. Why is the chip called RP2040?

The post-fix numeral on RP2040 comes from the following,

- 1. Number of processor cores (2)

- 2. Loosely which type of processor (M0+)

- 3. floor(log2(ram / 16k))

- 4. floor(log2(nonvolatile / 16k)) or 0 if no onboard nonvolatile storage

see Figure 1.

## 1.2. Summary

RP2040 is a low-cost, high-performance microcontroller device with flexible digital interfaces. Key features:

- Dual Cortex M0+ processor cores, up to 133 MHz

- 264 kB of embedded SRAM in 6 banks

- 30 multifunction GPIO

- 6 dedicated IO for SPI Flash (supporting XIP)

- · Dedicated hardware for commonly used peripherals

- Programmable IO for extended peripheral support

- 4 channel ADC with internal temperature sensor, 0.5 MSa/s, 12-bit conversion

- USB 1.1 Host/Device

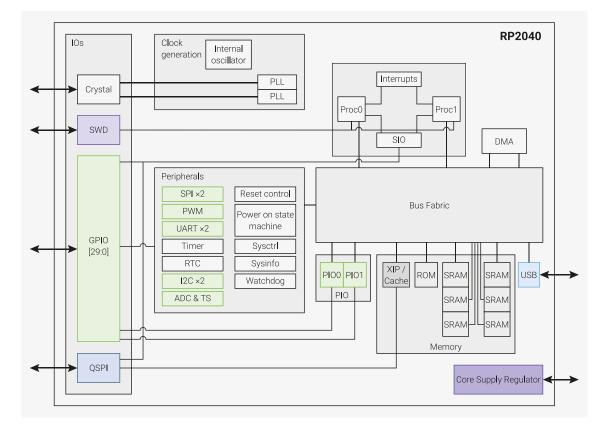

## 1.3. The Chip

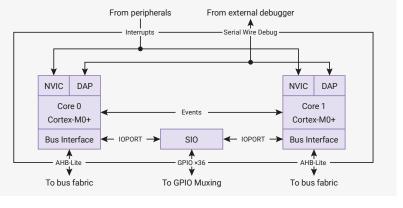

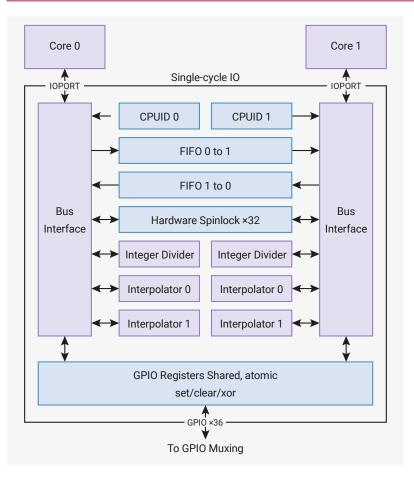

RP2040 has a dual M0+ processor cores, DMA, internal memory and peripheral blocks connected via AHB/APB bus fabric.

#### Figure 2. A system overview of the

RP2040 chip

Code may be executed directly from external memory through a dedicated SPI, DSPI or QSPI interface. A small cache improves performance for typical applications.

Debug is available via the SWD interface.

Internal SRAM can contain code or data. It is addressed as a single 264 kB region, but physically partitioned into 6 banks to allow simultaneous parallel access from different masters.

DMA bus masters are available to offload repetitive data transfer tasks from the processors.

GPIO pins can be driven directly, or from a variety of dedicated logic functions.

Dedicated hardware for fixed functions such as SPI, I2C, UART.

Flexible configurable PIO controllers can be used to provide a wide variety of IO functions.

A USB controller with embedded PHY can be used to provide FS/LS Host or Device connectivity under software control.

Four ADC inputs which are shared with GPIO pins.

Two PLLs to provide a fixed 48MHz clock for USB or ADC, and a flexible system clock up to 133MHz.

An internal Voltage Regulator to supply the core voltage so the end product only needs supply the IO voltage.

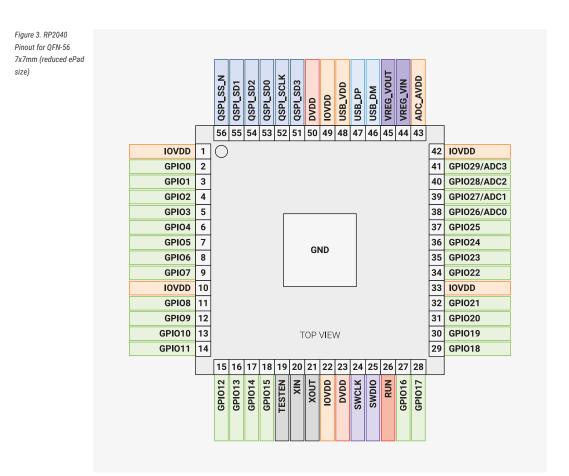

## **1.4. Pinout Reference**

This section provides a quick reference for pinout and pin functions. Full details, including electrical specifications and package drawings, can be found in Chapter 5.

## 1.4.1. Pin Locations

## 1.4.2. Pin Descriptions

Table 1. The function of each pin is briefly described here. Full electrical specifications can be found in Chapter 5.

| Name                 | Description                                                                                                                                                                                            |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOx                | General-purpose digital input and output. RP2040 can connect one of a number of internal peripherals to each GPIO, or control GPIOs directly from software.                                            |

| GPIOx/ADCy           | General-purpose digital input and output, with analogue-to-digital converter function. The RP2040 ADC has an analogue multiplexer which can select any one of these pins, and sample the voltage.      |

| QSPIx                | Interface to a SPI, Dual-SPI or Quad-SPI flash device, with execute-in-place support. These pins can also be used as software-controlled GPIOs, if they are not required for flash access.             |

| USB_DM and<br>USB_DP | USB controller, supporting Full Speed device and Full/Low Speed host. A $27\Omega$ series termination resistor is required on each pin, but bus pullups and pulldowns are provided internally.         |

| XIN and XOUT         | Connect a crystal to RP2040's crystal oscillator. XIN can also be used as a single-ended CMOS clock input, with XOUT disconnected. The USB bootloader requires a 12 MHz crystal or 12 MHz clock input. |

| RUN                  | Global asynchronous reset pin. Reset when driven low, run when driven high. If no external reset is required, this pin can be tied directly to IOVDD.                                                  |

| SWCLK and SWDIO      | Access to the internal Serial Wire Debug multi-drop bus. Provides debug access to both processors, and can be used to download code.                                                                   |

| TESTEN               | Factory test mode pin. Tie to GND.                                                                                                                                                                     |

| GND                  | Single external ground connection, bonded to a number of internal ground pads on the RP2040 die.                                                                                                       |

| IOVDD                | Power supply for digital GPIOs, nominal voltage 1.8 V to 3.3 V                                                                                                                                         |

| Name      | Description                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|

| USB_VDD   | Power supply for internal USB Full Speed PHY, nominal voltage 3.3 V                                                         |

| ADC_AVDD  | Power supply for analogue-to-digital converter, nominal voltage 3.3 V                                                       |

| VREG_VIN  | Power input for the internal core voltage regulator, nominal voltage 1.8 V to 3.3 V                                         |

| VREG_VOUT | Power output for the internal core voltage regulator, nominal voltage 1.1 V, 100 mA max current                             |

| DVDD      | Digital core power supply, nominal voltage 1.1 V. Can be connected to VREG_VOUT, or to some other board-level power supply. |

## 1.4.3. GPIO Functions

Each individual GPIO pin can be connected to an internal peripheral via the GPIO functions defined below. Some internal peripheral connections appear in multiple places to allow some system level flexibility. SIO, PIOO and PIO1 can connect to all GPIO pins and are controlled by software (or software controlled state machines) so can be used to implement many functions.

Table 2. General Purpose Input/Output (GPIO) Bank 0 Functions

|      | Function |           |          |        |     |      |      |              |               |

|------|----------|-----------|----------|--------|-----|------|------|--------------|---------------|

| GPIO | F1       | F2        | F3       | F4     | F5  | F6   | F7   | F8           | F9            |

| 0    | SPI0 RX  | UART0 TX  | I2C0 SDA | PWM0 A | SIO | PIO0 | PI01 |              | USB OVCUR DET |

| 1    | SPI0 CSn | UARTO RX  | I2C0 SCL | PWM0 B | SIO | PIO0 | PI01 |              | USB VBUS DET  |

| 2    | SPI0 SCK | UARTO CTS | I2C1 SDA | PWM1 A | SIO | PIO0 | PI01 |              | USB VBUS EN   |

| 3    | SPI0 TX  | UART0 RTS | I2C1 SCL | PWM1 B | SIO | PIO0 | PI01 |              | USB OVCUR DET |

| 4    | SPI0 RX  | UART1 TX  | I2C0 SDA | PWM2 A | SIO | PIO0 | PI01 |              | USB VBUS DET  |

| 5    | SPI0 CSn | UART1 RX  | I2C0 SCL | PWM2 B | SIO | PIO0 | PI01 |              | USB VBUS EN   |

| 6    | SPI0 SCK | UART1 CTS | I2C1 SDA | PWM3 A | SIO | PIO0 | PI01 |              | USB OVCUR DET |

| 7    | SPI0 TX  | UART1 RTS | I2C1 SCL | PWM3 B | SIO | PIO0 | PI01 |              | USB VBUS DET  |

| 8    | SPI1 RX  | UART1 TX  | I2C0 SDA | PWM4 A | SIO | PIO0 | PI01 |              | USB VBUS EN   |

| 9    | SPI1 CSn | UART1 RX  | I2C0 SCL | PWM4 B | SIO | PIO0 | PI01 |              | USB OVCUR DET |

| 10   | SPI1 SCK | UART1 CTS | I2C1 SDA | PWM5 A | SIO | PIO0 | PI01 |              | USB VBUS DET  |

| 11   | SPI1 TX  | UART1 RTS | I2C1 SCL | PWM5 B | SIO | PIO0 | PI01 |              | USB VBUS EN   |

| 12   | SPI1 RX  | UART0 TX  | I2C0 SDA | PWM6 A | SIO | PIO0 | PI01 |              | USB OVCUR DET |

| 13   | SPI1 CSn | UART0 RX  | I2C0 SCL | PWM6 B | SIO | PIO0 | PI01 |              | USB VBUS DET  |

| 14   | SPI1 SCK | UART0 CTS | I2C1 SDA | PWM7 A | SIO | PI00 | PI01 |              | USB VBUS EN   |

| 15   | SPI1 TX  | UART0 RTS | I2C1 SCL | PWM7 B | SIO | PIO0 | PI01 |              | USB OVCUR DET |

| 16   | SPI0 RX  | UART0 TX  | I2C0 SDA | PWM0 A | SIO | PIO0 | PI01 |              | USB VBUS DET  |

| 17   | SPI0 CSn | UART0 RX  | I2C0 SCL | PWM0 B | SIO | PI00 | PI01 |              | USB VBUS EN   |

| 18   | SPI0 SCK | UART0 CTS | I2C1 SDA | PWM1 A | SIO | PIO0 | PI01 |              | USB OVCUR DET |

| 19   | SPI0 TX  | UART0 RTS | I2C1 SCL | PWM1 B | SIO | PIO0 | PI01 |              | USB VBUS DET  |

| 20   | SPI0 RX  | UART1 TX  | I2C0 SDA | PWM2 A | SIO | PIO0 | PI01 | CLOCK GPIN0  | USB VBUS EN   |

| 21   | SPI0 CSn | UART1 RX  | I2C0 SCL | PWM2 B | SIO | PI00 | PI01 | CLOCK GPOUT0 | USB OVCUR DET |

|    | Function | Function  |          |        |     |      |      |              |               |

|----|----------|-----------|----------|--------|-----|------|------|--------------|---------------|

| 22 | SPI0 SCK | UART1 CTS | I2C1 SDA | PWM3 A | SIO | PI00 | PI01 | CLOCK GPIN1  | USB VBUS DET  |

| 23 | SPI0 TX  | UART1 RTS | I2C1 SCL | PWM3 B | SIO | PI00 | PI01 | CLOCK GPOUT1 | USB VBUS EN   |

| 24 | SPI1 RX  | UART1 TX  | I2C0 SDA | PWM4 A | SIO | PI00 | PI01 | CLOCK GPOUT2 | USB OVCUR DET |

| 25 | SPI1 CSn | UART1 RX  | I2C0 SCL | PWM4 B | SIO | PI00 | PI01 | CLOCK GPOUT3 | USB VBUS DET  |

| 26 | SPI1 SCK | UART1 CTS | I2C1 SDA | PWM5 A | SIO | PI00 | PI01 |              | USB VBUS EN   |

| 27 | SPI1 TX  | UART1 RTS | I2C1 SCL | PWM5 B | SIO | PI00 | PI01 |              | USB OVCUR DET |

| 28 | SPI1 RX  | UART0 TX  | I2C0 SDA | PWM6 A | SIO | PI00 | PI01 |              | USB VBUS DET  |

| 29 | SPI1 CSn | UART0 RX  | I2C0 SCL | PWM6 B | SIO | PI00 | PI01 |              | USB VBUS EN   |

Table 3. GPIO bank 0 function descriptions

| Function Name                     | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPIx                              | Connect one of the internal PL022 SPI peripherals to GPIO                                                                                                                                                                                                                                                                                                                                         |

| UARTx                             | Connect one of the internal PL011 UART peripherals to GPIO                                                                                                                                                                                                                                                                                                                                        |

| I2Cx                              | Connect one of the internal DW I2C peripherals to GPIO                                                                                                                                                                                                                                                                                                                                            |

| PWMx A/B                          | Connect a PWM slice to GPIO. There are eight PWM slices, each with two output channels (A/B). The B pin can also be used as an input, for frequency and duty cycle measurement.                                                                                                                                                                                                                   |

| SIO                               | Software control of GPIO, from the single-cycle IO (SIO) block. The SIO function (F5) must be selected for the processors to <i>drive</i> a GPIO, but the input is always connected, so software can check the state of GPIOs at any time.                                                                                                                                                        |

| PIOx                              | Connect one of the programmable IO blocks (PIO) to GPIO. PIO can implement a <i>wide</i> variety of interfaces, and has its own internal pin mapping hardware, allowing flexible placement of digital interfaces on bank 0 GPIOs. The PIO function (F6, F7) must be selected for PIO to <i>drive</i> a GPIO, but the input is always connected, so the PIOs can always see the state of all pins. |

| CLOCK GPINx                       | General purpose clock inputs. Can be routed to a number of internal clock domains on RP2040, e.g. to provide a 1 Hz clock for the RTC, or can be connected to an internal frequency counter.                                                                                                                                                                                                      |

| CLOCK GPOUTx                      | General purpose clock outputs. Can drive a number of internal clocks (including PLL outputs) onto GPIOs, with optional integer divide.                                                                                                                                                                                                                                                            |

| USB OVCUR DET/VBUS<br>DET/VBUS EN | USB power control signals to/from the internal USB controller                                                                                                                                                                                                                                                                                                                                     |

# **Chapter 2. System Description**

This chapter describes the RP2040 key system features including processor, memory, how blocks are connected, clocks, resets, power, and IO. Refer to Figure 2 for an overview diagram.

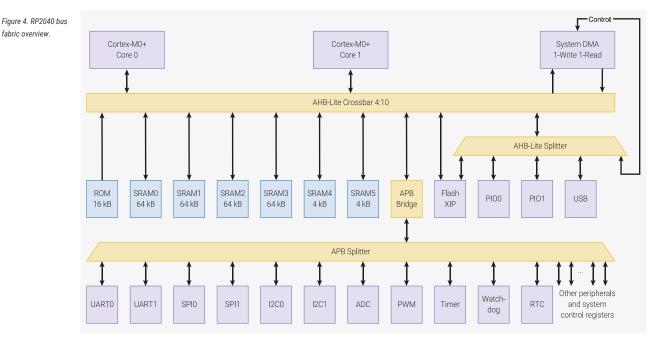

## 2.1. Bus Fabric

The RP2040 bus fabric routes addresses and data across the chip.

Figure 4 shows the high-level structure of the bus fabric. The main AHB-Lite crossbar routes addresses and data between its 4 upstream ports and 10 downstream ports: up to four bus transfers can take place each cycle. All data paths are 32 bits wide. Memory devices have dedicated ports on the main crossbar, to satisfy their high bandwidth requirements. High-bandwidth AHB-Lite peripherals have a shared port on the crossbar, and an APB bridge provides bus access to system control registers and lower-bandwidth peripherals.

The bus fabric connects 4 AHB-Lite masters, i.e. devices which generate addresses:

- Processor core 0

- Processor core 1

- DMA controller Read port

- DMA controller Write port

These are routed through to 10 downstream ports on the main crossbar:

- ROM

- Flash XIP

- SRAM 0 to 5 (one port each)

- Fast AHB-Lite peripherals: PIO0, PIO1, USB, DMA control registers, XIP aux (one shared port)

- Bridge to all APB peripherals, and system control registers

The four bus masters can access any four *different* crossbar ports simultaneously, the bus fabric does not add wait states to any AHB-Lite slave access. So at a system clock of 125 MHz the maximum sustained bus bandwidth is 2.0

GB/s. The system address map has been arranged to make this parallel bandwidth available to as many software use cases as possible – for example, the striped SRAM alias (Section 2.6.2) scatters main memory accesses across four crossbar ports (SRAM0...3), so that more memory accesses can proceed in parallel.

## 2.1.1. AHB-Lite Crossbar

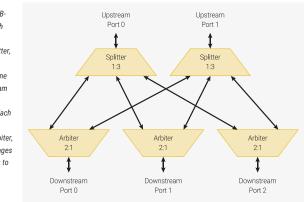

At the centre of the RP2040 bus fabric is a 4:10 fully-connected crossbar. Its 4 upstream ports are connected to the 4 system bus masters, and the 10 downstream ports connect to the highest-bandwidth AHB-Lite slaves (namely the memory interfaces) and to lower layers of the fabric. Figure 5 shows the structure of a 2:3 AHB-Lite crossbar, arranged identically to the 4:10 crossbar on RP2040, but easier to show in the diagram.

Figure 5. A 2:3 AHB-Lite crossbar. Each upstream port connects to a splitter, which routes bus requests toward one of the 3 downstream ports, and routes responses back. Each downstream port connects to an arbiter, which safely manages concurrent access to the port.

The crossbar is built from two components:

- Splitters

- Perform coarse address decode

- Route requests (addresses, write data) to the downstream port indicated by the initial address decode

- Route responses (read data, bus errors) from the correct arbiter back to the upstream port

- Arbiters

- Manage concurrent requests to a downstream port

- Route responses (read data, bus errors) to the correct splitter

- Implement bus priority rules

The main crossbar on RP2040 consists of 4 1:10 splitters and 10 4:1 arbiters, with a mesh of 40 AHB-Lite bus channels between them. Note that, as AHB-Lite is a pipelined bus, the splitter may be routing back a response to an earlier request from downstream port A, whilst a new request to downstream port B is already in progress. This does not incur any cycle penalty.

#### 2.1.1.1. Bus Priority

The arbiters in the main AHB-Lite crossbar implement a two-level bus priority scheme. Priority levels are configured permaster, using the BUS\_PRIORITY register in the BUSCTRL register block.

When there are multiple simultaneous accesses to same arbiter, any requests from high-priority masters (priority level 1) will be considered before any requests from low-priority masters (priority 0). If multiple masters of the same priority level attempt to access the same slave simultaneously, a round-robin tie break is applied, i.e. the arbiter grants access to each master in turn.

#### NOTE

Priority arbitration only applies to multiple masters attempting to access the **same** slave on the same cycle. Accesses to different slaves, e.g. different SRAM banks, can proceed simultaneously.

When accessing a slave with zero wait states, such as SRAM (i.e. can be accessed once per system clock cycle), highpriority masters will never observe any slowdown or other timing effects caused by accesses from low-priority masters. This allows *guaranteed* latency and throughput for hard real time use cases; it does however mean a low-priority master may get stalled until there is a free cycle.

#### 2.1.1.2. Bus Performance Counters

The performance counters automatically count accesses to the main AHB-Lite crossbar arbiters. This can assist in diagnosing performance issues, in high-traffic use cases.

There are four performance counters. Each is a 24-bit saturating counter. Counter values can be read from BUSCTRL\_PERFCTRx, and cleared by writing any value to BUSCTRL\_PERFCTRx. Each counter can count one of the 20 available events at a time, as selected by BUSCTRL\_PERFSELx. The available bus events are:

| PERFSEL<br>x | Event                      | Description                                                                                                                                                                            |

|--------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0            | APB access,<br>contested   | Completion of an access to the APB arbiter (which is upstream of all APB peripherals), which was previously delayed due to an access by another master.                                |

| 1            | APB access                 | Completion of an access to the APB arbiter                                                                                                                                             |

| 2            | FASTPERI access, contested | Completion of an access to the FASTPERI arbiter (which is upstream of PIOs, DMA config port, USB, XIP aux FIFO port), which was previously delayed due to an access by another master. |

| 3            | FASTPERI access            | Completion of an access to the FASTPERI arbiter                                                                                                                                        |

| 4            | SRAM5 access,<br>contested | Completion of an access to the SRAM5 arbiter, which was previously delayed due to an access by another master.                                                                         |

| 5            | SRAM5 access               | Completion of an access to the SRAM5 arbiter                                                                                                                                           |

| 6            | SRAM4 access, contested    | Completion of an access to the SRAM4 arbiter, which was previously delayed due to an access by another master.                                                                         |

| 7            | SRAM4 access               | Completion of an access to the SRAM4 arbiter                                                                                                                                           |

| 8            | SRAM3 access, contested    | Completion of an access to the SRAM3 arbiter, which was previously delayed due to an access by another master.                                                                         |

| 9            | SRAM3 access               | Completion of an access to the SRAM3 arbiter                                                                                                                                           |

| 10           | SRAM2 access, contested    | Completion of an access to the SRAM2 arbiter, which was previously delayed due to an access by another master.                                                                         |

| 11           | SRAM2 access               | Completion of an access to the SRAM2 arbiter                                                                                                                                           |

| 12           | SRAM1 access, contested    | Completion of an access to the SRAM1 arbiter, which was previously delayed due to an access by another master.                                                                         |

| 13           | SRAM1 access               | Completion of an access to the SRAM1 arbiter                                                                                                                                           |

| 14           | SRAM0 access,<br>contested | Completion of an access to the SRAM0 arbiter, which was previously delayed due to an access by another master.                                                                         |

| 15           | SRAM0 access               | Completion of an access to the SRAM0 arbiter                                                                                                                                           |

| PERFSEL | Event                      | Description                                                                                                       |

|---------|----------------------------|-------------------------------------------------------------------------------------------------------------------|

| x       |                            |                                                                                                                   |

| 16      | XIP_MAIN access, contested | Completion of an access to the XIP_MAIN arbiter, which was previously delayed due to an access by another master. |

| 17      | XIP_MAIN access            | Completion of an access to the XIP_MAIN arbiter                                                                   |

| 18      | ROM access,<br>contested   | Completion of an access to the ROM arbiter, which was previously delayed due to an access by another master.      |

| 19      | ROM access                 | Completion of an access to the ROM arbiter                                                                        |

### 2.1.2. Atomic Register Access

Each peripheral register block is allocated 4kB of address space, with registers accessed using one of 4 methods, selected by address decode.

- Addr + 0x0000 : normal read write access

- Addr + 0x1000 : atomic XOR on write

- Addr + 0x2000 : atomic bitmask set on write

- Addr + 0x3000 : atomic bitmask clear on write

This allows individual fields of a control register to be modified without performing a read-modify-write sequence in software: instead the changes are posted to the peripheral, and performed in-situ. Without this capability, it is difficult to safely access IO registers when an interrupt service routine is concurrent with code running in the foreground, or when the two processors are running code in parallel.

The four atomic access aliases occupy a total of 16 kB. Most peripherals on RP2040 provide this functionality natively, and atomic writes have the same timing as normal read/write access. Some peripherals (I2C, UART, SPI and SSI) instead have this functionality added using a bus interposer, which translates upstream atomic writes into downstream read-modify-write sequences, at the boundary of the peripheral. This extends the access time by two system clock cycles.

The SIO (Section 2.3.1), a single-cycle IO block attached directly to the cores' IO ports, does **not** support atomic accesses at the bus level, although some individual registers (e.g. GPIO) have set/clear/xor aliases.

## 2.1.3. APB Bridge

The APB bridge interfaces the high-speed main AHB-Lite interconnect to the lower-bandwidth peripherals. Whilst the AHB-Lite fabric offers zero-wait-state access everywhere, APB accesses have a cycle penalty:

- APB bus accesses take two cycles minimum (setup phase and access phase)

- The bridge adds an additional cycle to read accesses, as the bus request and response are registered

- The bridge adds two additional cycles to write accesses, as the APB setup phase can not begin until the AHB-Lite write data is valid

As a result, the throughput of the APB portion of the bus fabric is somewhat lower than the AHB-Lite portion. However, there is more than sufficient bandwidth to saturate the APB serial peripherals.

## 2.1.4. Narrow IO Register Writes

Memory-mapped IO registers on RP2040 ignore the width of bus read/write accesses. They treat all writes as though they were 32 bits in size. This means software can not use byte or halfword writes to modify part of an IO register: any write to an address where the 30 address MSBs match the register address will affect the contents of the entire register. To update part of an IO register, without a read-modify-write sequence, the best solution on RP2040 is atomic set/clear/XOR (see Section 2.1.2). Note that this is more flexible than byte or halfword writes, as any combination of fields can be updated in one operation.

Upon a 8-bit or 16-bit write (such as a strb instruction on the Cortex-M0+), an IO register will sample the entire 32-bit write databus. The Cortex-M0+ and DMA on RP2040 will always replicate narrow data across the bus:

Pico Examples: https://github.com/raspberrypi/pico-examples/tree/master/system/narrow\_io\_write.or Lines 19-60

```

19 int main() {

20

stdio_init_all();

21

22

// We'll use WATCHDOG_SCRATCH0 as a convenient 32 bit read/write register

23

// that we can assign arbitrary values to

io_rw_32 *scratch32 = &watchdog_hw->scratch[0];

24

// Alias the scratch register as two halfwords at offsets +0x0 and +0x2 \,

25

volatile uint16_t *scratch16 = (volatile uint16_t *) scratch32;

26

// Alias the scratch register as four bytes at offsets +0x0, +0x1, +0x2, +0x3:

27

volatile uint8_t *scratch8 = (volatile uint8_t *) scratch32;

28

29

30

// Show that we can read/write the scratch register as normal:

printf("Writing 32 bit value\n");

31

*scratch32 = 0xdeadbeef;

32

33

printf("Should be 0xdeadbeef: 0x%08x\n", *scratch32);

34

35

// We can do narrow reads just fine -- IO registers treat this as a 32 bit

36

// read, and the processor/DMA will pick out the correct byte lanes based

37

// on transfer size and address LSBs

printf("\nReading back 1 byte at a time\n");

38

39

// Little-endian!

40

printf("Should be ef be ad de: %02x %02x %02x \n",

41

scratch8[0], scratch8[1], scratch8[2], scratch8[3]);

42

43

// The Cortex-M0+ and the RP2040 DMA replicate byte writes across the bus,

44

// and IO registers will sample the entire write bus always.

45

printf("\nWriting 8 bit value 0xa5 at offset 0\n");

46

scratch8[0] = 0xa5;

// Read back the whole scratch register in one go

47

48

printf("Should be 0xa5a5a5a5: 0x%08x\n", *scratch32);

49

// The IO register ignores the address LSBs [1:0] as well as the transfer

50

51

// size, so it doesn't matter what byte offset we use

52

printf("\nWriting 8 bit value at offset 1\n");

53

scratch8[1] = 0x3c;

printf("Should be 0x3c3c3c3c: 0x%08x\n", *scratch32);

54

55

56

// Halfword writes are also replicated across the write data bus

57

printf("\nWriting 16 bit value at offset 0\n");

58

scratch16[0] = 0xf00d;

printf("Should be 0xf00df00d: 0x%08x\n", *scratch32);

59

60 }

```

## 2.1.5. List of Registers

The Bus Fabric registers start at a base address of 0x40030000 (defined as BUSCTRL\_BASE in SDK).

| Table 4. List of<br>BUSCTRL registers | Offset | Name         | Info                                                 |

|---------------------------------------|--------|--------------|------------------------------------------------------|

| 5                                     | 0x00   | BUS_PRIORITY | Set the priority of each master for bus arbitration. |

| Offset | Name             | Info                                             |

|--------|------------------|--------------------------------------------------|

| 0x04   | BUS_PRIORITY_ACK | Bus priority acknowledge                         |

| 0x08   | PERFCTR0         | Bus fabric performance counter 0                 |

| 0x0c   | PERFSEL0         | Bus fabric performance event select for PERFCTR0 |

| 0x10   | PERFCTR1         | Bus fabric performance counter 1                 |

| 0x14   | PERFSEL1         | Bus fabric performance event select for PERFCTR1 |

| 0x18   | PERFCTR2         | Bus fabric performance counter 2                 |

| 0x1c   | PERFSEL2         | Bus fabric performance event select for PERFCTR2 |

| 0x20   | PERFCTR3         | Bus fabric performance counter 3                 |

| 0x24   | PERFSEL3         | Bus fabric performance event select for PERFCTR3 |

## **BUSCTRL: BUS\_PRIORITY Register**

Offset: 0x00

#### Description

Set the priority of each master for bus arbitration.

Table 5. BUS\_PRIORITY Register

| Bits  | Name      | Description                         | Туре | Reset |

|-------|-----------|-------------------------------------|------|-------|

| 31:13 | Reserved. | -                                   | -    | -     |

| 12    | DMA_W     | 0 - low priority, 1 - high priority | RW   | 0x0   |

| 11:9  | Reserved. | -                                   | -    | -     |

| 8     | DMA_R     | 0 - low priority, 1 - high priority | RW   | 0x0   |

| 7:5   | Reserved. | -                                   | -    | -     |

| 4     | PROC1     | 0 - low priority, 1 - high priority | RW   | 0x0   |

| 3:1   | Reserved. | -                                   | -    | -     |

| 0     | PROC0     | 0 - low priority, 1 - high priority | RW   | 0x0   |

## **BUSCTRL: BUS\_PRIORITY\_ACK Register**

Offset: 0x04

#### Description

Bus priority acknowledge

Table 6. BUS\_PRIORITY\_ACK Register

| Bits | Description                                                                                                                                                                                                                    | Туре | Reset |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| 31:1 | Reserved.                                                                                                                                                                                                                      | -    | -     |

| 0    | Goes to 1 once all arbiters have registered the new global priority levels.<br>Arbiters update their local priority when servicing a new nonsequential access.<br>In normal circumstances this will happen almost immediately. | RO   | 0x0   |

## **BUSCTRL: PERFCTR0 Register**

Offset: 0x08

#### Description

Bus fabric performance counter 0

Table 7. PERFCTR0 Register

| Bits  | Description                                                                                                                                                             | Туре | Reset    |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|

| 31:24 | Reserved.                                                                                                                                                               | -    | -        |

| 23:0  | Busfabric saturating performance counter 0<br>Count some event signal from the busfabric arbiters.<br>Write any value to clear. Select an event to count using PERFSEL0 | WC   | 0x000000 |

## **BUSCTRL: PERFSEL0 Register**

#### Offset: 0x0c

#### Description

Bus fabric performance event select for PERFCTR0

#### Table 8. PERFSEL0 Register

| Bits | Description                                                           | Туре | Reset |

|------|-----------------------------------------------------------------------|------|-------|

| 31:5 | Reserved.                                                             | -    | -     |

| 4:0  | Select an event for PERFCTR0. Count either contested accesses, or all | RW   | 0x1f  |

|      | accesses, on a downstream port of the main crossbar.                  |      |       |

|      | $0x00 \rightarrow apb\_contested$                                     |      |       |

|      | $0x01 \rightarrow apb$                                                |      |       |

|      | $0x02 \rightarrow fastperi_contested$                                 |      |       |

|      | 0x03 → fastperi                                                       |      |       |

|      | $0x04 \rightarrow sram5\_contested$                                   |      |       |

|      | $0x05 \rightarrow sram5$                                              |      |       |

|      | $0x06 \rightarrow sram4\_contested$                                   |      |       |

|      | $0x07 \rightarrow sram4$                                              |      |       |

|      | $0x08 \rightarrow sram3\_contested$                                   |      |       |

|      | $0x09 \rightarrow sram3$                                              |      |       |

|      | $0x0a \rightarrow sram2\_contested$                                   |      |       |

|      | $0x0b \rightarrow sram2$                                              |      |       |

|      | $0x0c \rightarrow sram1_contested$                                    |      |       |

|      | $0x0d \rightarrow sram1$                                              |      |       |

|      | $0x0e \rightarrow sram0\_contested$                                   |      |       |

|      | $0x0f \rightarrow sram0$                                              |      |       |

|      | $0x10 \rightarrow xip\_main\_contested$                               |      |       |

|      | $0x11 \rightarrow xip_main$                                           |      |       |

|      | $0x12 \rightarrow rom\_contested$                                     |      |       |

|      | 0x13 → rom                                                            |      |       |

## **BUSCTRL: PERFCTR1 Register**

#### Offset: 0x10

#### Description

Bus fabric performance counter 1

#### Table 9. PERFCTR1 Register

| Bits  | Description                                                                                                                                                             | Туре | Reset    |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|

| 31:24 | Reserved.                                                                                                                                                               | -    | -        |

| 23:0  | Busfabric saturating performance counter 1<br>Count some event signal from the busfabric arbiters.<br>Write any value to clear. Select an event to count using PERFSEL1 | WC   | 0x000000 |

## **BUSCTRL: PERFSEL1 Register**

#### Offset: 0x14

#### Description

Bus fabric performance event select for PERFCTR1

#### Table 10. PERFSEL1 Register

| Bits | Description                                                           | Туре | Reset |

|------|-----------------------------------------------------------------------|------|-------|

| 31:5 | Reserved.                                                             | -    | -     |

| 4:0  | Select an event for PERFCTR1. Count either contested accesses, or all | RW   | 0x1f  |

|      | accesses, on a downstream port of the main crossbar.                  |      |       |

|      | $0x00 \rightarrow apb\_contested$                                     |      |       |

|      | $0x01 \rightarrow apb$                                                |      |       |

|      | $0x02 \rightarrow fastperi_contested$                                 |      |       |

|      | 0x03 → fastperi                                                       |      |       |

|      | $0x04 \rightarrow sram5\_contested$                                   |      |       |

|      | $0x05 \rightarrow sram5$                                              |      |       |

|      | $0x06 \rightarrow sram4\_contested$                                   |      |       |

|      | $0x07 \rightarrow sram4$                                              |      |       |

|      | $0x08 \rightarrow sram3\_contested$                                   |      |       |

|      | $0x09 \rightarrow sram3$                                              |      |       |

|      | $0x0a \rightarrow sram2\_contested$                                   |      |       |

|      | $0x0b \rightarrow sram2$                                              |      |       |

|      | $0x0c \rightarrow sram1\_contested$                                   |      |       |

|      | $0x0d \rightarrow sram1$                                              |      |       |

|      | $0x0e \rightarrow sram0\_contested$                                   |      |       |

|      | $0x0f \rightarrow sram0$                                              |      |       |

|      | $0x10 \rightarrow xip\_main\_contested$                               |      |       |

|      | $0x11 \rightarrow xip_main$                                           |      |       |

|      | $0x12 \rightarrow rom\_contested$                                     |      |       |

|      | $0x13 \rightarrow rom$                                                |      |       |

## **BUSCTRL: PERFCTR2 Register**

#### Offset: 0x18

#### Description

Bus fabric performance counter 2

#### Table 11. PERFCTR2 Register

| Bits  | Description                                                                                                                                                             | Туре | Reset    |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|

| 31:24 | Reserved.                                                                                                                                                               | -    | -        |

| 23:0  | Busfabric saturating performance counter 2<br>Count some event signal from the busfabric arbiters.<br>Write any value to clear. Select an event to count using PERFSEL2 | WC   | 0x000000 |

## **BUSCTRL: PERFSEL2 Register**

Offset: 0x1c

#### Description

Bus fabric performance event select for PERFCTR2

#### Table 12. PERFSEL2 Register

| Bits | Description                                                           | Туре | Reset |

|------|-----------------------------------------------------------------------|------|-------|

| 31:5 | Reserved.                                                             | -    | -     |

| 4:0  | Select an event for PERFCTR2. Count either contested accesses, or all | RW   | 0x1f  |

|      | accesses, on a downstream port of the main crossbar.                  |      |       |

|      | $0x00 \rightarrow apb\_contested$                                     |      |       |

|      | 0x01 → apb                                                            |      |       |

|      | $0x02 \rightarrow fastperi_contested$                                 |      |       |

|      | 0x03 → fastperi                                                       |      |       |

|      | $0x04 \rightarrow sram5\_contested$                                   |      |       |

|      | $0x05 \rightarrow sram5$                                              |      |       |

|      | $0x06 \rightarrow sram4\_contested$                                   |      |       |

|      | $0x07 \rightarrow sram4$                                              |      |       |

|      | $0x08 \rightarrow sram3\_contested$                                   |      |       |

|      | $0x09 \rightarrow sram3$                                              |      |       |

|      | $0x0a \rightarrow sram2\_contested$                                   |      |       |

|      | $0x0b \rightarrow sram2$                                              |      |       |

|      | $0x0c \rightarrow sram1_contested$                                    |      |       |

|      | $0x0d \rightarrow sram1$                                              |      |       |

|      | $0x0e \rightarrow sram0\_contested$                                   |      |       |

|      | $0x0f \rightarrow sram0$                                              |      |       |

|      | $0x10 \rightarrow xip\_main\_contested$                               |      |       |

|      | $0x11 \rightarrow xip_main$                                           |      |       |

|      | $0x12 \rightarrow rom\_contested$                                     |      |       |

|      | 0x13 → rom                                                            |      |       |

## **BUSCTRL: PERFCTR3 Register**

Offset: 0x20

#### Description

Bus fabric performance counter 3

#### Table 13. PERFCTR3 Register

| Bits  | Description                                                                                                                                                             | Туре | Reset    |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|

| 31:24 | Reserved.                                                                                                                                                               | -    | -        |

| 23:0  | Busfabric saturating performance counter 3<br>Count some event signal from the busfabric arbiters.<br>Write any value to clear. Select an event to count using PERFSEL3 | WC   | 0x000000 |

## **BUSCTRL: PERFSEL3 Register**

#### Offset: 0x24

#### Description

Bus fabric performance event select for PERFCTR3

#### Table 14. PERFSEL3 Register

| Bits | Description                                                           | Туре | Reset |

|------|-----------------------------------------------------------------------|------|-------|

| 31:5 | Reserved.                                                             | -    | -     |

| 4:0  | Select an event for PERFCTR3. Count either contested accesses, or all | RW   | 0x1f  |

|      | accesses, on a downstream port of the main crossbar.                  |      |       |

|      | $0x00 \rightarrow apb\_contested$                                     |      |       |

|      | 0x01 → apb                                                            |      |       |

|      | $0x02 \rightarrow fastperi\_contested$                                |      |       |

|      | 0x03 → fastperi                                                       |      |       |

|      | $0x04 \rightarrow sram5\_contested$                                   |      |       |

|      | $0x05 \rightarrow sram5$                                              |      |       |

|      | $0x06 \rightarrow sram4\_contested$                                   |      |       |

|      | $0x07 \rightarrow sram4$                                              |      |       |

|      | $0x08 \rightarrow sram3\_contested$                                   |      |       |

|      | 0x09 → sram3                                                          |      |       |

|      | $0x0a \rightarrow sram2\_contested$                                   |      |       |

|      | $0x0b \rightarrow sram2$                                              |      |       |

|      | $0x0c \rightarrow sram1_contested$                                    |      |       |

|      | 0x0d → sram1                                                          |      |       |

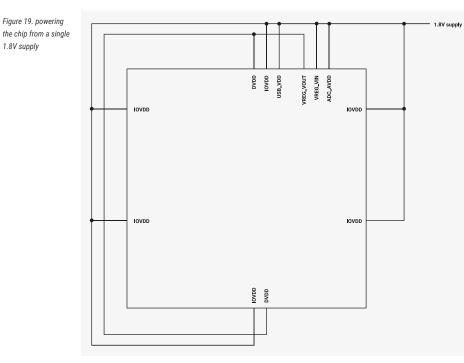

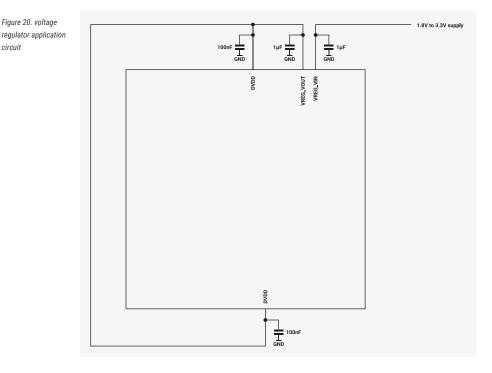

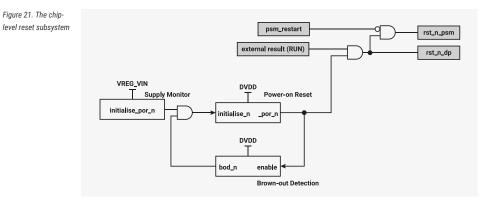

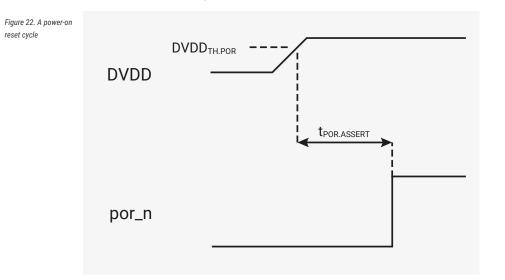

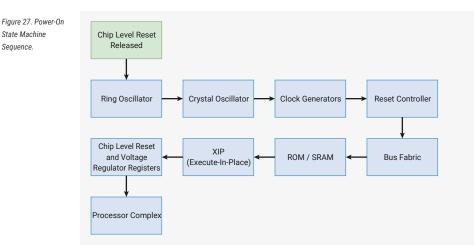

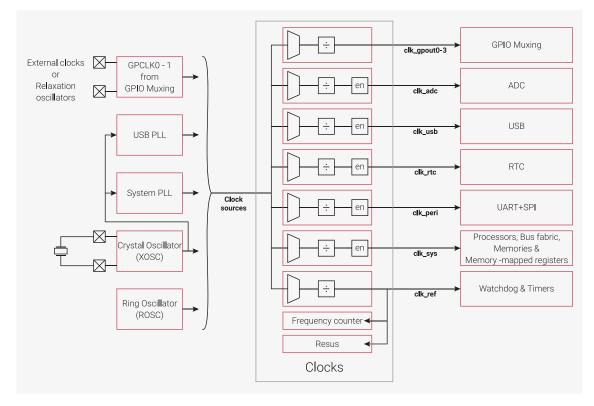

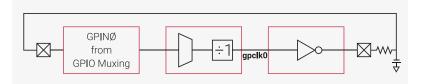

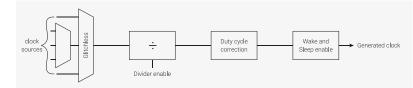

|      | $0x0e \rightarrow sram0\_contested$                                   |      |       |