# AT6558 BDS/GNSS Full Constellation SOC Chip Data Sheet

**Version** : **1.14**

www.icofchina.com

|                                                                             | Title  | AT6558 BDS/GNSS Full Constellation |  |  |  |  |

|-----------------------------------------------------------------------------|--------|------------------------------------|--|--|--|--|

|                                                                             |        | SOC Chip                           |  |  |  |  |

|                                                                             | Туре   | Data sheet                         |  |  |  |  |

|                                                                             | Number |                                    |  |  |  |  |

| Hangzhou ZhongKe Microelectro                                               |        |                                    |  |  |  |  |

| nics CO.,Ltd                                                                |        |                                    |  |  |  |  |

| Document summary                                                            |        |                                    |  |  |  |  |

| This manual provides the functional characteristics of the AT6558, the chip |        |                                    |  |  |  |  |

| overview and introduction.                                                  |        |                                    |  |  |  |  |

## Directory

| Directory 3                                  |

|----------------------------------------------|

| 1 Summary 6                                  |

| 1.1 Chip Introduction6                       |

| <b>1.2</b> Function Combination Table        |

| 1.3 Main Features 7                          |

| 1.4 Performance Indicators                   |

| <b>1.5</b> Chip Application                  |

| 2 Pin Description                            |

| 2.1 Pin Arrangement                          |

| 2.2 Pin Description                          |

| 3 Chip Architecture 13                       |

| 3.1 Chip Block Diagram 13                    |

| 3.2 Power Management 14                      |

| 3.2.1 Low Power Supply Connection Scheme     |

| 3.2.2 External PMU Power Connection Scheme   |

| 3.2.3 Backup Power Supply 15                 |

| 3.2.4 Working Mode 16                        |

| 3.3 Chip Reset 17                            |

| 4 RF Front-End 18                            |

| 4.1 RF Front-end Architecture 18             |

| 4.2 Active Antenna Detection                 |

| 5 Baseband Processor 19                      |

| 5.1 Multi System Satellite Processing Engine |

| <b>5.2</b> RTC Backup Area <b>19</b>         |

| 5.3 Timer 19                                 |

| 5.4 DMA Controller 19                        |

| 5.5 Watchdog 19                              |

| 5.6 UART 20                                    |

|------------------------------------------------|

| 5.7 SPI                                        |

| 5.8 I2C 20                                     |

| 6 Electrical Characteristics 21                |

| 6.1 Limit Characteristics 21                   |

| 6.2 DC Characteristics 21                      |

| 6.3 Simulation Related Characteristics         |

| 6.4 RF Related Characteristics 23              |

| 6.5 Satellite System Model 23                  |

| 7 Interface Properties 25                      |

| 7.1 RS232 Interface Timing 25                  |

| 7.2 SPI Interface Timing 25                    |

| 7.3 SWD Interface Timing 26                    |

| 8 Chip Package 27                              |

| 8.1 Chip Identification Rules 27               |

| 8.2 Package Specification 28                   |

| 9 Reference Design 29                          |

| 9.1 Reference Scheme                           |

| 9.2 Device Selection 31                        |

| 10 Application Solutions 33                    |

| 10.1 Active Antenna Feed and Detection         |

| 10.2 RF Input                                  |

| 10.3 Reference Clock Oscillator                |

| 10.4 RTC Clock 34                              |

| 10.5 GPIO 35                                   |

| <b>10.6</b> Low Power Setting                  |

| 10.6.1 Enter Low Power Mode                    |

| 10.6.2 Peripheral Circuit Connection Solutions |

| 10.7 DCDC 39                                   |

|                                                |

Hangzhou ZhongKe Microelectronics CO.,Ltd

| 11 Packaging and Transportation | 40 |

|---------------------------------|----|

| <b>11.1</b> Packaging           | 40 |

| <b>11.2</b> ESD Protection      | 40 |

| 12 Document Update Record       | 40 |

| Contact                         | 42 |

www.icofchina.com

## **1** Summary

#### **1.1** Chip Introduction

AT6558 is a high-performance BDS/GNSS multi-mode satellite navigation receiver SOC single chip, on that integrated RF front-end, digital baseband processor, 32 bit CPU RISC, power management functions.

AT6558 support a variety of satellite navigation systems, including the Chinese BDS (Beidou satellite navigation system), American GPS, Russian GLONASS, EU Galileo, Japanese QZSS and Satellite enhanced system SBAS (WAAS, EGNOS,

GAGAN, MSAS)).AT6558 is a real sixes in one multi-mode satellite navigation and positioning chip, can simultaneously receive GNSS signals of six satellite navigation systems and implement joint positioning, navigation, and timing.

| Туре         | Multi<br>Func |         | Po        | ower       | Inte  | rface | Characteristic |      |                   |                                 |         |              |  |

|--------------|---------------|---------|-----------|------------|-------|-------|----------------|------|-------------------|---------------------------------|---------|--------------|--|

|              | GPS<br>RDS    | GLONASS | 2.7V~3.6V | 1.65V~3.6V | UARTI | UART2 | Flash          | TCXO | Antenna Detection | Antenna Over Current Protection | Pre-SAW | External LNA |  |

| AT6558-5N-1X | •             |         | •         |            | •     | •     | •              | •    | •                 | •                               | •       | •            |  |

| AT6558-5N-2X | •             | 1       | •         |            | •     | •     | •              | •    | •                 | •                               | •       | •            |  |

| AT6558-5N-3X | • •           | 1       | •         |            | •     | •     | •              | •    | •                 | •                               | •       | •            |  |

| AT6558-5N-5X | •             | •       | •         |            | •     | •     | •              | •    | •                 | •                               | •       | •            |  |

| AT6558-5N-7X | • •           | •       | •         |            | •     | •     | •              | •    | •                 | •                               | •       | •            |  |

#### **1.2** Function Combination Table

www.icofchina.com

### **1.3** Main Features

- Functional Specifications

- Support BDS/GPS/GLONASS satellite navigation single system positioning and multiple system joint positioning

- Support QZSS and SBAS system

- Support A-GNSS

- Support D-GNSS differential positioning

- The maximum positioning update rate can reach 10Hz

- High Performance Solutions

- Cold start capture sensitivity: -148dBm

- Tracking sensitivity: 162 dBm

- Low Power

- BDS/GPS dual mode continuous operation: <23mA (@3.3V)

- Standby: <10uA (@3.3V)

- Power Management

- Support 2.7~3.6V power supply, typical 3.3V power supply.

- RTC and backup power supply can be reduced to 1.5V

- Core voltage of 1.2V

- Serial Interface

- 2 independent UART interface

- one I2C interface

- 2 independent SPI interface

- Package and Size

- QFN package, 40 pin, chip size: 5mm×5mm×0.8mm

#### **1.4** Performance Indicators

| Technical        | Indicators                        |

|------------------|-----------------------------------|

| Parameters       |                                   |

| Signal receiving | BDS/GPS/GLONASS/GALILEO/QZSS/SBAS |

www.icofchina.com

| RF channel number     | Three-channel RF, support the full constellation BDS, GPS |

|-----------------------|-----------------------------------------------------------|

|                       | and GLONASS receiving at the same time                    |

| Cold Start TTFF       | ≤32s                                                      |

| Hot start TTFF        | $\leq 1s$                                                 |

| Recapture TTFF        | ≤1s                                                       |

| Cold start capture    | -148dBm                                                   |

| sensitivity           |                                                           |

| Hot start capture     | -156dBm                                                   |

| sensitivity           |                                                           |

| Recapture sensitivity | -160dBm                                                   |

| Tracking sensitivity  | -162dBm                                                   |

| Positioning Precision | <2m ( 1                                                   |

| Speed Measurement     | <0.1m/s ( 10 )                                            |

| Precision             |                                                           |

| Timing Precision      | <30ns ( 1\sigma )                                         |

| Positioning Update    | Maximum 10Hz                                              |

| Rate                  |                                                           |

## **1.5 Chip Application**

- Vehicle positioning and navigation

- Timing

- Wearable Devices

- Portable devices, such as Mobile phone、Tablet PC

## **2** Pin Description

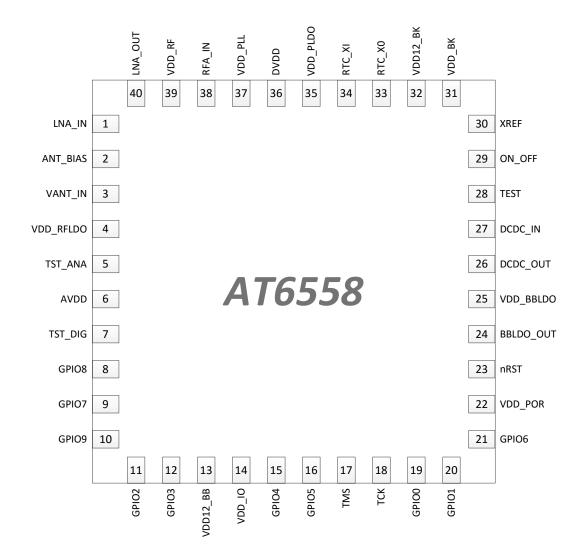

## 2.1 Pin Arrangement

### **2.2** Pin Description

| Numb | Name     | I/O Type  | Function description                        |  |  |  |

|------|----------|-----------|---------------------------------------------|--|--|--|

| er   |          | ro ijpe   |                                             |  |  |  |

| 1    | LNA_IN   | Analog IO | LNA input, the internal has been separated. |  |  |  |

| 2    | ANT BIAS | Analog IO | Active antenna power supply, receiving      |  |  |  |

| 2    | ANI_DIAS | Analog IO | antenna                                     |  |  |  |

www.icofchina.com

Hangzhou ZhongKe Microelectronics CO.,Ltd

| 3        | VANT_IN  | Analog      | Active antenna power supply, max 3.6V            |

|----------|----------|-------------|--------------------------------------------------|

|          |          | power       |                                                  |

| 4        | VDD_RFLD | Analog      | RFLDO power,1.4~1.8V                             |

| -        | 0        | power       |                                                  |

| 5        | TST_ANA  | Analog IO   | Analog test port                                 |

| 6        | AVDD     | Analog      | LDO output,1.2V, 1uF capacitance bypass to       |

| 0        | AVDD     | power       | the ground                                       |

| 7        | TST_DIG  | Analog IO   | Digital test port, the output high level is 1.2V |

|          |          | Digital     | General GPIO, default for speed pulse input 1    |

| 8        | GPIO8    | bidirection |                                                  |

|          |          | al          |                                                  |

|          |          | Digital     | General GPIO, default for vehicle travel         |

| 9        | GPIO7    | bidirection | direction                                        |

|          |          | al          |                                                  |

|          |          | Digital     | General GPIO, default for speed pulse input 2    |

| 10       | GPIO9    | bidirection |                                                  |

|          |          | al          |                                                  |

|          |          | Digital     | General GPIO, default for SCL clock line of      |

| 11       | GPIO2    | bidirection | I2C                                              |

|          |          | al          |                                                  |

|          |          | Digital     | General GPIO, default for SDA data line of I2C   |

| 12       | GPIO3    | bidirection |                                                  |

|          |          | al          |                                                  |

| 10       |          | Digital     | Digital baseband core power supply,1.2V,1uF      |

| 13       | VDD12_BB | power       | capacitance bypass to the ground                 |

|          |          | Digital     |                                                  |

| 14       | VDD_IO   | power       | Digital baseband IO power supply                 |

| 1.7      | CDICA    | Digital     | Generic GPIO, default for TXD send data lines    |

| 15 GPIO4 |          | bidirection | of UART1                                         |

| L        | I        | L           |                                                  |

www.icofchina.com

|    |          | al          |                                                   |  |

|----|----------|-------------|---------------------------------------------------|--|

|    |          | Digital     | Canadia CDIO default for DVD marks 1 t            |  |

| 16 | 16 GPIO5 | bidirection | Generic GPIO, default for RXD receive data        |  |

| 10 | 01105    | al          | lines of UART1                                    |  |

|    |          |             |                                                   |  |

| 17 |          | Digital     |                                                   |  |

| 17 | TMS      | bidirection | SWD debug interface data line                     |  |

|    |          | al          |                                                   |  |

| 18 | TCK      | Digital     | SWD debug interface clock line                    |  |

|    |          | input       |                                                   |  |

|    |          | Digital     | Generic GPIO, default for TXD send data lines     |  |

| 19 | GPIO0    | bidirection | of UART0                                          |  |

|    |          | al          |                                                   |  |

|    |          | Digital     | Generic GPIO, default for RXD receive data        |  |

| 20 | GPIO1    | bidirection | lines of UART0                                    |  |

|    |          | al          |                                                   |  |

|    |          | Digital     | Generic GPIO, default for 1PPS output pulse       |  |

| 21 | GPIO6    | bidirection |                                                   |  |

|    |          | al          |                                                   |  |

|    |          | Analog      | POR power input, battery backup main power        |  |

| 22 | VDD_POR  | power       | supply                                            |  |

| 23 | nRST     | Analog IO   | External reset input, pull-up                     |  |

|    | BBLDO OU | 0           |                                                   |  |

| 24 | –<br>  T | Analog IO   | BBLDO output,1.2V                                 |  |

|    |          | Analog      |                                                   |  |

| 25 | BBLDO_IN | power       | BBLDO input,1.4V~3.6V                             |  |

| 26 | DCDC OUT | -           | DCDC output                                       |  |

| 20 |          | Analog IO   | DCDC output                                       |  |

| 27 | DCDC_IN  | Analog      | DC-DC input                                       |  |

|    |          | power       |                                                   |  |

| 28 | TEST     | Digital     | Chip test mode control, high level enter the test |  |

www.icofchina.com

|    |             | · ,        |                                                |  |  |  |

|----|-------------|------------|------------------------------------------------|--|--|--|

|    |             | input      | mode; drop down (battery backup domain)        |  |  |  |

| 29 | ON OFF      | Digital    | Shutdown control, pull up(battery backup       |  |  |  |

|    |             | input      | domain)                                        |  |  |  |

| 20 | VDEE        |            | Reference frequency input, external TCXO or    |  |  |  |

| 30 | XREF        | Analog IO  | passive crystal                                |  |  |  |

| 21 |             | Analog     |                                                |  |  |  |

| 31 | VDD_BK      | power      | Backup power input,1.5~3.6V                    |  |  |  |

| 32 |             | Analog IO  | Backup LDO output, 1.2V, 1uF capacitance       |  |  |  |

| 32 | VDD12_BK    | Analog IO  | bypass to the ground                           |  |  |  |

| 33 | RTC_XO      | Analog IO  | RTC OSC output                                 |  |  |  |

| 34 | RTC_XI      | Analog IO  | RTC OSC input                                  |  |  |  |

| 25 | 35 VDD_PLDO | Analog     | PLL LDO power,1.4~1.8V                         |  |  |  |

| 35 |             | power      |                                                |  |  |  |

| 26 | DUDD        |            | Phase-locked loop digital power supply, 1.2 V, |  |  |  |

| 36 | DVDD        | Analog IO  | 1uF capacitance bypass to the ground           |  |  |  |

| 27 |             | A state IO | Phase-locked loop analog power supply, 1.2 V,  |  |  |  |

| 37 | VDD_PLL     | Analog IO  | 1uF capacitance bypass to the ground           |  |  |  |

| 38 | RFA_IN      | RF IO      | RFA input, the internal has been separated     |  |  |  |

| 20 |             | Analog IO  | RF power,1.2V,1uF capacitance bypass to the    |  |  |  |

| 39 | VDD_RF      |            | ground                                         |  |  |  |

| 40 | LNA_OUT     | RF IO      | LNA output, the internal has been separated.   |  |  |  |

|    |             | Package    |                                                |  |  |  |

| EP | GND         | bottom     | Public access sites must be well grounded.     |  |  |  |

|    |             | metal      |                                                |  |  |  |

## **3** Chip Architecture

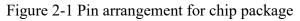

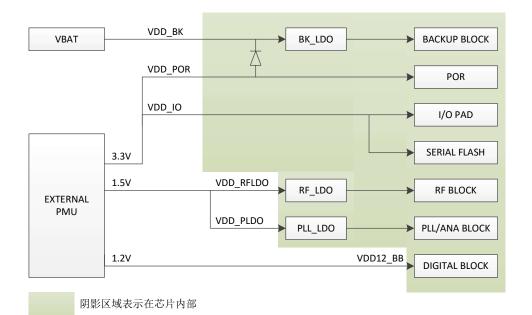

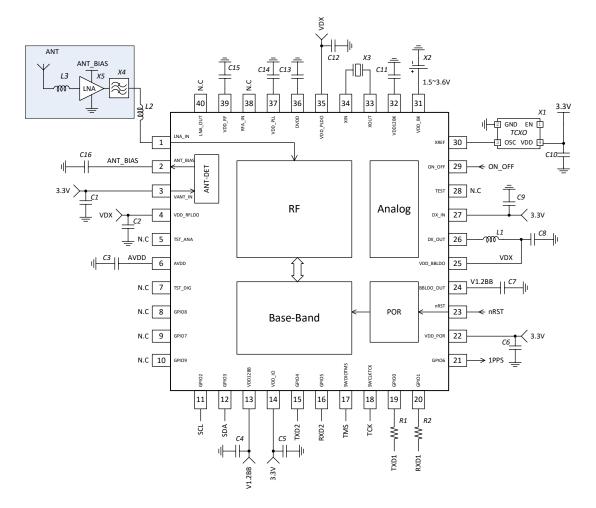

## **3.1** Chip Block Diagram

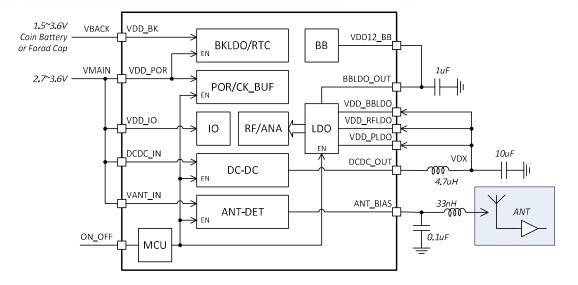

Figure 3-1 AT6558 system block diagram

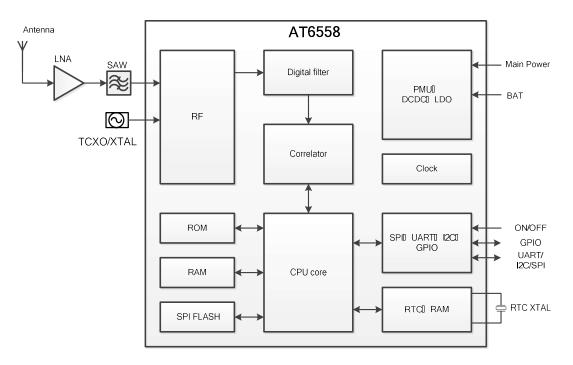

#### **3.2** Power Management

**3.2.1** Low Power Supply Connection Scheme

As shown in Figure 3-2, MAIN POWER provides 3.3 V power supply to the entire chip:

Connected to VDD\_IO and supplied power to IO PAD and FLASH of the chip;

Connected to VDD\_POR and supplied power to internal POR, at the same time, supplied power to backup area through a diode;

Connected to the input end of the DCDC and supplied power to DCDC. Using DCDC output as an internal LDO input, supplied power to the chip RF front-end part, analog and digital part by the internal LDO.

The external button battery is used as a backup power supply (VBAT) to supply power to the backup area of the chip, and the power supply of the backup circuit can be supplied in the case of the main power supply power down.

Figure 3-2 AT6558 power connection scheme (low power consumption scheme)

#### 3.2.2 External PMU Power Connection Scheme

In the case of external PMU, DCDC and BB\_LDO inside the chip can not be used, external PMU provide 3 sets of power supply for each part of the chip power www.icofchina.com Hangzhou ZhongKe Microelectronics CO.,Ltd supply:

As shown in Figure 3-3, external PMU provide 3.3 V power supply ; connected to VDD\_IO and supplied power to IO PAD and FLASH of the chip; connected to VDD\_POR and supplied power to internal POR, at the same time, supply power to the backup area through a diode.

External PMU provide 1.5V power, connected to the RF\_LDO and BB\_LDO inside the chip and supplied power to RF front end and analog part of the chip by the internal LDO.

External PMU provide 1.2V power, connected to VDD12\_BB inside the chip, directly to supply power to the digital part of the chip.

The external button battery is used as a backup power supply (VBAT) to supply power to the backup area of the chip, and can be supplied in the case of the main power supply power down.

Figure 3-3 AT6558 power connection scheme (external PMU scheme)

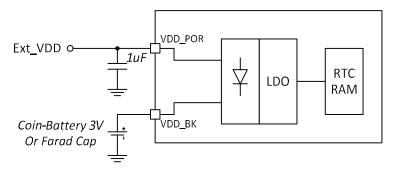

#### 3.2.3 Backup Power Supply

An external rechargeable 3V button battery or Fala capacitor is recommended to provide backup power for RTC and RAM. The built-in trickle charging circuit and www.icofchina.com Hangzhou ZhongKe Microelectronics CO.,Ltd reverse charging circuit and don't need external diode and a current limiting resistor. The maximum charge current is 500uA and the maximum charge voltage is VDD\_POR. Note that the maximum charging voltage of the button cell can reach VDD\_POR-0.3V; if the Fala capacitor is used, the withstand voltage of the capacitor should be paid attention to.

If the system does not require hot start function, the VDD\_BK pin can be left floating. When the VDD\_POR power down, RTC and backup RAM because there is no power supply, will stop working. Positioning information can not be saved and the hot start function will fail.

Figure 3-4 backup power connection diagram

#### 3.2.4 Working Mode

AT6558 has four work modes: full working mode, automatic low power mode, external control low power mode and the battery backup mode.

Full working mode: when all power supply normally and the ON\_OFF pin is high, the chip is in full working mode and the signal receive and calculating normally.

Automatic low power mode: in some applications, it does not need continuous positioning and more focus on low power consumption, at this time the need for timely closure of the chip function in order to save power consumption. In this mode, all the power supply normally, once the chip is working properly and positioning, the internal program will automatically shut down the power consumption module, enter the state of low power consumption and start the timer (RTC timer). The timer will automatically wake up the chip and carry on the next position.

External control low power mode: all the power supply normally and the chip is working properly, the external host will pull down the ON\_OFF pin; Program inside www.icofchina.com Hangzhou ZhongKe Microelectronics CO.,Ltd the chip will automatically save the current state of the circuit, and close the RF circuit and baseband circuit, then enter the state of low power consumption. When the ON\_OFF pin is pulled up, the chip will automatically restore the full working mode (equivalent to a hot start).

Battery backup mode: close all the power except VDD\_BK, the chip will enter the backup mode. At this time, only the minimum current is required to maintain the RTC clock and backup RAM .After the power recovery, the navigation program can recover from the backup RAM in order to achieve a rapid hot start.

| Mode                 | RF           | Baseband | IO/POR       | RTC/ Backup  |

|----------------------|--------------|----------|--------------|--------------|

|                      | Front-end    | kernel   |              | RAM          |

| Full working mode    | $\checkmark$ |          | $\checkmark$ | $\checkmark$ |

| Automatic low power  | ×            | ×        | $\checkmark$ | $\checkmark$ |

| mode                 |              |          |              |              |

| External control low | ×            | ×        | $\checkmark$ | $\checkmark$ |

| power mode           |              |          |              |              |

| Battery backup mode  | ×            | ×        | ×            | $\checkmark$ |

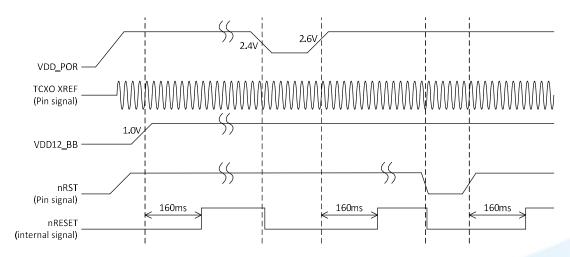

### **3.3** Chip Reset

Chip internal integrated power on reset circuit, and supports external reset from the chip. Reset sequence is as follows:

www.icofchina.com

## **4 RF Front-End**

#### 4.1 RF Front-end Architecture

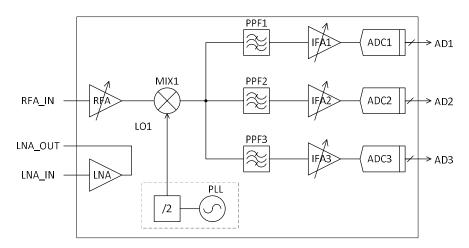

The RF front-end includes three separate receiving channels ,and supports the satellite signal frequency point of the full constellation: BDS B1, GPS L1, Galileo L1, GLONASS L1. Three channels sharing RF front end and PLL, support a variety of reference frequency. Integrated active antenna detection circuit and clock frequency multiplier circuit.ADC sampling frequency can be configured.

Figure 4-1 AT6558 block diagram of RF front end

#### 4.2 Active Antenna Detection

Chip integrated active antenna detection circuit, can be fed to the external active antenna. And according to the size of the feed current, indicating the status of the active antenna. The active antenna detection circuit also provides short circuit protection, and protecting the chip and the active antenna is not damaged by limiting the current fed to the active antenna.

Detection circuit of the active antenna defines three kinds of state, when the current is less than the set value, indicating open antenna; when the current is greater than the set value, indicating a normal antenna; when the current is too large or the short circuit occurs, indicating antenna over current.

www.icofchina.com

## **5** Baseband Processor

#### 5.1 Multi System Satellite Processing Engine

AT6558 integrates the latest multi-system satellite processing engine, supports BDS, GPS, GLONASS, Galileo, QZSS and SBAS system. It can receive the signals of the six systems at the same time and realize the joint positioning. AT6558 can significantly improve the positioning accuracy and positioning availability, especially in the complex environment, such as urban canyons, performance improvement is more significant.

#### **5.2 RTC Backup Area**

Real time clock (RTC) is located in the battery power supply area, and is equipped with a backup RAM. Using independent low power LDO for power supply. RTC can normally work in the case of the disappearance of the main power supply, while ensuring that the data is not lost in the backup RAM.

#### **5.3** Timer

Using three timer circuit with PWM function, the timer interrupt can be used as a processor interrupt input, also can be used as the hardware request source of DMA. The timing cycle can be adjusted according to re-frequency-dividing of the peripheral clock, theoretically up to  $2^{32}$  times of the peripheral cycle.

#### **5.4 DMA Controller**

DMA controller supports one-way transmission of 8 channels, each channel can be independently carried out the following three kinds of data transmission: memory to the peripheral; peripheral to the memory; memory to the memory.

#### 5.5 Watchdog

Watchdog circuit is used for the detection of hardware and software, whether a timeout error has occurred. When there is a timeout signal output, the chip will be reset by the signal. Therefore, the reliability of the chip is guaranteed from the hardware.

### **5.6 UART**

Consists of two independent full duplex UART modules, achieve data conversion between serial and parallel. Baud rate maximum support 256000bps, and have the function of automatic baud rate detection. Each UART has an independent transmit FIFO and receive FIFO, the depth is 32 bytes. UART supports DMA working mode.

#### 5.7 SPI

AT6558 contains a SPI master device interface and a SPI slave device interface. SPI master device interface is used for connecting the SPI interface devices, such as MEMS sensors, FLASH, etc.. SPI slave the device interface can be used as the data interface with the external application processor, the external application processor through the SPI interface to obtain the location information of the chip. Compared to UART, the data transmission speed of SPI is significantly improved.

#### **5.8 I2C**

I2C interface as the master device interface can carry standard transmission (100Kbps) and fast transmission (400Kbps). Support 7bit address or 10bit address mode. Both receiving and sending contain 4 bytes FIFO depth, can be configured for DMA working mode.

## **6 Electrical Characteristics**

### **6.1** Limit Characteristics

| Parameters                                             | Maximum swing | Unit |

|--------------------------------------------------------|---------------|------|

| Voltage referring to earth(analog core power supply,   | -0.3 ~ 1.8    | V    |

| digital core power supply)                             |               |      |

| Voltage referring to earth(digital IO rear drive power | -0.3 ~ 4.1    | V    |

| supply, LDO input power supply)                        |               |      |

| Analog pin voltage                                     | -0.3 ~ 1.8    | V    |

| Other pin voltage                                      | -0.3 ~ 4.1    | V    |

| Maximum RF input power                                 | 5             | dBm  |

| Working Temperature                                    | -40~85        | °C   |

| Junction Temperature                                   | 150           | °C   |

| Storage Temperature                                    | -50~125       | °C   |

## 6.2 DC Characteristics

Power Pin

| Parameters | Minimum value | Typical | Maximum value | Unit |

|------------|---------------|---------|---------------|------|

|            |               | value   |               |      |

| VDD12_BB   | 1.08          | 1.2     | 1.32          | V    |

| VDD12_BK   | 1.08          | 1.2     | 1.32          | V    |

| VDD_IO     | 2.7           | 3.3     | 3.6           | V    |

| VDD_POR    | 2.7           | 3.3     | 3.6           | V    |

| VANT_IN    | 1.8           | 3.3     | 3.6           | V    |

| VDD_BK     | 1.5           | 3.3     | 3.6           | V    |

| VDD_PLDO   | 1.4           | 1.5     | 1.8           | V    |

| VDD_RFLDO  | 1.4           | 1.5     | 1.8           | V    |

| VDD_BBLDO  | 1.4           | 1.5     | 1.8           | V    |

| DCDC_IN    | 2.7           | 3.3     | 3.6           | V    |

| DCDC_OUT   | 1.4           | 1.5     | 1.75          | V    |

| AVDD       | 1.14          | 1.2     | 1.26          | V    |

| DVDD       | 1.14          | 1.2     | 1.26          | V    |

| VDD_RF     | 1.14          | 1.2     | 1.26          | V    |

| VDD_PLL    | 1.14          | 1.2     | 1.26          | V    |

| BBLDO_OUT  | 1.14          | 1.2     | 1.26          | V    |

### Digital IO Pin

www.icofchina.com

| Parameters  | Instruction        | Minimum    | Typical | Maximum    | Unit |

|-------------|--------------------|------------|---------|------------|------|

| 1 arameters |                    | value      | value   | value      |      |

| Ileak       | Leak current input |            | <1      |            | uA   |

|             | pin                |            | _       |            |      |

| Vil         | Low level input    | -0.3       | 0       | VDD IO*0.2 | V    |

| V 11        | voltage            | -0.5       | 0       |            | v    |

| Vih         | High level input   | VDD IO*0.8 |         | VDD IO+0.3 | v    |

|             | voltage            | VDD_10*0.8 |         | VDD_IO+0.3 | v    |

| Vol         | Low level output   |            | 0       | 0.4        | V    |

|             | voltage            |            | 0       | 0.4        | v    |

| Voh         | High level output  | VDD IO-0.4 |         |            | V    |

|             | voltage            | VDD_10-0.4 |         |            | v    |

| Rpu         | Pull up resistor   |            | 40      |            | kΩ   |

| Rpd         | Pull down resistor |            | 40      |            | kΩ   |

### **6.3** Simulation Related Characteristics

|     |                                                                      |                                   | Pa      | rameter In | dex     |      |

|-----|----------------------------------------------------------------------|-----------------------------------|---------|------------|---------|------|

| NO. | Parameters                                                           | Condition                         | Minimum | Typical    | Maximum | Unit |

|     |                                                                      |                                   | value   | value      | value   |      |

| 1   | Reset voltage                                                        |                                   | 2.35    | 2.45       | 2.6     | V    |

| 2   | Reset time <sup>[1]</sup>                                            | crystal<br>frequency<br>26.000MHz |         | 160        |         | ms   |

| 3   | TCXO crystal frequency <sup>[2]</sup>                                |                                   |         | 26.000     |         | MHz  |

| 4   | TCXO amplitude                                                       |                                   | 0.5     | 1.5        | 3.6     | Vpp  |

| 5   | Crystal frequency <sup>[2]</sup>                                     |                                   | 10      | 26.000     | 32      | MHz  |

| 6   | Crystal equivalent series resistance <i>Rs</i>                       |                                   |         |            | 80      | Ω    |

| 7   | Active antenna detection current <sup>[3]</sup>                      |                                   | 2.4     | 3          | 3.6     | mA   |

| 8   | Active antenna<br>short-circuit<br>protection current <sup>[4]</sup> |                                   | 45      | 50         | 60      | mA   |

| 9   | Antenna detection circuit voltage drop                               | Input 50mA,<br>3.3V load          |         |            | 0.3     | V    |

| 10  | Working current                                                      | @3.3V<br>BD+GPS                   |         | 23         |         | mA   |

| 11  | Battery backup<br>current                                            |                                   |         | 10         | 40      | uA   |

www.icofchina.com

| 12 | RTC<br>frequency                          | Crystal           |  | 32.768 |    | kHz |

|----|-------------------------------------------|-------------------|--|--------|----|-----|

| 13 | RTC<br>equivalent<br>resistance <i>Rs</i> | Crystal<br>series |  |        | 80 | KΩ  |

[1] Reset time is related to the crystal frequency. When the frequency is 16.369MHz, the reset time is 250mS, and the frequency is 26 MHz, the reset time is 160 mS.

[2] Chip use the 26.000MHz frequency TCXO by default. Other frequencies as well as passive crystal need to customize the program.

[3][4]Active antenna detection current and short circuit protection current can be configured.

|     |                                  |           | Pa      | arameter Inc | lex     |      |

|-----|----------------------------------|-----------|---------|--------------|---------|------|

| NO. | Parameters                       | Condition | Minimum | Typical      | Maximum | Unit |

|     |                                  |           | value   | value        | value   |      |

|     |                                  | GPS       |         | 1575.42      |         | MHz  |

| 1   | Input fraguanay E                | Galileo   |         | 1575.42      |         | MHz  |

|     | Input frequency $F_{in}$         | BD        |         | 1561.098     |         | MHz  |

|     |                                  | GLONASS   | 1597.78 | 1602         | 1605.66 | MHz  |

| 2   | Input signal level $P_{IN}$      |           | -110    |              | -65     | dBm  |

| 3   | Input reflection coefficient S11 |           |         |              | -10     | dB   |

| 4   | Noise figure NF                  |           |         | 2.5          |         | dB   |

| 5   | 1dB compression<br>point         |           |         | -75          |         | dBm  |

| 6   | Image rejection ratio            |           | 16      | 26           |         | dB   |

| 7   | Lock time of phase locked loop   |           |         |              | 100     | us   |

| 8   | AGC stable time                  |           |         |              | 100     | us   |

**6.4** RF Related Characteristics

### **6.5** Satellite System Model

Chip provides a combination of multiple satellite system model, as follows. Considering the bandwidth, group delay and RF port matching, etc., please choose the www.icofchina.com Hangzhou ZhongKe Microelectronics CO.,Ltd

#### appropriate SAW filter and antenna..

| Model | GPS | BD | GLONASS |

|-------|-----|----|---------|

| 1     | •   |    |         |

| 2     |     | •  |         |

| 3     |     |    | •       |

| 4     | •   | •  |         |

| 5     | •   |    | •       |

| 6     |     | •  | •       |

| 7     | •   | •  | •       |

## **7 Interface Properties**

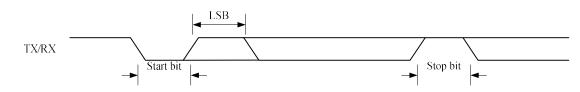

### 7.1 RS232 Interface Timing

Figure 7-1 RS-232 interface timing diagram

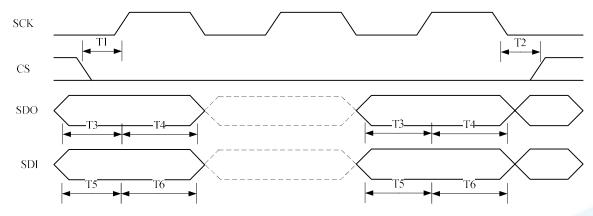

#### 7.2 SPI Interface Timing

| Description            | Label | Minimum   | Maximum   | Unit |

|------------------------|-------|-----------|-----------|------|

| CS establishment time  | T1    | 0.5T      | -         | ns   |

| CS hold time           | T2    | 0.5T      | -         | ns   |

| SDO establishment time | Т3    | 0.5T - 3t | 0.5T - 2t | ns   |

| SDO hold time          | T4    | 0.5T + 2t | 0.5T + 3t | ns   |

| SDI establishment time | T5    | 3t        | -         | ns   |

| SDI hold time          | Т6    | 10        | -         | ns   |

Note1:T represents SCK time cycle, configurable range is (SPICLK/2) MHz  $\sim$

( SPICLK/4096 ) MHz.

Note2: t represents SPICLK time cycle, can be a high-speed bus clock or peripheral clock.

www.icofchina.com

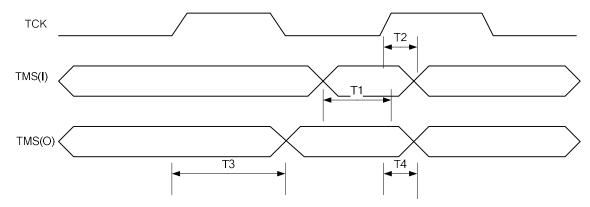

## 7.3 SWD Interface Timing

| Description                               | Label | Minimum | Maximum | Unit |

|-------------------------------------------|-------|---------|---------|------|

| The establishment time of the TMS (I)     | T1    | 0.35T   | -       | ns   |

| input to the TCK rising edge              |       |         |         |      |

| The hold time of the TMS (I) input to the | T2    | 0.15T   | -       | ns   |

| TCK rising edge                           |       |         |         |      |

| The data valid time of the TCK rising     | Т3    | -       | 0.5T    | ns   |

| edge to TMS (O) data                      |       |         |         |      |

| The hold time of the TCK rising edge to   | T4    | 0       | -       | ns   |

| TMS (O)                                   |       |         |         |      |

Note: T represents the cycle of the JTAG interface TCK, the maximum is 50MHz.

Figure 7-3 SWD interface timing diagram

## 8 Chip Package

## **8.1** Chip Identification Rules

| Code       | Instruction        |

|------------|--------------------|

| AT6558     | Chip model         |

| LLLLLLLLLL | Chip serial number |

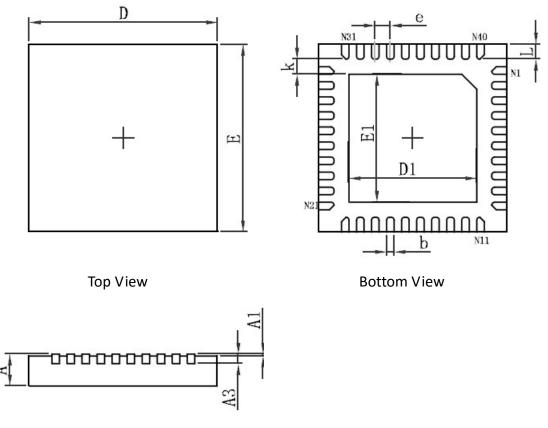

## 8.2 Package Specification

The chip is packaged in the form of QFN5 \* 5-40L (P0.4T0.8), the following is the size of the package.

Side View

Package Size

| Sumbol | Dimensions In Millimeters |             | Dimension   | s In Inches |

|--------|---------------------------|-------------|-------------|-------------|

| Symbol | Min.                      | Max.        | Min.        | Max.        |

| A      | 0.700/0.800               | 0.800/0.900 | 0.028/0.031 | 0.031/0.035 |

| A1     | 0.000                     | 0.050       | 0.000       | 0.002       |

| A3     | 0.203                     | REF.        | 800.0       | REF.        |

| D      | 4.924                     | 5.076       | 0.194       | 0.200       |

| E      | 4.924                     | 5.076       | 0.194       | 0.200       |

| D1     | 3.300                     | 3.500       | 0.130       | 0.138       |

| E1     | 3.300                     | 3.500       | 0.130       | 0.138       |

| k      | 0.200                     | DMIN.       | 0.008       | 3MIN.       |

| b      | 0.150                     | 0.250       | 0.006       | 0.010       |

| е      | 0.400TYP.                 |             | 0.016       | STYP.       |

| L      | 0.324                     | 0.476       | 0.013       | 0.019       |

www.icofchina.com

## **9 Reference Design**

#### **9.1** Reference Scheme

Figure 9-2 passive antenna scheme

The scheme adopts the passive or active antenna, the total gain outside the chip is more than 18dB, less than 35dB. The LNA of an active antenna or a passive antenna is powered by ANT\_BIAS. Note that LNA\_IN DC voltage is less than 1.2 V. If the antenna unit circuit output is DC, before the inductor L2 must add a 470pF blocking capacitor. Positioning information through the serial port output, the default output port is the UART1, corresponding to TXD1/RXD1. Material list: device selection please refer to "AT6558 main peripheral components BOM table"

| Number            | Optional                                  |

|-------------------|-------------------------------------------|

|                   |                                           |

| www.icofchina.com | Hangzhou ZhongKe Microelectronics CO.,Ltd |

| C1, C2, C4, C5, C6, C9, | 0.1uF±5% Chip capacitor                           |

|-------------------------|---------------------------------------------------|

| C10, C12, C17           |                                                   |

| C3、C7、C11、C13、C14、      | 1uF±5% Chip capacitor                             |

| C16                     |                                                   |

| C8                      | 10uF±5% Chip capacitor                            |

| C15                     | 470pF±5% Chip capacitor, Used as a DC-block       |

| R1, R2                  | 10k Ohm±5% Chip resistor                          |

| L1                      | 4.7uH±10% Chip inductor                           |

| L2                      | 4.3 nH±5% High frequency chip inductor            |

| L3                      | 5% High frequency chip inductor                   |

|                         | According to the LNA input impedance matching     |

|                         | fixed value                                       |

| X1                      | TCXO Crystals, Recommend 0.5ppm                   |

| X2                      | 3V rechargeable button battery or super capacitor |

| X3                      | RTC Crystals, 32.768kHz                           |

| X4                      | SAW Filter                                        |

| X5                      | External LNA                                      |

### **9.2** Device Selection

| Device name    | Parameters | Package | Specifications                                           | Manufactor | Model              |  |  |

|----------------|------------|---------|----------------------------------------------------------|------------|--------------------|--|--|

| DC/DC Power    | 4.7uH      | 0603    | 1209/ 620-                                               | SAMSUNG    | CIG10W4R7MNC       |  |  |

| Inductors      |            |         | ±20%,620mA,0.5Ω                                          | MURATA     | LQM18PN4R7MFR      |  |  |

|                | 4.3nH      | 0402    | $\pm 0.2$ nH,750mA,0.07 $\Omega$                         |            | LQW15AN4N3C00D     |  |  |

|                |            |         | ±0.3nH,300mA,0.21Ω                                       |            | LQG15HN4N3S02      |  |  |

| High Frequency | 6.8nH      |         | ±3%,570mA,0.13Ω                                          | MURATA     | LQW15AN6N8H00D     |  |  |

| Inductors      | 0.8nH      |         | ±5%,300mA,0.29Ω                                          | MUKAIA     | LQG15HN6N8J02      |  |  |

|                | 22II       |         | ±3%,260mA,0.63Ω                                          |            | LQW15AN33NH00D     |  |  |

|                | 33nH       |         | ±5%,200mA,0.67Ω                                          |            | LQG15HN33NJ02      |  |  |

| DTC Createle   | 32.768K    | SMD3215 | 20ppm,CL=12.5pF                                          | EPSON      | FC-135             |  |  |

| RTC Crystals   |            |         |                                                          | KDS        | DST310S            |  |  |

|                |            | SMD2520 | 3.3V,<br>0.5ppm@-30°Cto +85°C<br>or 0.5ppm@-40°Cto +85°C | EPSON      | TG-5035CG          |  |  |

|                |            |         |                                                          |            | TG-5006CG          |  |  |

|                |            |         |                                                          | KDS        | DSB221SDN          |  |  |

| TCXO Crystals  | 26M SM     |         |                                                          | KYOCERA    | KT2520K26000ACW33T |  |  |

|                |            |         |                                                          | NDK        | NT2520SB           |  |  |

|                |            |         |                                                          | TXC        | 7L26003            |  |  |

|                |            |         |                                                          | SIWARD     | STO-2520A          |  |  |

| Low Noise      | LNA        | 6UDFN   | Gain=21.5dB,NF=0.8dB                                     | Hangzhou   |                    |  |  |

|                |            |         |                                                          |            | AT2659             |  |  |

| Amplifier      |            |         |                                                          | Zhongke    |                    |  |  |

AT6558 main peripheral components BOM table

www.icofchina.com

|            |          |                                                              |                                                                                     | Micro           |                 |

|------------|----------|--------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------|-----------------|

| Filter SAW |          |                                                              | Insertion Loss= 0.9dB@1575.42M<br>impedance=50Ω                                     | TDK EPCOS       | B39162B9416K610 |

|            | 0.001411 | Insertion Loss = $0.95$ dB@1575.42M<br>impedance= $50\Omega$ | MURATA                                                                              | SAFEB1G57KE0F00 |                 |

|            | SAW      | SMD1411                                                      | Insertion Loss = $0.9$ dB@1575.42M<br>1.3dB@1602M, impedance=50 $\Omega$            | MUKAIA          | SAFEA1G58KA0F00 |

|            |          |                                                              | Insertion Loss = $1.0$ dB@ $1575.42$ M<br>$1.3$ dB@ $1602$ M, impedance= $50\Omega$ | WISOL           | SFHG89DQ102     |

## **10** Application Solutions

#### **10.1** Active Antenna Feed and Detection

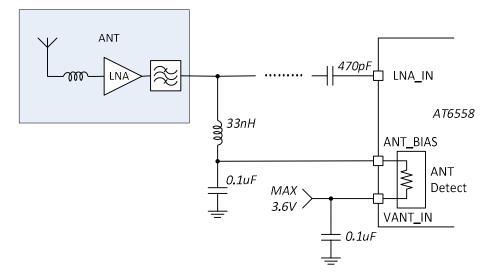

The following figure, the chip active antenna detection circuit can detect the state of the active antenna, VANT\_IN connected to a system power supply, the maximum voltage 3.6V.ANT\_BIAS connected to a 33nH and 0.1uF inductor capacitor filter for blocking the AC signal, and feed to the active antenna.

Note: Even if the LC filter is added to block AC signal, low frequency communication large signal is still likely to feed through to ANT\_BIAS port and cause detection circuit miscalculation. Especially in the strong interference environment or near the high power transmission device, the probability of miscalculation will increase.

The minimum detection current for antenna access is 2.5mA, and the current limit of short circuit protection is 50mA.

#### 10.2 RF Input

Signal input from the LNA\_IN, external antenna unit (passive medium +LNA, or active antenna) is recommended for the gain of 18~35dB. No matter what form of the antenna, it is recommended to carry out the power supply through the ANT\_BIAS. The chip can automatically adjust the internal gain by the state of the antenna, so that the chip can work in the optimum gain state.

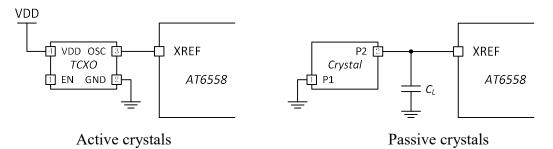

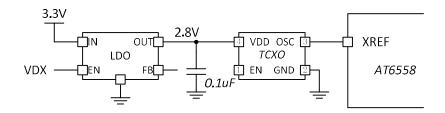

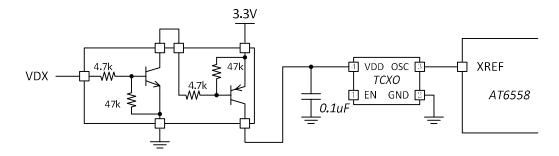

#### **10.3** Reference Clock Oscillator

The reference clock frequency stability will greatly affect the receiver performance, including sensitivity, positioning accuracy, timing accuracy. Normally, in order to obtain the optimal performance, it is recommended that the user chooses high stability crystal oscillator for clock reference source of navigation chip. Recommended temperature compensated crystal oscillator which frequency stability is 0.5ppm, and is not sensitive to temperature and vibration environment.

The chip also supports passive crystal as a clock reference source, due to passive crystal instantaneous frequency drift is large, positioning accuracy is inferior to TCXO. Due to the passive oscillator frequency is not fixed and the precision is poor, every batch of navigation firmware of passive crystals need to customize, so don't recommend to use passive crystals.

Commonly used the circuit connection of active crystals and passive crystals are as follows:

(Chip firmware needs to be customized)

P1 which is one end of the passive crystal connect to ground, and P2 which is the other end of the passive crystal connect to chip XREF, at the same time, a capacitor CL is connected in parallel to the ground on P2. The value of CL is the load capacitance of the crystal. Different crystals may be different, the general 12pF can be.

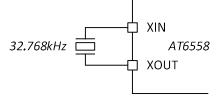

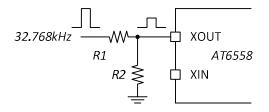

#### **10.4** RTC Clock

Real time clock (RTC) is located in the battery power supply area, which ensures that the Backup data in RAM is not lost when the main power supply is off .When the main power supply is power on again, it can quickly re-positioning. RTC OSC using passive crystal, connected to the XIN and XOUT pins of the chip, without the off-chip

capacitor and the feedback resistor, as shown below:

32k RTC Passive crystal

Chip also supports the direct clock input, the user can choose from the XIN or XOUT input, but need to ensure that the instantaneous voltage on the XIN or XOUT not more than 1.5 V.As shown below, the clock signal is added to the XOUT through the resistor voltage divider, and adjust the ratio of R1 to R2, so that the clock high level on the XOUT is 1.2V.

32K direct clock input (resistor voltage divider)

#### **10.5** GPIO

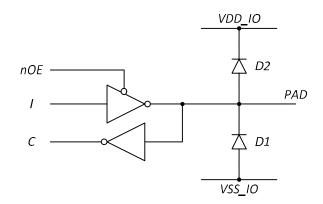

Chip provides 10 GPIO, can be reused for UART, I2C, SPI, etc.. Its main internal structure is as follows:

It must keep the PAD voltage which is less than VDD\_IO+0.5V in use, otherwise it will appear ESD diode D2 forward conduction and lead to the chip working abnormal.

Special note: when the GPIO as the input IO, such as RXD1/RXD2, chip

AT6558

VDD\_IO power down, the external device should set the GPIO port signal voltage to low level.

#### **10.6** Low Power Setting

AT6558 can provide two kinds of low power solution those are automatic low power mode and external control low power mode.

Automatic low power consumption mode is that in the non continuous positioning scenarios, the chip positioning, internal procedures automatically turn off the power module, enter standby mode; Wake up automatically and carry on the next position by the timer. According to the different application scenarios, the program needs to customize.

External control low power mode has three kinds of way1) shut down the main power supply; 2) set ON\_OFF pin to low level; 3) send low power instructions through the UART.

| Power mo            | Power mode   |              | IO/POR       | LNA          | TCXO         | Antenna      | RTC          | Main   |

|---------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------|

|                     |              |              |              |              |              |              |              | power  |

|                     |              |              |              |              |              |              |              | supply |

| Full working mode   |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | ON     |

| Automatic low power |              | ×            | $\checkmark$ | ×            | ×            | ×            | $\checkmark$ | ON     |

| mode                |              |              |              |              |              |              |              |        |

| External            | Shut down    | ×            | ×            | ×            | ×            | ×            | $\checkmark$ | OFF    |

| control             | main power   |              |              |              |              |              |              |        |

| low                 | supply       |              |              |              |              |              |              |        |

| power               | ON_OFF Pull  | ×            | $\checkmark$ | ×            | ×            | ×            | $\checkmark$ | ON     |

| mode                | down         |              |              |              |              |              |              |        |

|                     | UART         | ×            | $\checkmark$ | ×            | $\checkmark$ | ×            |              | ON     |

|                     | instructions |              |              |              |              |              |              |        |

#### 10.6.1 Enter Low Power Mode

#### 1) Shut down main power supply

In the power connection as shown in the figure below, shut down the main power supply VMAIN. In addition to the backup circuit, all other circuit power down, power consumption is close to 0.

Special note: the GPIO as input, such as RXD1 / RXD2, chip VDD\_IO power down, the external device should be set the signal voltage of the GPIO port to low level.

2) Set the ON OFF pin to a low level

Mains VMAIN electricity normally, ON\_OFF pin is set to the low level through external MCU, the chip will enter a low-power standby state, the chip consumes only minimal power consumption. External active antenna, LNA, TCXO and so on will be closed.

3) Send instruction via UART

Mains VMAIN electricity normally, through external UART send instructions that enter the low power mode, the chip will shut down most of the circuit, enter the low power standby state. External active antenna, LNA and so on shut down. TCXO work normally.

4) Automatic Low Power Mode

In the sleep and wake time interval of system definition, the chip automatically enter the low power mode.

#### 10.6.2 Peripheral Circuit Connection Solutions

1 ) Chip Power Supply

Hangzhou ZhongKe Microelectronics CO.,Ltd

#### 2) Antenna or external LNA enable

An external LNA or antenna unit is powered by ANT\_BIAS and achieve enable Normal work, the ANT\_BIAS output supply power to external LNA or antenna unit; low power consumption, ANT\_BIAS off, then the external LNA or antenna is closed, no longer consumes the charge current.

3) TCXO Power Supply

ON\_OFF low power mode and independent low power mode need to close the TCXO to further reduce power consumption.

Separate LDO or NPN-PNP composite transistor chip supply power to TCXO, using the output of the chip DCDC VDX as enabling signal.

Using LDO supply power to TCXO

Hangzhou ZhongKe Microelectronics CO.,Ltd

Using a compound transistor chip supply power to TCXO

#### **10.7 DCDC**

In order to obtain the lowest power consumption and optimal performance, it is recommended to use on-chip DCDC converter, the output of the DCDC supply on-chip LDO again. It can effectively reduce the power consumption of the chip.

In order to reduce the influence of DCDC switching frequency on the performance of the chip, the connection length of the 4.7uH inductor and the 10uF capacitor with the pin DX\_OUT must be minimized. Filter circuit is particularly important, and it is recommended that each power input is added to the 1uF filter capacitor, if necessary, plus other filter power circuit.

Special attention, both ground wire that a filter capacitor of the power input DX\_IN and ground wire that the filter capacitor after output DX\_OUT inductance should have good connection with GND. If the ground wire is through the PCB via hole connected to the GND, should be respectively through via hole connected to the GND, and try to increase the number of via hole.

## **11 Packaging and Transportation**

### **11.1** Packaging

AT6558 chip use moisture roll tape for packaging.

#### **11.2 ESD Protection**

Please pay attention to the antistatic and moisture proof in the process of chip transportation and production.

# CAUTION! ESD SENSITIVE DEVICE!

Please pay attention to the electrostatic protection in the process of using, packaging and transportation!

## **12 Document Update Record**

| Date       | Version | Instruction                                            |

|------------|---------|--------------------------------------------------------|

| 2015.06.30 | V1.08   | The first version of the official release              |

| 2015.07.20 | V1.09   | 1 Modify the ANT_BIAS pin definition                   |

|            |         | 2 Add backup power note 3.2.3                          |

|            |         | 3 Add the power consumption mode 3.2.4                 |

|            |         | 4 Add chip reset instructions 3.3                      |

|            |         | 5 Modify the reference design                          |

|            |         | 6 Add application solutions and recommendations        |

|            |         | section                                                |

| 2015.07.20 | V1.10   | Not supported passive crystal                          |

| 2015.08.12 | V1.11   | 1 Modify the default support for crystal frequency     |

|            |         | 2 Add a reference clock crystal selection section 10.3 |

| 2015.12.01 | V1.12   | 1 Modify IO/POR power range to 2.8~3.6V                |

|            |         | 2 Add DCDC instructions                                |

|            |         | 3 Modify passive antenna solution                      |

AT6558

AT6558

| single GPS   |

|--------------|

| dual mode    |

| positioning, |

| 5            |

|              |

| chapter 10   |

|              |

| 2 passive    |

| heme, and    |

|              |

|              |

|              |

|              |

|              |

## Contact

Hangzhou ZhongKe Microelectronics CO.,Ltd.

10F Innovation Tower,3850# Jiangnan Avenue Binjiang, Hangzhou, China

Tel: 0571-28918107

Fax: 0571-28918122

Website : http://www.icofchina.com