## **APPLICATION NOTE – REFERENCE DESIGN**

# MODEL NAME : 3.7inch e-Paper 2 bit B/W/DG/LG

## 1 About This Application Note

This document describes a reference design system that integrates E Ink's black, white, dark gray and light gray 3.69" display (3.7inch e-Paper). It includes an application circuit, timing information and pin assignments for the ePaper display module.

### 2 Overview

This display is a 280x480 ePaper display with integrated timing control and power management circuitry. Each pixel on the display has the capability of showing black, white, dark gray and light gray. The 3.7inch e-Paper is ideal for applications such as signage for retail pricing.

## 3 Device Interface

This chapter describes the interface and pin assignments of the3.7 inch e-Paper panel.

| Pin As | signment |        |                                                          |

|--------|----------|--------|----------------------------------------------------------|

| Pin #  | Туре     | Single | Description                                              |

| 1      |          | NC     | No connection and do not connect with other NC pins      |

| 2      | 0        | GDR    | N-Channel MOSFET Gate Drive Control                      |

| 3      | 0        | RESE   | Current Sense Input for the Control Loop                 |

| 4      |          | NC     | No connection and do not connect with other NC pins      |

| 5      | Р        | VSH2   | Positive source driver voltage for Red                   |

| 6      | 0        | TSCL   | I2C Interface to digital temperature sensor Clock pin    |

| 7      | I/O      | TSDA   | I2C Interface to digital temperature sensor Date pin     |

| 8      | I        | BS     | Bus selection pin; L: 4-wire IF. H: 3-wire IF. (Default) |

| 9      | 0        | BUSY_N | Busy state output pin                                    |

| 10     | I        | RST_N  | Reset                                                    |

| 11     | I        | DC     | Data /Command control pin                                |

| 12     | I        | CSB    | Chip Select input pin                                    |

| 13     | I        | SCL    | serial clock pin (SPI)                                   |

| 14     | I/O      | SDA    | serial data pin (SPI)                                    |

| 15     | Р        | VDDIO  | Supply voltage                                           |

| 16     | Р        | VCI    | Supply voltage                                           |

| 17     | Р        | VSS    | Ground                                                   |

| 18     | Р        | VDD    | Core logic power pin                                     |

| 19     |          | VPP    | OTP Program power                                        |

| 20     | Р        | VSH1   | Positive Source driving voltage                          |

| 21     | Р        | VGH    | Positive Gate driving voltage                            |

| 22     | Р        | VSL    | Negative Source driving voltage                          |

| 23     | Р        | VGL    | Negative Gate driving voltage                            |

| 24     | Р        | VCOM   | VCOM driving voltage                                     |

|        |          |        |                                                          |

#### Table 1 Pin descriptions for 3.7inch e-Paper

I: Input Pin; O: Output Pin; I/O: Input/Out Pin; P: Power Pin

#### 3.1 3-Wire SPI and 4-Wire SPI setting

Please follow below table for SPI HW setting that you want use

| BS   | Interface  | CSB  | DC   | SCL  | SDA  |

|------|------------|------|------|------|------|

| High | 3-wire SPI | High | Low  | High | High |

| Low  | 4-wire SPI | High | High | High | High |

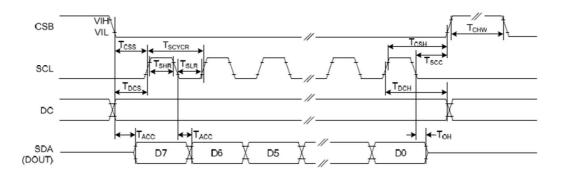

### 3.2 SPI Interface Timing

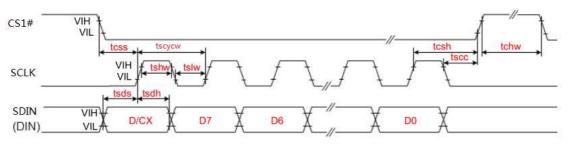

3-wire Serial Interface - Write

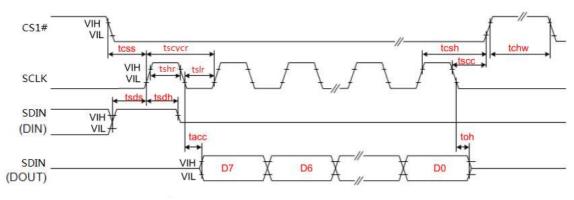

3-wire Serial Interface - Read

Figure 1 3-wire SPI Timing Diagram

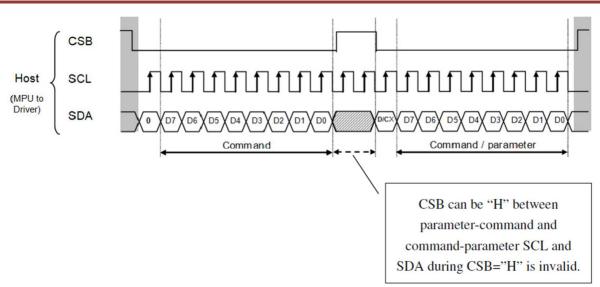

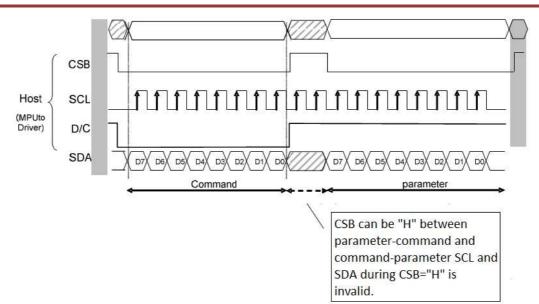

Figure 2 Host Communications Timing Diagram

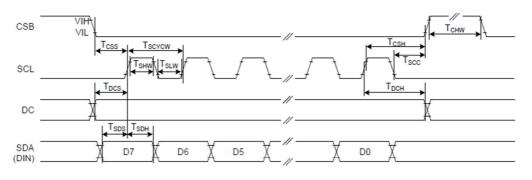

Figure: 4-wire Serial Interface Characteristics (Write mode)

Figure: 4-wire Serial Interface Characteristics (Read mode)

Figure 3 4-wire SPI Timing Diagram

| <b>Figure 4 Host Communications</b> | Timing Diagram |

|-------------------------------------|----------------|

|                                     |                |

| Symbol         | Signal              |                             | Min | Тур | Max | Unit |

|----------------|---------------------|-----------------------------|-----|-----|-----|------|

| SERIAL COMMUNI | CATION              |                             |     |     |     |      |

| tCSS           |                     | Chip select setup time      | 60  |     |     | ns   |

| tCSH           | CSB                 | Chip select hold time       | 65  |     |     | ns   |

| tSCC           | CSB                 | Chip select setup time      | 20  |     |     | ns   |

| tCHW           |                     | Chip select setup time      | 40  |     |     | ns   |

| tSCYCW         |                     | Serial clock cycle (Write)  | 100 |     |     | ns   |

| tSHW           |                     | SCL "H" pulse width (Write) | 35  |     |     | ns   |

| tSLW           | SCL                 | SCL "L" pulse width (Write) | 35  |     |     | ns   |

| tSCYCR         | SCL                 | Serial clock cycle (Read)   | 150 |     |     | ns   |

| tSHR           |                     | SCL "H" pulse width (Read)  | 60  |     |     | ns   |

| tSLR           |                     | SCL "L" pulse width (Read)  | 60  |     |     | ns   |

| tSDS           | 604                 | Data setup time             | 30  |     |     | ns   |

| tSDH           | SDA                 | Data hold time              | 30  |     |     | ns   |

| tACC           | – (DIN)<br>– (DOUT) | Access time                 |     |     | 10  | ns   |

| tOH            |                     | Output disable time         | 15  |     |     | ns   |

Table 2 Timing Table

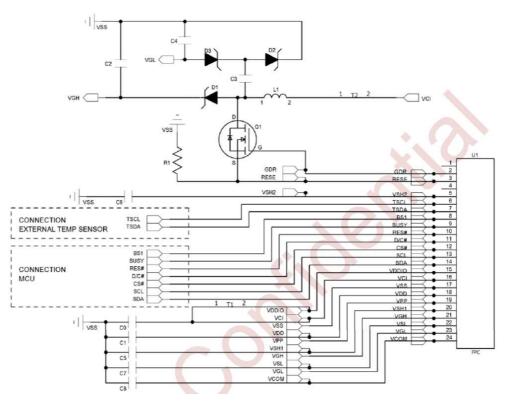

#### 4 Reference circuit

| Part Name | Value   | Reference Part/ Requirement       |

|-----------|---------|-----------------------------------|

| C0-C1     | 1uF     | 0603; X5R/X7R; Voltage Rating 6V  |

| C2-C7     | 4.7uF   | 0805; X5R/X7R; Voltage Rating 25V |

| C8        | 1uF     | X7R; Voltage Rating 25V           |

| R1        | 2.2 Ohm | 0805; 1%                          |

Figure 5 3.7inch e-Paper Reference Circuit

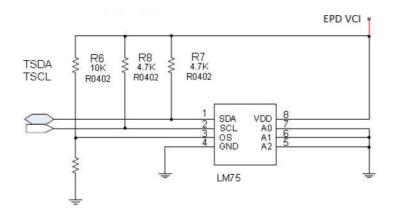

Figure 6 Temperature Sensor Circuit (optional)

## 5 Software Programming Guide

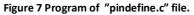

This chapter describes image update flow of 3.7inch e-Paper. Defining the pin connection between MCU and the display is needed. The definition is customized in the file "pindefine.c" User only need to assign the MCU pins to connect the pins defined in this file. The definition is shown in figure 7. When the pin define setting is done, the display is automatically controlled by the function. The next two sections will describe the simulation of SPI transmission protocol and image update flow.

| MSP430f550x port define                |                        |

|----------------------------------------|------------------------|

| //OUTPUT                               |                        |

|                                        | www.even.WCU.min.hana  |

|                                        | vour own MCU pin here. |

|                                        |                        |

| #define DC_H P5OUT =0x01               |                        |

| //Pin define jar BS                    |                        |

| #define BS_L P6OUT&=0xFE               |                        |

| #define BS_H P6OUT =0x01               |                        |

| //Pin define j <mark>o</mark> r RSTN   |                        |

| #define RSTN_L P6OUT&=0xFD             |                        |

| #define RSTN_H P6OUT =0x02             |                        |

| //Pin define f <mark>a</mark> r CSB    |                        |

| #define CSB_L P6OUT&=0xF7              |                        |

| #define CSB_H P6OUT =0x08              |                        |

| //Pin define f <mark>o</mark> r SCL    | MCI I nin accian       |

| #define SCL_L P4OUT&=0x7F              | MCU pin assign         |

| #define SCL_H P4OUT =0x80              |                        |

| //Pin define jor SDA                   |                        |

| #define SDA L P4OUT&=0xBF              |                        |

| #define SDA_H P4OUT = 0x40             |                        |

| _                                      | Define pin for panel   |

| //======= Irrut ========               | Define plit for parter |

| // UC8154                              |                        |

| //Pin define for SDA_IN                |                        |

| #define SDA_IN (P4IN&0x40)>>6          |                        |

| #define BUSYN P6IN_bit.P6IN2           |                        |

| <pre>#endif //#ifncefPINDEFINE_H</pre> |                        |

| renear //#cjincerranderane_n_          |                        |

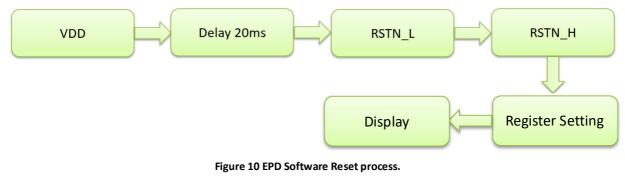

#### 5.1 EPD Software Reset

EPD software reset is include in the function "void EPD\_Init(void)". The setting process is illustrated in figure 10. The last step "check\_busy" is important for the programming sequence. The main idea is to check the device is powered up. Two functions are defined in table 5.

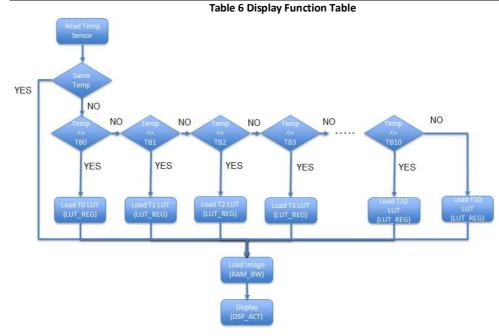

#### 5.2 Display

There are 2 image display functions, which are listed in table 6 with frame buffer settings (Ram BW and Ram Red). The display process is shown in figure 12. Frame buffer settings will be introduced next chapter.

#### Table 5 check\_busy Function Table

| Function                   | Description             |  |  |

|----------------------------|-------------------------|--|--|

| void check_busy_high(void) | Check high peak finish. |  |  |

| void check_busy_low(void)  | Check low peak finish.  |  |  |

| Table 5 check_busy Fi      | unction Table           |  |  |

| Function                     | Description         | RAM BW | Ram Red |

|------------------------------|---------------------|--------|---------|

| void EPD_Display_White(void) | Display white image | 0xFF   | OxFF    |

| void EPD_Display_Black(void) | Display black image | 0x00   | 0x00    |

| void EPD_Display_LG(void)    | Display LG image    | 0x00   | OxFF    |

| void EPD_Display_DG(void)    | Display DG image    | 0xFF   | 0x00    |

#### Figure 12 Display process

|      | Temperature Range                            |

|------|----------------------------------------------|

| тво  | 0 <temperature <="5&lt;/td"></temperature>   |

| TB1  | 5 <temperature <="10&lt;/td"></temperature>  |

| TB2  | 10 <temperature <="15&lt;/td"></temperature> |

| TB3  | 15 <temperature <="20&lt;/td"></temperature> |

| TB4  | 20 <temperature <="25&lt;/td"></temperature> |

| TB5  | 25 <temperature <="30&lt;/td"></temperature> |

| TB6  | 30 <temperature <="35&lt;/td"></temperature> |

| TB7  | 35 <temperature <="40&lt;/td"></temperature> |

| TB8  | 40 <temperature <="45&lt;/td"></temperature> |

| TB9  | 45 <temperature <="50&lt;/td"></temperature> |

| TB10 | 50 <temperature <="55&lt;/td"></temperature> |

Table 7 Temperature Range Table

## 6 Registers Table

| W# | D/C#          | Hex       | <b>D</b> 7    | D6             | D5             | D4             | D3                                      | D2             | Dl              | <b>D</b> 0     | Comm       | Command                |                 | Description                      |  |  |  |

|----|---------------|-----------|---------------|----------------|----------------|----------------|-----------------------------------------|----------------|-----------------|----------------|------------|------------------------|-----------------|----------------------------------|--|--|--|

| 0  | 0             | 04        | 0             | 0              | 0              | 0              | 0                                       | 1              | 0               | 0              | Source     | Source Driving voltage |                 | Set Source driving voltage       |  |  |  |

| 0  |               | ••        |               |                |                |                | 10                                      | 77.            |                 | 2070           | Contro     |                        |                 | A[7:0] = 41h [POR], VSH1 at 15V  |  |  |  |

| _  | 1             |           | A7            | A6             | A5             | A <sub>4</sub> | A3                                      | A <sub>2</sub> | A <sub>1</sub>  | A <sub>0</sub> | - Control  | p.                     |                 | B[7:0] = A8h [POR], VSH2 at 5V.  |  |  |  |

| 0  | 1             |           | <b>B</b> 7    | B <sub>6</sub> | B <sub>5</sub> | B4             | <b>B</b> <sub>3</sub>                   | B <sub>2</sub> | B <sub>1</sub>  | Bo             |            |                        |                 | C[7:0] = 32h [POR], VSL at -15V  |  |  |  |

| 0  | 1             | 2         | C7            | C6             | C5             | C4             | C3                                      | C2             | C1              | Co             | 1          |                        |                 | C[7.0] = 5211 [FOR], VSL at -15V |  |  |  |

| ~  |               |           | - Cr          | 00             | 0.0            |                | 0.                                      | 0.0000000      | ive setting     |                |            |                        |                 | 0[7] 0                           |  |  |  |

|    | ] = 1,        |           |               | C              | 2 47           |                |                                         |                | 7]/B[           |                |            |                        | 011             | C[7] = 0,                        |  |  |  |

|    |               | Itage     | setting       | g from         | n 2.4 v        | to             |                                         |                |                 | SH2            | voltage    | setting fr             | om 9V           | VSL setting from -9V to -17V     |  |  |  |

| .8 |               | 1.000     | 10.000        |                |                |                | 0110                                    | 1000           | 17V             | 1.10           |            | 1 (0)(7,0)             |                 |                                  |  |  |  |

|    | B[7:0]<br>8Eh | 1.0.25    | 1/VSH2<br>2.4 |                | [7:0]<br>Fh    | VSH1/V<br>5.7  | 5 C C C C C C C C C C C C C C C C C C C |                | A/B[7:0]<br>23h | VS             | H1/VSH2    | A/B[7:0]<br>3Ch        | VSH1/VSH:<br>14 |                                  |  |  |  |

|    | 8Eh           |           | 2.4           |                | Oh             | 5.8            |                                         |                | 23h             | -              | 9.2        | 3Dh                    | 14              | 1Ah -9                           |  |  |  |

|    | 90h           |           | 2.5           | 1              | un<br>1h       | 5.9            |                                         |                | 24n<br>25h      | - 3            | 9.2        | 3Dh<br>3Eh             | 14.2            | 1Ch -9.5                         |  |  |  |

|    | 91h           |           | 2.7           | 6              | 2h             | 6              |                                         |                | 26h             |                | 9.6        | 3Fh                    | 14.6            | 1Eh -10<br>20h -10.5             |  |  |  |

|    | 92h           |           | 2.8           |                | 3h             | 6.1            |                                         |                | 27h             | - 16           | 9.8        | 40h                    | 14.8            |                                  |  |  |  |

|    | 93h           |           | 2.9           |                | 4h             | 6.2            |                                         |                | 28h             |                | 10         | 41h                    | 15              | 22h -11<br>24h -11.5             |  |  |  |

| -  | 94h           |           | 3             | В              | 5h             | 6.3            |                                         |                | 29h             | 1              | 10.2       | 42h                    | 15.2            |                                  |  |  |  |

| _  | 95h           |           | 3.1           | B              | 6h             | 6.4            |                                         |                | 2Ah             |                | 10.4       | 43h                    | 15.4            | 26h -12<br>28h -12.5             |  |  |  |

| _  | 96h           | 1         | 3.2           | B              | 7h             | 6.5            |                                         |                | 2Bh             |                | 10.6       | 44h                    | 15.6            | 20n -12.5<br>2Ah -13             |  |  |  |

| _  | 97h           | -         | 3.3           |                | 8h             | 6.6            |                                         |                | 2Ch             |                | 10.8       | 45h                    | 15.8            | 13<br>2Ch 13.5                   |  |  |  |

|    | 98h           | 2         | 3.4           |                | 9h             | 6.7            |                                         |                | 2Dh             |                | 11         | 46h                    | 16              | 2Ch -13.5<br>2Eh -14             |  |  |  |

|    | 99h           |           | 3.5           |                | Ah             | 6.8            |                                         |                | 2Eh             |                | 11.2       | 47h                    | 16.2            | 30h -14.5                        |  |  |  |

|    | 9Ah           |           | 3.6           |                | Bh             | 6.9            |                                         |                | 2Fh             |                | 11.4       | 48h                    | 16.4            | 30n -14.5<br>32h -15             |  |  |  |

|    | 9Bh           |           | 3.7           |                | Ch             | 7              |                                         |                | 30h             | -              | 11.6       | 49h                    | 16.6            | 32/1 -15<br>34h -15.5            |  |  |  |

|    | 9Ch<br>9Dh    | 2         | 3.8<br>3.9    | K              | Dh<br>Eh       | 7.1            |                                         |                | 31h<br>32h      | - 12           | 11.8<br>12 | 4Ah<br>4Bh             | 16.8            | 3411 -15.5<br>36h -16            |  |  |  |

|    | 9Eh           | 8         | 4             | 7.0            | Fh             | 7.3            |                                         |                | 32h             |                | 12.2       | Other                  | NA              | 38h -16.5                        |  |  |  |

|    | 9Fh           | -         | 4.1           |                | Oh             | 7.4            |                                         |                | 34h             |                | 12.4       | Other                  | 197             | 3Ah -17                          |  |  |  |

|    | A0h           |           | 4.2           | c              | 1h             | 7.5            |                                         |                | 35h             | -              | 12.6       | 107 .                  |                 | Other NA                         |  |  |  |

|    | A1h           | 2         | 4.3           | K 24           | 2h             | 7.6            |                                         |                | 36h             |                | 12.8       | 1                      |                 | Oulei IVA                        |  |  |  |

| -  | A2h           | 0         | 4.4           | C              | 3h             | 7.7            |                                         |                | 37h             |                | 13         | 200                    |                 | E.                               |  |  |  |

| _  | A3h           | 1 6       | 4.5           | C              | 4h             | 7.8            |                                         |                | 38h             | 1              | 13.2       |                        |                 |                                  |  |  |  |

|    | A4h           | 2         | 4.6           | ×              | 5h             | 7.9            |                                         |                | 39h             | 12             | 13.4       |                        |                 |                                  |  |  |  |

| _  | A5h           |           | 4.7           | 12             | 6h             | 8              |                                         |                | 3Ah             |                | 13.6       |                        | 19.             |                                  |  |  |  |

|    | A6h           | 2 · · · · | 4.8           | 5 I I          | 7h             | 8.1            |                                         |                | 3Bh             |                | 13.8       | Y                      |                 |                                  |  |  |  |

|    | A7h           | 0         | 4.9           | 5              | 8h             | 8.2            |                                         |                |                 |                |            |                        |                 |                                  |  |  |  |

| _  | A8h           | 2         | 5             | 1              | 9h             | 8.3            |                                         |                |                 |                |            |                        |                 |                                  |  |  |  |

|    | A9h           |           | 5.1           |                | Ah             | 8.4            |                                         |                |                 |                |            |                        |                 |                                  |  |  |  |

| _  | AAh<br>ABh    | -         | 5.2<br>5.3    |                | Bh             | 8.5            |                                         |                |                 |                |            |                        |                 |                                  |  |  |  |

|    | ABh           |           | 5.3           | 5              | Dh             | 8.0            |                                         |                |                 |                |            |                        |                 |                                  |  |  |  |

|    | ADh           | 2         | 5.5           | X              | Eh             | 8.8            |                                         |                |                 |                |            |                        |                 |                                  |  |  |  |

|    |               |           | 5.6           |                | ther           | NA             |                                         |                |                 |                |            |                        |                 | Remark: VSH1>                    |  |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                               | 0 0 | 0 | A4 . | A3 A3 | Aı  | A <sub>0</sub> | Control  | VGH settin<br>A[4:0]<br>00h | ng from 12<br>VGH        | A[4:0]                                              |                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|------|-------|-----|----------------|----------|-----------------------------|--------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------|

| O0h   20   10h   16.5     07h   12   11h   17     08h   12.5   12h   17.5     09h   13   13h   18     0Ah   13.5   14h   18.5     0Bh   14   15h   19     0Ch   14.5   16h   19.5     0Dh   15   17h   20     0Eh   15.5   Other   NA |     |   |      |       |     |                |          | 00h                         |                          | K                                                   |                                                                               |

| 07h   12   11h   17     08h   12.5   12h   17.5     09h   13   13h   18     0Ah   13.5   14h   18.5     0Bh   14   15h   19     0Ch   14.5   16h   19.5     0Dh   15   17h   20     0Eh   15.5   Other   NA                           |     |   |      |       |     |                |          |                             | 20                       | 10h                                                 | 16.5                                                                          |

| 08h   12.5   12h   17.5     09h   13   13h   18     0Ah   13.5   14h   18.5     0Bh   14   15h   19     0Ch   14.5   16h   19.5     0Dh   15   17h   20     0Eh   15.5   Other   NA                                                   |     |   |      |       |     |                |          | 20                          |                          |                                                     |                                                                               |

| 09h   13   13h   18     0Ah   13.5   14h   18.5     0Bh   14   15h   19     0Ch   14.5   16h   19.5     0Dh   15   17h   20     0Eh   15.5   Other   NA                                                                               |     |   |      |       |     | 1              |          | 07h                         | 12                       | 11h                                                 | 17                                                                            |

| 0Ah   13.5   14h   18.5     0Bh   14   15h   19     0Ch   14.5   16h   19.5     0Dh   15   17h   20     0Eh   15.5   Other   NA                                                                                                       |     |   |      |       |     |                |          | 08h                         | 12.5                     | 12h                                                 | 17.5                                                                          |

| 0Bh   14   15h   19     0Ch   14.5   16h   19.5     0Dh   15   17h   20     0Eh   15.5   Other   NA                                                                                                                                   |     |   |      |       |     |                |          | 09h                         | 13                       | 13h                                                 | 18                                                                            |

| 0Ch   14.5   16h   19.5     0Dh   15   17h   20     0Eh   15.5   Other   NA                                                                                                                                                           |     |   |      |       |     |                | 0Ah 13.5 | 13.5                        | 14h                      | 18.5                                                |                                                                               |

| 0Dh   15   17h   20     0Eh   15.5   Other   NA                                                                                                                                                                                       |     |   |      |       |     |                |          | 0Bh                         | 14                       | 15h                                                 | 19                                                                            |

| 0Eh 15.5 Other NA                                                                                                                                                                                                                     |     |   |      |       |     |                |          | 0Ch                         | 14.5                     | 16h                                                 | 19.5                                                                          |

|                                                                                                                                                                                                                                       |     |   | 0Dh  | 15    | 17h | 20             |          |                             |                          |                                                     |                                                                               |

| 0Fh 16                                                                                                                                                                                                                                |     |   |      |       |     |                |          | 0Eh                         | 15.5                     | Other                                               | NA                                                                            |

|                                                                                                                                                                                                                                       | 1   |   |      |       |     |                |          | 0Fh                         | 16                       | 1                                                   | D.                                                                            |

|                                                                                                                                                                                                                                       |     |   |      |       |     |                |          |                             |                          |                                                     |                                                                               |

|                                                                                                                                                                                                                                       |     |   |      |       |     |                |          |                             |                          |                                                     |                                                                               |

|                                                                                                                                                                                                                                       |     |   |      |       |     |                |          |                             | 0Bh<br>0Ch<br>0Dh<br>0Eh | OBh   14     OCh   14.5     ODh   15     OEh   15.5 | 0Bh   14   15h     0Ch   14.5   16h     0Dh   15   17h     0Eh   15.5   Other |

| 0 | 0 | 20 | 0  | 0              | 1  | 0  | 0  | 0              | 0              | 0  | Master Activation | The Displa<br>located at I<br>BUSY pad<br>operation. | risplay Update Sequence<br>ny Update Sequence Option is<br>R22h.<br>I will output high during<br>User should not interrupt this<br>o avoid corruption of panel |

|---|---|----|----|----------------|----|----|----|----------------|----------------|----|-------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 0 | 21 | 0  | 0              | 1  | 0  | 0  | 0              | 0              | 1  | Display Update    | RAM cont                                             | ent option for Display Update                                                                                                                                  |

| 0 | 1 |    | A7 | A <sub>6</sub> | As | A4 | A3 | A <sub>2</sub> | A <sub>1</sub> | Ao | Control 1         | A[7:0] = 0                                           | 0h [POR]                                                                                                                                                       |

|   |   |    |    |                |    |    |    |                | -              |    |                   | A[7:4] Rec                                           | RAM option                                                                                                                                                     |

|   |   |    |    |                | 1  |    |    |                |                |    |                   | 0000                                                 | Normal                                                                                                                                                         |

|   |   |    |    |                |    |    |    |                |                |    |                   | 0100                                                 | Bypass RAM content as 0                                                                                                                                        |

|   |   |    |    |                |    |    |    | 1              |                |    |                   | 1000                                                 | Inverse RAM content                                                                                                                                            |

|   |   |    |    |                |    |    |    |                |                |    |                   | A[3:0] BW                                            | RAM option                                                                                                                                                     |

|   |   |    |    |                |    |    |    |                |                |    |                   | 0000                                                 | Normal                                                                                                                                                         |

|   |   |    |    |                |    |    |    |                |                |    |                   | 0100                                                 | Bypass RAM content as 0                                                                                                                                        |

|   |   | 19 |    |                | 0  |    |    |                |                |    |                   | 1000                                                 | Inverse RAM content                                                                                                                                            |

|   | nand<br>D/C# |    | D7             | D6             | D5 | D4             | D3         | D2             | Dl         | D0             | Command        | Description                                                                                                                                                                                                                      |                       |

|---|--------------|----|----------------|----------------|----|----------------|------------|----------------|------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 0 | 0            | 22 | 0              | 0              | 1  | 0              | 0          | 0              | 1          | 0              | Display Update | Display Update Sequence Option:                                                                                                                                                                                                  |                       |

| 0 | 1            |    | A <sub>7</sub> | A <sub>6</sub> | As | A <sub>4</sub> | <b>A</b> 3 | A <sub>2</sub> | <b>A</b> 1 | A <sub>0</sub> | Control 2      | Enable the stage for Master Activation<br>A[7:0]= FFh (POR)                                                                                                                                                                      |                       |

|   |              |    |                |                |    |                |            |                |            |                |                | Operating sequence                                                                                                                                                                                                               | Parameter<br>(in Hex) |

|   |              |    |                |                |    |                |            |                |            |                |                | Enable clock signal                                                                                                                                                                                                              | 80                    |

|   |              |    |                |                |    |                |            |                |            |                |                | Disable clock signal                                                                                                                                                                                                             | 01                    |

|   |              |    |                |                |    |                |            |                |            |                |                | Enable clock signal Enable Analog                                                                                                                                                                                                | CO                    |

|   |              |    |                |                |    |                |            |                |            |                |                | Enable clock signal Enable Analog<br>Disable Analog Disable clock signal                                                                                                                                                         | 03                    |

|   |              |    |                |                |    |                |            |                |            |                |                | Disable Analog Disable clock signal                                                                                                                                                                                              | 03                    |

|   |              |    |                |                |    |                |            |                |            |                |                | Enable clock signal<br>Load LUT with DISPLAY Mode 1<br>Disable clock signal<br>Enable clock signal                                                                                                                               | 91                    |

|   |              |    |                |                |    |                |            |                |            |                |                | Load LUT with DISPLAY Mode 2<br>Disable clock signal                                                                                                                                                                             | 99                    |

|   |              |    |                |                |    |                |            |                |            |                |                | Enable clock signal<br>Load temperature value from I2C<br>Single Master Interface<br>Load LUT with DISPLAY Mode 1<br>Disable clock signal                                                                                        | B1                    |

|   |              |    |                |                |    |                |            |                |            |                | . 2            | Enable clock signal<br>Load temperature value from I2C<br>Single Master Interface<br>Load LUT with DISPLAY Mode 2<br>Disable clock signal                                                                                        | <b>B</b> 9            |

|   |              |    |                |                |    |                |            |                |            |                | SIL            | Enable clock signal<br>Enable Analog<br>Display with DISPLAY Mode 1<br>Disable Analog<br>Disable OSC                                                                                                                             | <b>C</b> 7            |

|   |              |    |                |                |    |                |            |                |            | (              | 5              | Enable clock signal<br>Enable Analog<br>Display with <b>DISPLAY Mode</b> 2<br>Disable Analog<br>Disable OSC                                                                                                                      | CF                    |

|   |              |    |                |                |    |                |            |                |            | J              |                | Enable clock signal<br>Enable Analog<br>Load temperature value from 12C<br>Single Master Interface<br>Load temperature value from 12C<br>Single Master Interface<br>DISPLAY with DISPLAY Mode 1<br>Disable Analog<br>Disable OSC | F7                    |

|   |              |    |                |                | 5  |                |            |                |            |                |                | Enable clock signal<br>Enable Analog<br>Load temperature value from I2C<br>Single Master Interface<br>Load temperature value from I2C<br>Single Master Interface<br>DISPLAY with DISPLAY Mode 2<br>Disable Analog<br>Disable OSC | FF                    |

| R/W# D | /C# | Hex | <b>D</b> 7 | D6 | <b>D</b> 5 | D4 | D3 | D2 | D1 | D0 | Command                               | Description                                                                                                                                                                                                                                                         |

|--------|-----|-----|------------|----|------------|----|----|----|----|----|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0   | 24  | 0          | 0  | 1          | 0  | 0  | 1  | 0  | 0  | Write RAM (Black<br>White) / RAM 0x24 | After this command, data entries will be<br>written into the BW RAM until another<br>command is written. Address pointers will<br>advance accordingly<br>For White pixel:<br>Content of Write RAM(BW) = 1<br>For Black pixel:<br>Content of Write RAM(BW) = 0       |

| 0      | 0   | 26  | 0          | 0  | 1          | 0  | 0  | 1  | 1  | 0  | Write RAM (RED)<br>/ RAM 0x26         | After this command, data entries will be written into the RED RAM until another command is written. Address pointers will advance accordingly.   For Red pixel:   Content of Write RAM(RED) = 1 For non-Red pixel [Black or White]:   Content of Write RAM(RED) = 0 |

|   | 0 | 0 | 32 | 0              | 0              | 1              | 1              | 0              | 0              | 1              | 0  | • | Write LUT register from MCU interface      |

|---|---|---|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|---|--------------------------------------------|

|   | 0 | 1 |    | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | Ao |   | [105 bytes], which contains the content of |

|   | 0 | 1 |    | B7             | B <sub>6</sub> | Bs             | B4             | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | Bo |   | VS [nX-LUT], TP #[nX], RP#[n]).            |

|   | 0 | 1 |    | 1              | 1              | 1              | 1              | •              |                | 1              | 1  |   |                                            |

|   | 0 | 1 |    | -              |                | -              | -              | -              | 7.             | -              |    |   |                                            |

| • |   |   |    |                |                |                |                |                |                |                |    |   | •                                          |

#### **Revision History**

| Version | Date       | Page | Description | Author   |

|---------|------------|------|-------------|----------|

| 0.1     | 2020/06/15 |      | Initial     | Hans Yeh |

|         |            |      |             |          |