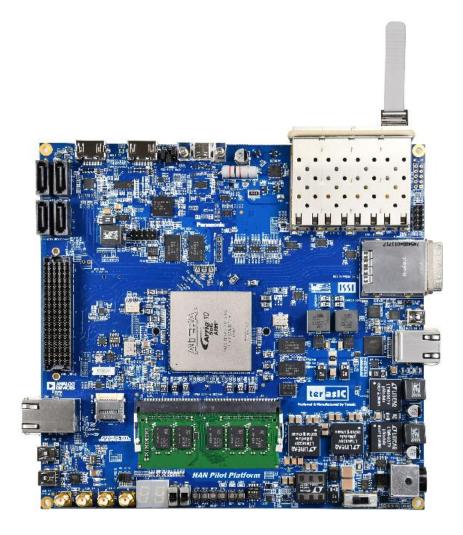

# HAN Pllot Platform

# DEMONSTRATION MANUAL

www.terasic.com Copyright © Terasic Inc. All rights reserved.

# TABLE OF CONTENTS

| Chapter 1       | Introduction                                          | 3  |

|-----------------|-------------------------------------------------------|----|

| Chapter 2       | Examples for FPGA                                     | 4  |

| 2.1 Factory Def | ault Code                                             | 4  |

| 2.2 Nios II Con | trol for Programmable PLL/ Temperature/ Power/ 9-axis | 6  |

| 2.3 Nios DDR4   | SDRAM Test                                            |    |

| 2.4 RTL DDR4    | SDRAM Test                                            | 14 |

| 2.5 USB Type-0  | C DisplayPort Alternate Mode                          | 15 |

| 2.6 USB Type-0  | C FX3 Loopback                                        | 17 |

| 2.7 HDMI TX a   | and RX in 4K Resolution                               | 21 |

| 2.8 HDMI TX i   | n 4K Resolution                                       | 26 |

| 2.9 Low Latence | y Ethernet 10G MAC Demo                               | 29 |

| 2.10 Socket Ser | ver                                                   |    |

| 2.11 Auto Fan S | Speed Control                                         | 40 |

| Chapter 3       | Examples for HPS SoC                                  |    |

| 3.1 User LED a  | nd KEY                                                | 44 |

| 3.2 Setup USB   | Wi-Fi Dongle                                          | 48 |

| 3.3 HPS GPIO    | Header                                                | 51 |

| 3.4 Network So  | cket                                                  | 55 |

| Chapter 4       | Examples for Using both HPS SoC and FPGA              | 61 |

| 4.1 Required Ba | ackground                                             | 61 |

| 4.2 System Req  | uirements                                             | 61 |

| 4.3 AXI bridges | s in Intel SoC FPGA                                   | 62 |

| 4.4 GHRD Proj   | ect                                                   | 63 |

| 4.5 Compile and | d Programming                                         | 64 |

| 4.6 Develop the | C Code                                                | 64 |

| Chapter 5       | PCI Express Design for Windows                        | 69 |

| 5.1 PCI Express System Infrastructure   | 69 |

|-----------------------------------------|----|

| 5.2 PC PCI Express Software SDK         | 70 |

| 5.3 PCI Express Software Stack          | 70 |

| 5.4 PCI Express Library API             | 75 |

| 5.5 PCIe Reference Design – Fundamental | 79 |

| 5.6 PCIe Reference Design - DDR4        |    |

| Chapter 6 PCI Express Design for Linux  | 92 |

| 6.1 PCI Express System Infrastructure   | 92 |

| 6.2 PC PCI Express Software SDK         |    |

| 6.3 PCI Express Software Stack          |    |

| 6.4 PCI Express Library API             | 96 |

| 6.5 PCIe Reference Design – Fundamental |    |

| 6.6 PCIe Reference Design - DDR4        |    |

| Chapter 7 Linux BSP                     |    |

| 7.1 Introduction                        |    |

| 7.2 Use Linux BSP                       |    |

| 7.3 Linux LXDE VNC Desktop BSP          |    |

| 7.4 Linux LXDE HDMI Desktop BSP         |    |

| 7.5 VNC Desktop OpenCL BSP              |    |

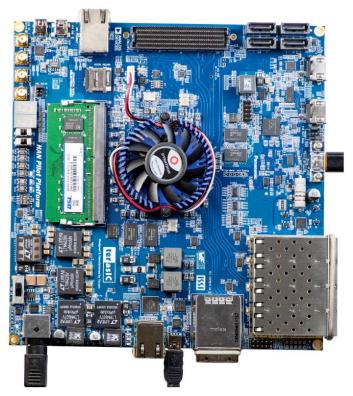

# Chapter 1

This manual will introduce the various application demonstrations on HAN Pilot Platform. These demonstrations cover most of the interfaces on HAN Pilot Platform. Let users familiarize using these interfaces of the HAN Pilot Platform. Demonstration according to FPGA and HPS Fabrics are divided into three categories:

- Pure use of FPGA fabric resources (Chapter 2)

- Pure use of HPS fabric resources (Chapter 3)

- Use both FPGA and HPS fabric resources (Chapter 4)

In addition, the PCIe example of HAN Pilot Platform will be described separately in one chapter (Chapter 5) because of its high content.

Finally, to complete the following demonstration, user needs to install the following software in the computer:

- Intel Quartus<sup>®</sup> Prime Design Software Version 18.1 or later.

- Intel SoC Embedded Design Suite (EDS)

# Chapter 2

# **Examples for FPGA**

This chapter provides examples of advance designs implemented by RTL or Qsys on the HAN Pilot Platform. These reference designs cover the features of peripherals connected to the FPGA, such as DDR4, PCIe, HDMI and USB Controller. All the associated files can be found in the directory \Demonstrations\FPGA of HAN Pilot Platform system CD.

### 2.1 Factory Default Code

The HAN Pilot Platform has a default configuration bit-stream pre-programmed, which demonstrates some of the basic features on board. This demo used LED,7-Segments, Switch, HDMI transmitter display and fan control.

#### ■ Function Block Diagram

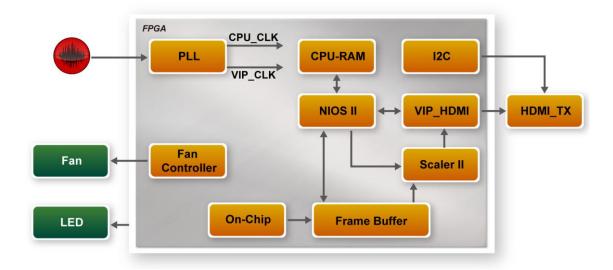

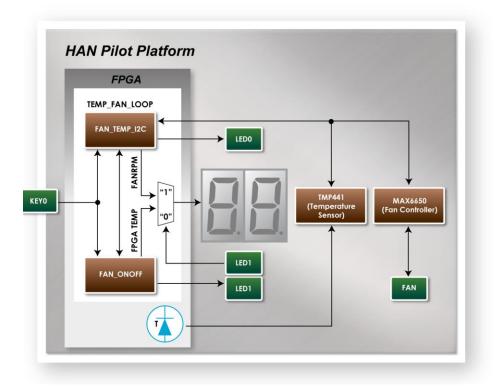

**Figure 2-1** shows the function block diagram of this demonstration. This demo used fan controller to control fan and used frame buffer read board picture from ON-CHIP-MEMORY and used scaler scale the picture to 1920x1080 size, display the picture by HDMI TX.

Figure 2-1 Block Diagram of Default Demonstration

#### Design Tools

- Quartus Prime 18.1.0 Standard Edition

- Demonstration Source Code:

- Project Directory: Demonstration\default\_code

- Bit Stream: default\_code.sof or default\_code.jic

- Demonstration Batch File: default\_code\demo\_batch or default\_code\demo\_run\_batch

NOTE: because the demo included software, and run on on-chip-memory, so use mem\_init can package elf to sof, so user can only program .sof or .sof and .elf to run demo.

The demo batch file includes following files:

- Batch File: test.bat

- FPGA Configuration File: default\_code.sof or default\_code.jic

#### **Demonstration Setup**

- 1. Make sure Quartus Prime is installed on the host PC.

- 2. Connect HAN Pilot Platform to the host PC via USB cable. Install the USB-Blaster II driver if necessary.

- 3. Connect the HDMI TX to displayer via HDMI cable.

- 4. Set MSEL[2:0] to 010, set SW0 to 0, SW1 to 0.

- 5. Power on the HAN Pilot Platform.

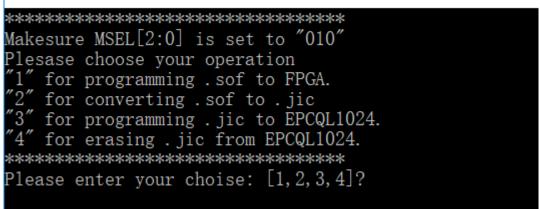

- 6. Execute the demo batch file "test.bat" under the batch file folder \ default\_code\demo\_batch. You will see the menu as shown in **Figure 2-2**.

- 7. Select your choice, and program FPGA or program flash.

- 8. When the demo is running, you can see the LED is blinking and flowing, and the displayer will display the board picture as shown in **Figure 2-3**.

C:\WINDOWS\system32\cmd.exe

#### Figure 2-2 Menu of Default Demonstration

**Figure 2-3 Board Picture of Default Demonstration**

# **2.2 Nios II Control for Programmable PLL/ Temperature/**

### **Power/ 9-axis**

This demonstration shows how to use the Nios II processor to program two programmable oscillators (CDCM6208 and TXC) on the FPGA board, how to measure the power consumption based on the built-in power measure circuit. The demonstration also includes a function of monitoring system temperature with the on-board temperature sensor, and 3-axis gyroscope, 3-axis accelerometer, and 3-axis magnetometer output with the on-board MPU-9250 Motion Tracking device.

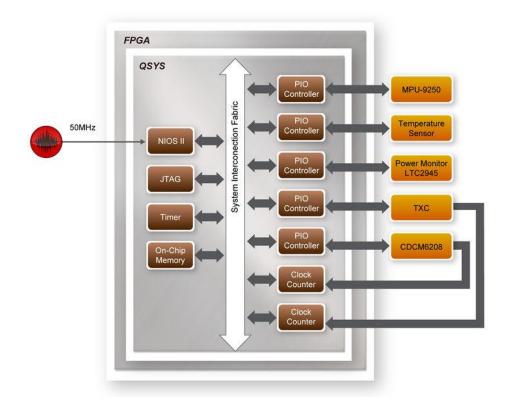

#### System Block Diagram

**Figure 2-4** shows the system block diagram of this demonstration. The system requires a 50 MHz clock provided from the board. The five peripherals (including temperature sensor, power monitor, CDCM6208, TXC, and MPU-9250) are all controlled by Nios II through the PIO controller, and all of them are programmed through I2C protocol which is implemented in the C code. The I2C pins from chip are connected to Qsys System Interconnect Fabric through PIO controllers. The Nios II program toggles the PIO controller to implement the I2C protocol. The Nios II program is running in the on-chip memory.

#### Figure 2-4 Block Diagram of the Nios II Basic Demonstration

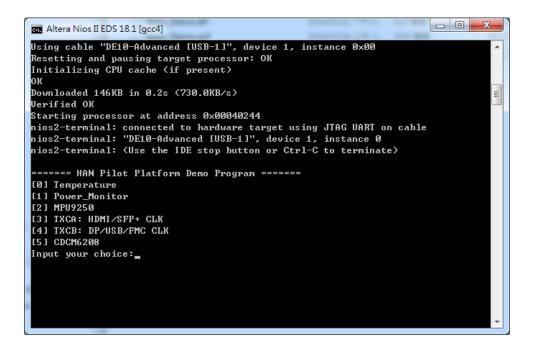

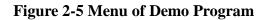

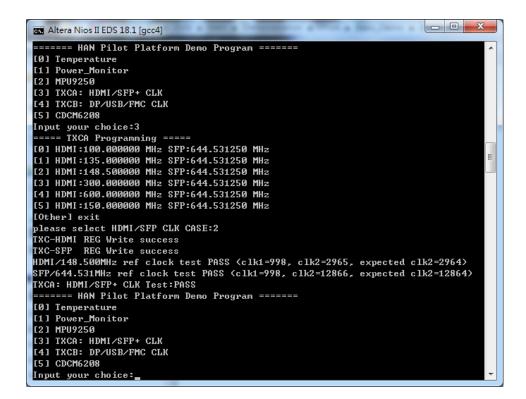

The program provides a menu in nios-terminal, as shown in **Figure 2-5** to provide an interactive interface. With the menu, users can perform the test for the temperature sensor, power monitor, external programmable PLL and 9-axis outputs. Note, pressing 'ENTER' should be followed with the choice number.

HAN Pilot Platform Demonstration Manual www.terasic.com October 8, 2019 In temperature test, the program will display local temperature and remote temperature. The remote temperature is the FPGA temperature, and the local temperature is the board temperature where the temperature sensor located.

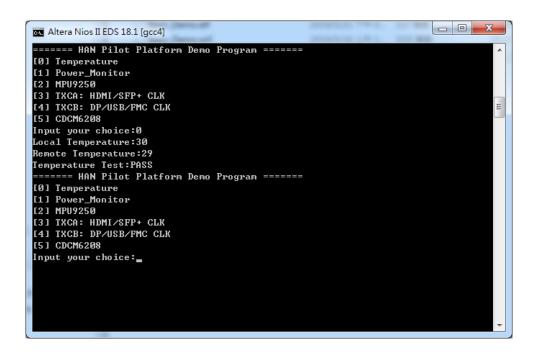

A power monitor IC (LTC2945) embedded on the board can monitor Arria10 real-time current and power. This IC can work out current/power value as multiplier and divider are embedded in it. There is a sense resistor R176 (0.006  $\Omega$ ) for LTC2945 in the circuit, when power on the HAN Pilot Platform, there will be a voltage drop (named  $\Delta$ SENSE Voltage) on R176. Based on sense resistors, the program of power monitor can calculate the associated voltage, current and power consumption from the LTC2945 through the I2C interface. Please note the device I2C address is 0xD4.

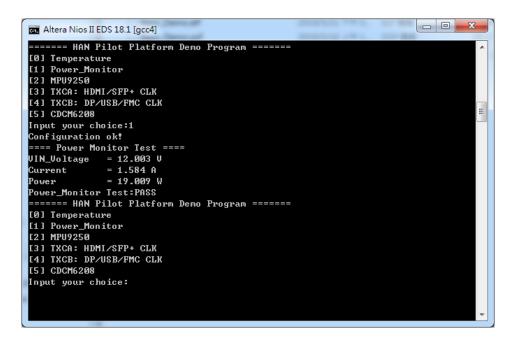

The MPU-9250 consists of two dies, one die houses the 3-axis gyroscope and 3-axis accelerometer, and the other die houses the a-axis magnetometer. Similarly, the MPU-9250 provides complete 9-axis output through the I2C interface.

In the external PLL programming test, the program will program the PLL first, and subsequently will use TERASIC QSYS custom CLOCK\_COUNTER IP to count the clock count in a specified period to check whether the output frequency is changed as configured. For CDCM6208 programming, the program can control the CDCM6208 to configure the output frequency of SATA/PCIE/DDR4A/DDR4B/DDR4H REFCLK according to your choice. Please note the device I2C address is 0xA8. For TXC programming, the program can control the TXC to configure the output frequency of HDMI/SFP+/FMC/DP/USB REFCLK according to your choice. There are five TXC's ICs for clock generator, divided into two group, TXCA and TXCB. The HDMI and SFP+ reference clock generators share the same I2C bus, REFCLK0\_SCL/REFCLK0\_SDA, and are grouped into TXCA. The FMC, DP, and USB reference clock generators also share the same I2C bus, REFCLK1\_SCL/REFCLK1\_SDA, and are grouped into TXCB.

#### Demonstration File Location

- Hardware project directory: Basic\_Demo

- Bitstream used: Basic\_Demo.sof

- Software project directory: Basic\_Demo \software

- Demo batch file: Basic\_Demo\demo\_batch\test.bat, test.sh

#### **Demonstration Setup and Instructions**

- 1. Make sure Quartus Prime is installed on the host PC.

- 2. Set MSEL[2:0] to 010

- 3. Power on the FPGA board.

- 4. Use the USB Cable to connect your PC and the FPGA board and install USB Blaster II driver if necessary.

- 5. Execute the demo batch file "test.bat" under the batch file folder: Basic\_Demo\demo\_batch.

- 6. After the Nios II program is downloaded and executed successfully, a prompt message will be displayed in nios2-terminal.

7. For temperature test, please input key '0' and press 'Enter' in the nios-terminal, as shown in **Figure 2-6**.

**Figure 2-6 Temperature Demo**

8. For power monitor test, please input key '1' and press 'Enter' in the nios-terminal, the Nios II console will display the values of voltage, current and power as shown in **Figure 2-7**.

**Figure 2-7 Power Monitor Demo**

9. For 9-axis test, please input key '2' and press 'Enter' in the nios-terminal, the Nios II console will display the values of 9-axis as shown in **Figure 2-8**.

HAN Pilot Platform Demonstration Manual

Figure 2-8 MPU-9250 Demo

For programmable PLL TXCA test, please input key '3' and press 'Enter' in the nios-terminal first, then select the desired output frequency of HDMI/SFP+ REFCLK, as shown in Figure 2-9.

Figure 2-9 TXCA Demo

11. For programmable PLL TXCB test, please input key '4' and press 'Enter' in the nios-terminal first, then select the desired output frequency of DP/USB/FMC REFCLK, as shown in **Figure 2-10**.

| 🖬 Altera Nios II EDS 18.1 [gcc4]                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------|

| ====== HAN Pilot Platform Demo Program =======                                                                             |

| [0] Temperature                                                                                                            |

| [1] Power_Monitor                                                                                                          |

| [2] MPU9250                                                                                                                |

| [3] TXCA: HDMI/SFP+ CLK                                                                                                    |

| [4] TXCB: DP/USB/FMC CLK                                                                                                   |

| [5] CDCM6208                                                                                                               |

| Input your choice:4                                                                                                        |

| ===== TXCB Programming =====                                                                                               |

| [0] DP:150.000000 MHz USB:150.000000 MHz FMC:150.000000 MHz                                                                |

| [1] DP:270.000000 MHz USB:270.000000 MHz FMC:270.000000 MHz<br>[2] DP:270.000000 MHz USB:270.000000 MHz FMC:297.000000 MHz |

| [3] DP:270.000000 MHz USB:644.531250 MHz FMC:100.000000 MHz                                                                |

| [4] DP:270.000000 MHz USB:644.531250 MHz FMC:125.000000 MHz                                                                |

| [5] DP:270.000000 MHz USB:644.531250 MHz FMC:150.000000 MHz                                                                |

| [6] DP:270.000000 MHz USB:644.531250 MHz FMC:644.531250 MHz                                                                |

| [Other] exit                                                                                                               |

| please select DP/USB/FMC CLK CASE:4                                                                                        |

| TXC-DP REG Write success                                                                                                   |

| TXC-USB REG Write success                                                                                                  |

| TXC-FMC REG Write success                                                                                                  |

| DP/270.000000MHz ref clock test PASS (clk1=999, clk2=5389, expected clk2=5394)                                             |

| USB/644.531250MHz ref clock test PASS (clk1=998, clk2=12863, expected clk2=12864                                           |

|                                                                                                                            |

| FMC/125.000000MHz ref clock test PASS (clk1=998, clk2=2495, expected clk2=2495)                                            |

| TXCB: DP/USB/FMC CLK Test:PASS                                                                                             |

| ======= HAN Pilot Platform Demo Program =======                                                                            |

| [0] Temperature                                                                                                            |

| [1] Power_Monitor                                                                                                          |

| [2] MPU9250                                                                                                                |

| [3] TXCA: HDMI/SFP+ CLK<br>[4] TXCB: DP/USB/FMC CLK                                                                        |

| IAI IXCB: DP/USB/FMC CLK<br>[5] CDCM6208                                                                                   |

| Input your choice:                                                                                                         |

|                                                                                                                            |

Figure 2-10 TXCB Demo

12. For programmable PLL CDCM6208 test, please input key '5' and press 'Enter' in the nios-terminal first, then select the desired output frequency of SATA/ PCIE/ DDR4A/ DDR4B/ DDR4H REFCLK, as shown in Figure 2-11.

| Altera Nios II EDS 18.1 [gcc4]              | the summer because of    |                                  | x  |

|---------------------------------------------|--------------------------|----------------------------------|----|

| ====== HAN Pilot Platfor                    | rm Demo Program ======   |                                  |    |

| [0] Temperature                             |                          |                                  |    |

| 1] Power_Monitor                            |                          |                                  |    |

| 21 MPU9250                                  |                          |                                  |    |

| 31 TXCA: HDMI/SFP+ CLK                      |                          |                                  |    |

| 41 TXCB: DP/USB/FMC CLK                     |                          |                                  |    |

| 51 CDCM6208                                 |                          |                                  |    |

| nput your choice:5                          |                          |                                  |    |

| ==== CDCM6208 Programmin                    | ng =====                 |                                  |    |

| 0] SATA_DEVICE:150.000 N                    | MHz SATA_HOST:150.000 MH | Hz OB_PCIE:100.000 MHz           |    |

|                                             | 266.666 MHz DDR4H:266.66 |                                  |    |

| 1] SATA_DEVICE:150.000 N                    |                          |                                  |    |

|                                             | 133.333 MHz DDR4H:133.33 | 33 MHz                           |    |

| Other] exit                                 |                          |                                  |    |

| lease select CLK CASE:0                     |                          |                                  |    |

| DCM6208 REG Write succes                    | 55                       |                                  |    |

| EAD CDCM6208                                |                          |                                  |    |

| eg[0]-reg[20] read and v                    |                          |                                  |    |

|                                             | ef clock test PASS (clk1 | 1=998, clk2=2995, expected clk2= | =2 |

| 94)                                         |                          |                                  |    |

|                                             | clock test PASS (clk1=9  | 998, clk2=2995, expected clk2=29 | 9  |

| •)<br>• • • • • • • • • • • • • • • • • • • |                          |                                  |    |

|                                             |                          | clk2=1996, expected clk2=1996)   |    |

|                                             |                          | c1k2=5323, expected c1k2=5322)   |    |

|                                             |                          | c1k2=5322, expected c1k2=5322)   |    |

|                                             | ck test PASS (clk1=998,  | c1k2=5323, expected c1k2=5322)   |    |

| DCM6208 Test:PASS                           |                          |                                  |    |

| ====== HAN Pilot Platfor                    | rm Demo Program ======   |                                  |    |

| 0] Temperature                              |                          |                                  |    |

| 1] Power_Monitor                            |                          |                                  |    |

| 2] MPU9250<br>3] TXCA: HDMI/SFP+ CLK        |                          |                                  |    |

| 4] TXCH: HDM1/SFP+ CLK                      |                          |                                  |    |

| .4.1 TXCB: DP/USB/FMC CLR<br>[5.1 CDCM6208  |                          |                                  |    |

| ISI GDGM6208<br>(nput your choice:_         |                          |                                  |    |

HAN Pilot Platform Demonstration Manual www.terasic.com October 8, 2019

# 2.3 Nios DDR4 SDRAM Test

Many applications use a high performance RAM, such as a DDR4 SDRAM, to provide temporary storage. In this demonstration hardware and software designs are provided to illustrate how to perform DDR4 memory access in QSYS. We describe how the Altera's "Arria 10 External Memory Interfaces" IP is used to access the two DDR4-Sodimm on the FPGA board, and how the Nios II processor is used to read and write the SDRAM for hardware verification. The DDR4 SDRAM controller handles the complex aspects of using DDR4 SDRAM by initializing the memory devices, managing SDRAM banks, and keeping the devices refreshed at appropriate intervals.

#### System Block Diagram

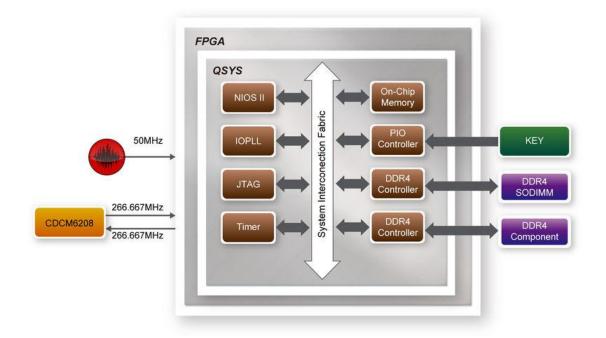

**Figure 2-12** shows the system block diagram of this demonstration. The QSYS system requires one 50 MHz and two 266.667MHz clock source. The two 266.667 MHz clock source is provided by CDCM6208 clock generator on the board. The 50MHz is used by IO PLL to generate 200MHz for Nios Processor and On-chip Memory. The two 266.667MHz clock are used as reference clocks for the DDR4 controllers. There are two DDR4 Controllers are used in the demonstrations. Each controller is responsible for one DDR4 SDRAM. Each DDR4 controller is configured as a 1 GB DDR4-1066MHz controller. The DDR4A controllers are designed as 1GB rather 4GB is due to address space limitation of Nios II processor. Nios II processor is used to perform memory test. The Nios II program is running in the On-Chip Memory. A PIO Controller is used to monitor buttons status which is used to trigger starting memory testing.

#### Figure 2-12 Block Diagram of the DDR4 Basic Demonstration

The system flow is controlled by a Nios II program. First, the Nios II program writes test patterns into the whole 1 GB of SDRAM. Then, it calls Nios II system function (alt\_dache\_flush\_all) to make sure all data has been written to SDRAM. Finally, it reads data from SDRAM for data

HAN Pilot Platform Demonstration Manual verification. The program will show progress in JTAG-Terminal when writing/reading data to/from the SDRAM. When verification process is completed, the result is displayed in the JTAG-Terminal.

#### Design Tools

- Quartus Prime 18.1.0 Standard Edition

- Nios II Software Build Tools for Eclipse 18.1

#### Demonstration Source Code

- Quartus Project directory: NIOS\_DDR4

- Nios II Eclipse: NIOS\_DDR4 \software

- Nios II Project Compilation

#### Nios II Project Compilation

Before you attempt to compile the reference design under Nios II Eclipse, make sure the project is cleaned first by clicking 'Clean' from the 'Project' menu of Nios II Eclipse.

#### **Demonstration Batch File**

Demo Batch File Folder: NIOS\_DDR4 \demo\_batch The demo batch file includes following files:

- Batch File for USB-Blaster II: test.bat, test.sh

- FPGA Configure File: NIOS\_DDR4.sof

- Nios II Program: DDR4\_Test.elf

#### Demonstration Setup

Please follow below procedures to setup the demonstration.

- 1. Make sure Quartus Prime and Nios II are installed on your PC.

- 2. Make sure DDR4 SODIMM are installed on the FPGA board.

- 3. Set MSEL[2:0] to  $010_{\circ}$

- 4. Power on the FPGA board.

- 5. Use USB Cable to connect PC and the FPGA board and install USB Blaster II driver if necessary.

- 6. Execute the demo batch file "test.bat" under the folder "NIOS\_DDR4\demo\_batch".

- 7. After Nios II program is downloaded and executed successfully, a prompt message will be displayed in nios2-terminal.

- 8. Press Key0~Key1 of the FPGA board to start SDRAM verify process. Press Key0 for continued test.

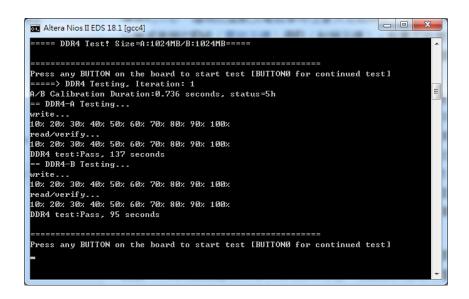

- 9. The program will display progressing and result information, as shown in Figure 2-13.

Figure 2-13 Progress and Result Information for the DDR4 Demonstration

### 2.4 RTL DDR4 SDRAM Test

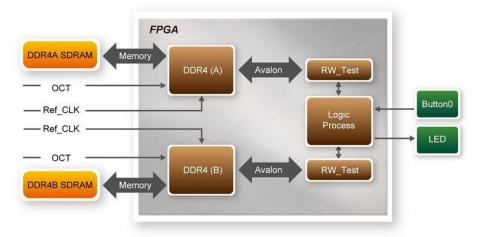

This demonstration performs a memory test function on the one DDR4 SO-DIMM (DDR4A) and one DDR4 Component (DDR4B) on the HAN Pilot Platform. The memory size of DDR4 SO-DIMM is 4GB and DDR4 Component is 1GB.

#### ■ Function Block Diagram

**Figure 2-14** shows the function block diagram of this demonstration. There are two DDR4 SDRAM controllers. The controller uses 266.667 MHz as a reference clock. It generates one 1066MHz clock as memory clock from the FPGA to the memory and the controller itself runs at quarter-rate in the FPGA i.e. 266.667 MHz.

Figure 2-14 Block Diagram of DDR4 x2 Demonstration

#### Design Tools

- Quartus Prime 18.1.0 Standard Edition

- Demonstration Source Code:

HAN Pilot Platform Demonstration Manual

- Project Directory: Demonstration\RTL DDR4 •

- Bit Stream: RTL DDR4.sof

#### **Demonstration Batch File**

Demo Batch File Folder: RTL DDR4 \demo batch The demo batch file includes following files:

- Batch File: test.bat

- FPGA Configuration File: RTL DDR4.sof

#### **Demonstration Setup**

- 1. Make sure Quartus Prime is installed on the host PC.

- 2. Connect HAN Pilot Platform to the host PC via USB cable. Install the USB-Blaster II driver if necessary.

- 3. Set MSEL[2:0] to  $010_{\circ}$

- 4. Power on the HAN Pilot Platform.

- 5. Execute the demo batch file "test.bat" under the batch file folder \ RTL\_DDR4\demo\_batch.

- 6. Press KEY0 on HAN Pilot Platform to start the verification process. When KEY0 is released, LED0, LED1 should start blinking. After approximately 2 seconds, LED1 and LED2 should stop blinking and stay on to indicate the DDR4 (A) and DDR4 (B) have passed the test, respectively. Table 2-1 lists the LED indicators.

- 7. If LED0 or LED1 does not start blinking upon releasing KEY0, it indicates local\_cal\_success of the corresponding DDR4 fails.

- 8. If LED0 or LED1 fail to remain on after 2 seconds, the corresponding DDR4 test has failed.

- 9. Press KEY0 again to regenerate the test control signals for a repeat test.

| Table 2-1 LED Indicators |                      |  |

|--------------------------|----------------------|--|

| Name                     | Description          |  |

| LED0                     | DDR4 (A) test result |  |

| LED1                     | DDR4 (B) test result |  |

#### Table 2-1 LED Indicators

# 2.5 USB Type-C DisplayPort Alternate Mode

This section introduces how to implement a DisplayPort Source based on USB Type-C DisplayPort Alternate Mode. The demo includes two major parts: DisplayPort and USB Type-C.

For DisplayPort design, DisplayPort Intel FPGA IP is used to generate DisplayPort TX video. The DisplayPort design is refer to the document :Arria 10 DisplayPort Design Example using on board connector (TX Only).

For USB Type-C, system need to monitor the information sent from the USB Type-C Port Controller CYPD3125 (EZ-PD CCG3). From the sent information, system can know whether the plug-in device is a DisplayPort monitor and the DP lane number is 4 or 2, and system have to configure the DisplayPort crossbar switch so the FPGA transceiver signals can be routed to the

type-c port correctly.

The Quartus Project USBC\_DP\_4K is designed for 4K monitor, and USBC\_DP\_FullHD is design for Full HD Monitor. If your Type-C monitor only supports Full HD, please use the USB\_DP\_FullHD for the demo setup.

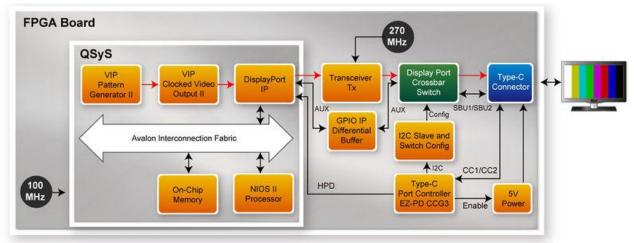

#### System Block Diagram

**Figure 2-15** shows the system block diagram for the DisplayPort Demo. When a Type-C monitor is plugged into the Type-C Connector, the Type-C Port Controller (EZ-PD CCG3) will enable 5V power for the monitor. When a Type-C device is plug-in or removed from the Type-C connector, the CCG3 will notify FPGA through the IC2 interface. CCG3 will sends one byte data to 0 offset address in the I2C Slave Port. The meaning of the data is shown in **Table 2-2**. If attached device is a DisplayPort monitor, then DisplayPort crossbar switch is configured so the transceivers signals are routed to the type-c connector correctly.

For DisplayPort design, the Hot Plug Detect (HPD) causes the DisplayPort source to initialize the link via AUX channel. The DisplayPort IP generates parallel Video data and FPGA transceivers are used to serial the video data. For 4K video data, 4 TX transceivers are used with reference clock 270 MHz. For Full HD video data, 4 or 2 TX transceivers are used. The input video data for DisplayPort IP is generated by VIP Test Pattern Generator II IP and VIP Clocked Video Output II IP.

In the system, a Nios II processor is used to control the DisplayPort IP. The Nios II Processor is running on on-chip memory with 100Mhz.

Figure 2-15 Block Diagram of DisplayPort Demo

| Data[6:5] | Description                                    |  |

|-----------|------------------------------------------------|--|

| 0         | No Device is attached                          |  |

| 1         | Only USB 3.1 Device is attached                |  |

| 2         | 4 Lane DisplayPort monitor is attached         |  |

| 3         | USB and 2 Lane DisplayPort monitor is attached |  |

#### Table 2-2 Information sent by CCG3

| Data[4] | Description     |

|---------|-----------------|

| 0       | Cable is normal |

| 1       | Cable is flip   |

#### **Demonstration** File Locations

- For 4K Video Output:

- Hardware project directory: USBC\_DP\_4K

- Bitstream used: USBC\_DP\_golden\_top.sof

- Nios II Program: dp\_demo\_test.elf

- Demo batch file: USBC\_DP\_4K\demo\_batch\test.bat

- For Full-HD Video Output:

- Hardware project directory: USBC\_DP\_FullHD

- Bitstream used: USBC\_DP.sof.sof

- Nios II Program: dp\_demo\_test.elf

- Demo batch file: USBC\_DP\_FullHD\demo\_batch\test.bat

#### Demonstration Setup and Instructions

- 1. Make sure Quartus Prime is installed on your PC.

- 2. Set MSEL[2:0] to  $010_{\circ}$

- 3. Power on the FPGA board.

- 4. Use the Mini USB Cable to connect your PC and the FPGA board and install USB Blaster II driver if necessary.

- 5. Execute test.bat under the demo\_batch folder.

- 6. Connect USB Type-C Connector (J2) to a 4K Type-C Monitor (or Full HD Type-C Monitor) via a Type-C Cable.

- 7. You will see a color bar pattern on the Type-C Monitor.

# 2.6 USB Type-C FX3 Loopback

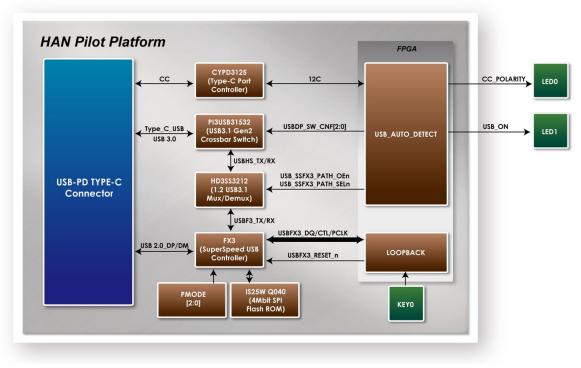

This demonstration illustrates how the FX3 is working with the FPGA for USB3.0/USB2.0 data bulk in/out (data loop transmission). There is a USB type-C connector onto HAN Pilot Platform, a type-C cable is reversible for plugging in the USB type-C connector. This demonstration also implements the auto-switching mechanism for a type-C cable plugging in on either side.

#### Function Block Diagram

**Figure 2-16** shows the function block diagram of the USBC\_FX3 demonstration. This design comprises two parts, USB3.0/USB2.0 TX&RX crossbar switch controlling and FX3 data transferring. As the Type-C connector is reversible, a Type-C port Controller (CYPD3125) is required for USB3.0/USB2.0 TX&RX crossbar switch controlling. When the Type-C cable is

plugged in, the CC (Configuration Channel) signal is communicating with the controller. The controller then transfers the data to the Slave IC (FPGA) by I2C in Master mode, and There will be a salve I2C module in the FPGA to decode the signal and send the control signal to control the RX/TX direction of the PI3USB31532 USB3.0 signal. Here is a LED0 on the board to indicate the cable plugging direction, and LED1 indicates whether there is a USB connection signal or not. For the data transmission of FX3 module, FIFO and controller (implemented in the FPGA) combine FX3 module to perform the data bulk in/out loop. (For details, please refer to CYPRESS AN65974 Designing with the EZ-USB<sup>®</sup> FX3<sup>™</sup> Slave FIFO Interface Chapter 11). All modules functions are described below:

**USB\_AUTO\_DETECT**: This module can decode the I2C signal from the Type-C Port Controller (CYPD3125 IC), then timely switch the RX/TX direction of Type-C port (by controlling the PI3USB31532 IC) and control the USB 3.0 Mux/Demux9 (HD3SS3212) switching to transfer the USB 3.0 signal to FX3 module. As shown in Figure 4-1, the LED0 indicates the Type-C connector RX/TX direction, the LED1 indicates the USB 3.0 signal input.

**LOOPBACK**: This module is designed as FX3 Slave FIFO Interface, the module combines the CYPRESS application(bulkloop.exe) to implement data bulk in/out loop demo.

**KEY0**: It is used to reset FX3 module.

**PMODE[2:0]**: The HAN Pilot Platform has a 4Mbits Flash ROM, which can be used to program the FX3 firmware. This ROM is connected to FX3 through SPI interface. PMODE[2:0] is used to set the FX3 in program or boot status. The setting details is described in below steps.

Figure 2-16 Block diagram of the USBC FX3 design

#### Demonstration Setup

• Hardware Setting Up, as shown in **Figure 2-17**.

Figure 2-17 USBC FX3 Demo Hardware Setting Up

- Design Tools

- Quartus Prime 18.1 Standard Edition

- Demonstration Source Code

- Quartus project directory: USBC\_FX3

- Bitstream used: USBC\_FX3.sof

- Demonstration Batch File

- Demo batch file folder: demonstrations $USBC_FX3$ demo\_batch

- Demonstration Setup

- Connect the HAN Pilot Platform USB Blaster II connector (J20) to the host PC with a USB cable and install the USB-Blaster II driver if necessary.

- Use a Type-C cable to connect the HAN Pilot Platform and a PC (with a Type-C connector). As shown in **Figure 2-17**.

- Plug the 12V adapter to HAN Pilot Platform DC 12V power connector (J28).

- Set MSEL[2:0] to 010.

- Power on the HAN Pilot Platform.

- Execute the demo batch file "test.bat" from the directory \FPGA\USBC\_FX3\demo\_batch.

- Install the FX3 driver: the driver for Windows 7 is in the  $\ FPGA\ USBC_FX3\ demo_batch\ Driver\ win7$  folder, and the driver for Windows 10 is in the  $\ FPGA\ USBC_FX3\ demo_batch\ Driver\ win10$  folder.

- Use JP6, JP5, JP4 to set the PMODE[2:0] as "0F1" (F indicates floating).

- Press KEY0 (RESET FX3).

- Re-plug the Type-C cable one time, Cypress Control Center will show Cypress FX3 USB Streamer Example Device and BOS (SuperSpeed Device capability), it indicates the USB3.0 Has completed the setup. When LED1 lights up, it indicates USB signal is detected. LED0 lights off indicates Type-C Cable two sides plugged with same directions,

LED0 lights up indicates Type-C Cable two sides plugged with reverse directions.

• Execute the .exe application: \demo\_batch\Host\_app\loopback\bulkloop.exe, see **Figure 2-18** below, press Start, you will see the Bytes Transferred IN/Out value increasing rapidly. For more information of bulkloop.exe, please refer to Cypress EZ-USB FX3 SDK Getting Started with FX3 SDK.

| Connected Devices   | (0x04B4 - 0x00F1) Cypre   | ess FX3 USB StreamerExample De | evice |

|---------------------|---------------------------|--------------------------------|-------|

|                     | Select Endpoint Pai       | r (IN & OUT)                   |       |

| IN Endpoints        | BULK IN, AltInt - 0 and E | pAddr - 0x81                   | -     |

| OUT Endpoints       | BULK OUT, AltInt - 0 and  | EpAddr - 0x01                  | •     |

|                     | Data Pattern to           | OUTPUT                         |       |

|                     |                           | O Constant Byte                |       |

| 🔘 Random Data B     | Byte                      | Incrementing Bytes             |       |

| Kanuoin Data t      |                           |                                |       |

| C. Kandom Data t    |                           | Incrementing 32 bits INTEG     | GER   |

| Kanoon Data t       | Constant / Start Value    | Incrementing 32 bits INTEC     | GER.  |

| Bytes Transferred O |                           |                                | GER.  |

Figure 2-18 FX3 bulk in out bulkloop

Table 2-3 summarizes the functional keys and details of each LED status.

| Name | Description                                                          |

|------|----------------------------------------------------------------------|

| LED0 | LED0 lights off indicates Type-C Cable two sides plugged with same   |

|      | directions.                                                          |

|      | LED0 lights up indicates Type-C Cable two sides plugged with reverse |

|      | directions.                                                          |

| LED1 | It lights up when the USB signal is detected.                        |

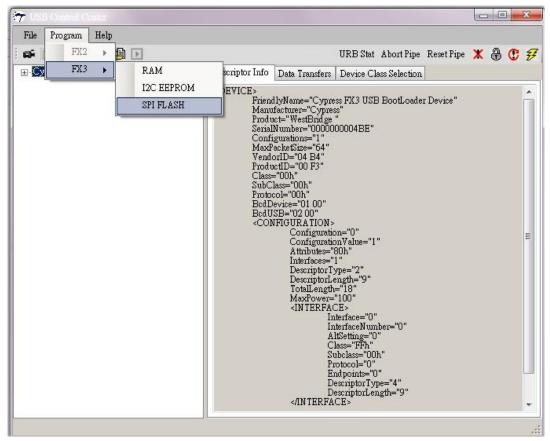

- Program the FX3 firmware:(Optional)

- Execute the demo batch file "test.bat" from the directory  $\FPGA\USBC_FX3\demo\_batch$

- Execute Cypress Control: FPGA\USBC\_FX3\demo\_batch\Host\_app\ download\_firmware\CyControl.exe

- Use JP6, JP5, JP4 to set the PMODE[2:0] as "F11"(F indicates floating).

- Press KEY0 (RESET FX3), Cypress Control center will show Cypress FX3 USB Bootloader Device.

- Program software, In Control Center. Click Program FX3 SPI FLASH, as shown in Figure 2-19. Select file FPGA\USBC\_FX3\demo\_batch\FX3\_Firmware\SF\_loopback.img. Wait until It reports "Programming of SPI FLASH Succeeded".

**Figure 2-19 Cypress Control Center**

# 2.7 HDMI TX and RX in 4K Resolution

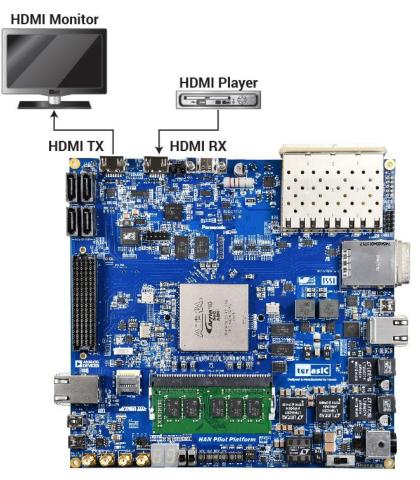

This demonstration uses the Intel® FPGA HDMI IP core to implement the HDMI Retransmit function in the FPGA of the HAN Pilot Platform. As shown in **Figure 2-20**, user can connect an HDMI video player to the input video and audio data to HDMI RX port of the HAN Pilot Platform. After the HDMI video data is received in the FPGA, it will be instantly transferred to the HDMI TX port. The user only needs to connect an HDMI screen to the HAN Pilot Platform. User only needs to connect an HDMI screen to the HAN Pilot Platform. User only needs to connect an HDMI screen to the HAN Pilot Platform. User only needs to connect an HDMI screen to the HAN Pilot Platform. User only needs to connect an HDMI screen to the HAN Pilot Platform, then you can watch the images output by the HDMI Player. This demonstration supports image resolution up to **4K@60YUV** mode. User who need resolution with **4K@60RGB** mode, please use the project in the folder "HDMI\_RX\_TX\_192" and use Quartus 19.2 version to open and edit it. If you want to learn HDMI high-performance related image processing, this demo can help you learn quickly.

Figure 2-20 The Architecture of the demonstration

#### System Block Diagram

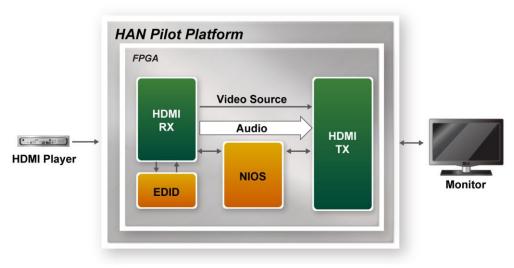

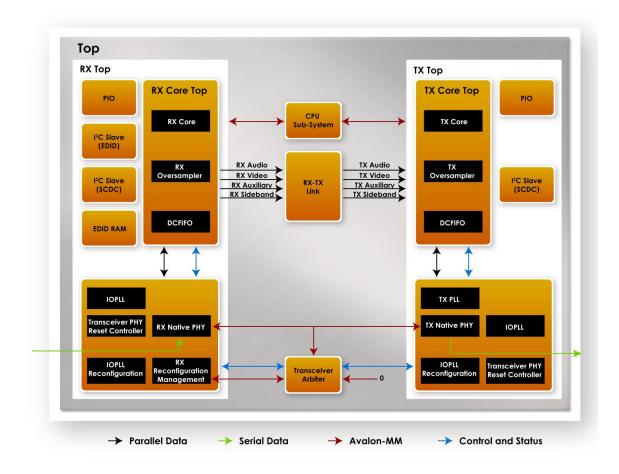

**Figure 2-21** shows the system block diagram of this example. It shows that the Intel® FPGA HDMI IP core is used in the FPGA. It is divided into two parts: Transmitter and Receiver. These two IPs can be directly used by Transition-minimized differential signaling (TMDS) interface connection, only need HDMI repeater or redrive IC as an intermediary to connect HDMI devices, no need to use special HDMI Transmitter and Receiver IC. For details about HDMI IP, please refer to HDMI Intel® FPGA IP User Guide and Intel FPGA HDMI Design Example User Guide for Intel Arria 10 Devices.

Figure 2-21 The system block of the demonstration

This demonstration first needs to connect the HAN Pilot Platform to the HDMI interface screen. Because this demo can support various screen resolutions. When the HAN Pilot Platform connect to the monitor, the HDMI RX block in the FPGA will first read the supporting resolution of the monitor from the it's EDID and stored in the EDID RAM in the HDMI RX block. The NIOS handles the control signals between the EDID and the HDMI IP in this demo.

The HDMI Video player is then connected to the HDMI RX port of the HAN Pilot Platform. When the RX instance in the FPGA receives a video source from the external video generator, the video and audio data then go through a loopback FIFO before it is transmitted to the TX instance. The final image and sound data will be displayed on the monitor connected to the TX end. For a more detailed IP block diagram in the example, refer to Figure 2-22.

Figure 2-22 The HDMI IP block of the demonstration

#### ■ Demonstration Source Code for 4K@60YUV

$Project \ Location: \ System \ CD \ Demonstration \ FPGA \ HDMI_RX_TX \ \$

- Quartus Project directory: HDMI\_RX\_TX\quartus\

- Nios II Eclipse: HDMI\_RX\_TX\software\

- Demonstration Batch File:

Demo Batch File Folder: HDMI\_RX\_TX\demo\_batch\ The demo batch file includes following files:

- Batch File for USB-Blaster II: test.bat, test.sh

- FPGA Configure File: a10\_hdmi2\_demo.sof

- Nios II Program: HDMI\_RX\_TX.elf

#### Demonstration Source Code for 4K@60RGB

Project Location: System CD\Demonstration\FPGA\HDMI\_RX\_TX\_192

- Quartus Project directory: HDMI\_RX\_TX\_192\quartus\

- Nios II Eclipse: HDMI\_RX\_TX\_192\software\

• Demonstration Batch File:

Demo Batch File Folder: HDMI\_RX\_TX\_192\demo\_batch\ The demo batch file includes following files:

- Batch File for USB-Blaster II: test.bat, test.sh

- FPGA Configure File: a10\_hdmi2\_demo.sof

- Nios II Program: HDMI\_RX\_TX.elf

#### ■ Hardware Requirement

- A PC

- An HDMI monitor capable of displaying 4K/60P

- An HDMI video player capable of outputting 4K/60P resolution

#### **Demonstration Setup**

- 1. Make sure Quartus Prime and Nios II are installed on your PC.

- 2. Set MSEL[2:0] to 010, Set SW0 to 1, SW1 to 0.

- 3. Connect a HDMI monitor to the HAN Pilot Platform as shown in Figure 2-23.

#### Figure 2-23 Connection setup of the HDMI TX monitor and HAN Pilot Platform

- 4. Connect the USB Blaster II port on the HAN Pilot Platform to the computer using the USB cable (Do not connect the HDMI video player at this time).

- 5. Open HAN Pilot Platform power and execute demo batch file: test.bat

- 6. Waiting for FPGA code download completed.

- 7. First set the output resolution of the HDMI video player to 4K@60Hz and connect to the HDMI RX port of HAN Pilot Platform as shown in **Figure 2-20**.

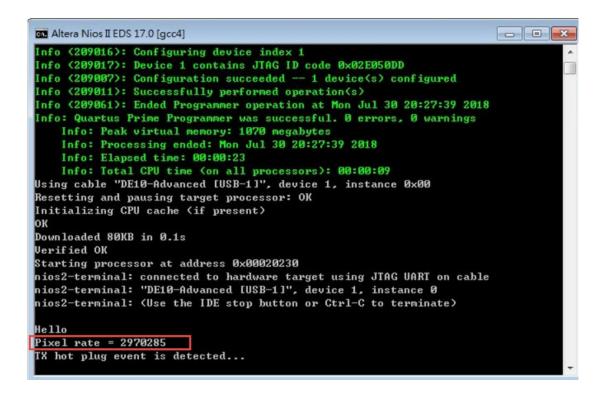

- 8. Observe the Nios command shell window (See Figure 2-24), whether the Pixel rate is around 297000 (the value when the resolution is 4K).

- 9. Check if the resolution of the HDMI monitor is 4K/60P. If the monitor cannot support 4K resolution, some HDMI video players will automatically switch to full HD or lower resolution. If the HDMI video player cannot automatically switch, please manually switch to the resolution that monitor can support.

Figure 2-24 Verify the pixel rate of the demonstration

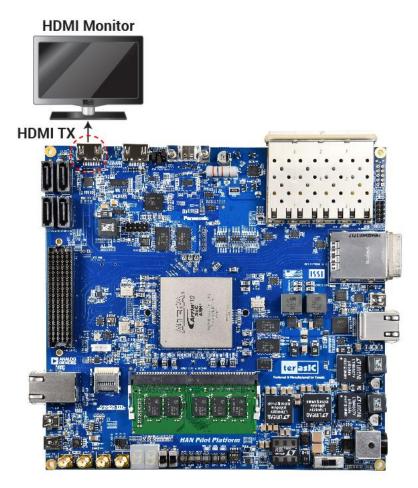

# 2.8 HDMI TX in 4K Resolution

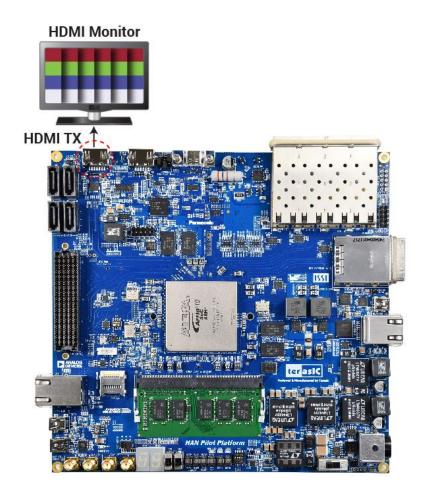

Compared with the section 2.7 HDMI TX and RX in 4K Resolution, the difference of this demonstration is that only the TX of the Intel® FPGA HDMI IP cores is used in the FPGA. This demo also has a video test pattern generator built into the FPGA. The highest resolution 4K image is sent to the HDMI TX IP. It is displayed via an external HDMI monitor.

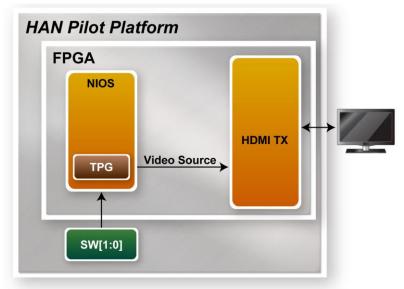

#### System Block Diagram

HAN Pilot Platform Demonstration Manual www.terasic.com October 8, 2019 **Figure 2-25** shows the system block diagram of the demo. First, Nios is used to generate the test pattern output to the HDMI TX IP. The resolution of the generated pattern can be 4K or Full HD (1080). User can switch the output resolution instantly through the Switch on the HAN Pilot Platform. The HDMI TX IP is identical to section 2.7.

Figure 2-25 The System Block Diagram of the demonstration

#### Design Tools

- Quartus Prime 18.1.0 Standard Edition

- Nios II Software Build Tools for Eclipse 18.1

#### Demonstration Source Code

$Project \ Location: \ System \ CD \ Demonstration \ FPGA \ HDMI_TX_4K \ \$

- Quartus Project directory: HDMI\_TX\_4K

- Nios II Eclipse: HDMI\_TX\_4K\software\

- Demonstration Batch File:

#

The demo batch file includes following files:

- Batch File for USB-Blaster II: test.bat, test.sh

- FPGA Configure File: HDMI\_TX\_4K.sof

- Nios II Program: vip\_control.elf

#### Hardware Requirement

- A PC

- An HDMI monitor capable of displaying 4K/60P

#### Demonstration Setup

- 1. Make sure Quartus Prime and Nios II are installed on your PC.

- 2. Connect a HDMI monitor to the HAN Pilot Platform as shown in Figure 2-23.

- 3. Connect the USB Blaster II port on the HAN Pilot Platform to the computer using the USB cable (do not connect the HDMI video player at this time).

- 4. Set MSEL[2:0] to 010.

- 5. Open HAN Pilot Platform power and execute demo batch file: test.bat

- 6. Waiting for FPGA code download completed

- 7. Check if the test color pattern is shown on the HDMI monitor (See Figure 2-26).

Figure 2-26 Test color pattern is shown on the HDMI monitor

8. User can switch SW[1:0] to change the resolution of the test patter output. The relationship between the detailed screen resolution and the switch is shown in Table 2-4.

| <b></b> |                                       |

|---------|---------------------------------------|

| SW[1:0] | Resolution Setting                    |

| 00      | 1080@60P                              |

| 01      | 4K@60P                                |

| 10      | 1080@60P (Same with the SW[1:0] = 00) |

| 11      | 4K@30P                                |

Table 2-4 Switch setting for the resolution of the test pattern

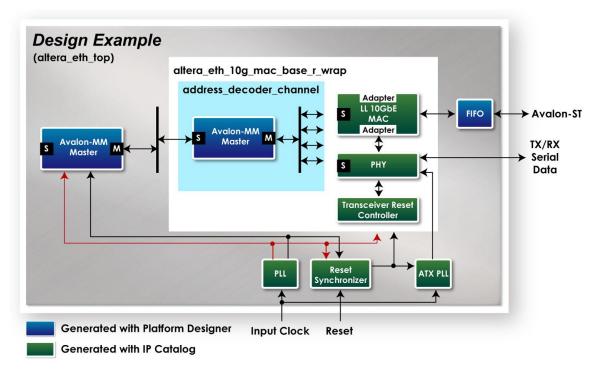

# 2.9 Low Latency Ethernet 10G MAC Demo

This 10GBASE-R Ethernet design example is generated according to the documents : Low Latency Ethernet 10G MAC Intel Arria 10 FPGA IP Design Example User Guide. The LL (Low Latency) 10GbE IP is used in the example design. This example executes the external loopback test through one of the SFP+ ports on the FPGA main board. A SFP+ loopback fixture is required to perform this demonstration. **Figure 2-27** shows the block diagram of this demonstration.

#### Figure 2-27 Block diagram of 10GBASE-R demo

#### Project Information

The Project information is shown in the Table 2-5.

Table 2-5 Project Information

| Item                | Description                                                      |

|---------------------|------------------------------------------------------------------|

| Project<br>Location | CDROM/Demonstration/FPGA/alt_eth                                 |

| FPGA Bit<br>Stream  | CDROM/Demonstration/FPGA/alt_eth/output_files/altera_eth_top.sof |

|                     | CDROM/Demonstration/FPGA/alt_eth/hwtesting/system_console/       |

| Test Scrip<br>File  | gen_conf.tcl<br>monitor_conf.tcl                                 |

|                     | show_stats.tcl                                                   |

#### **Demonstration Setup**

Here is the procedure to setup the demonstration. A SFP+ loopback fixture is required for this demonstration.

1. Insert a SFP+ loopback fixture into the SFP+-A port on the HAN Pilot Platform as shown in **Figure 2-28**.

Figure 2-28 SFP+-A loopback on the HAN Pilot Platform

- 2. Connect the host PC to the FPGA board using a Mini-USB cable. Please make sure the USB-Blaster II driver is installed on the host PC.

- 3. Set MSEL[2:0] to 010.

- 4. Power on the FPGA Board.

- 5. Using Quartus to open the quartus project "altera\_eth\_top.qpf".

- 6. Execute the demo batch file "test.bat" under the batch file folder, alt\_eth\demo\_batch.

- 7. Launch the System Console by selecting the menu item "Tools=>System Debugging

HAN Pilot Platform Demonstration Manual www.terasic.com October 8, 2019 Tools=>System Console" in Quartus.

- 8. In the Tcl Console pane, type "cd hwtesting/system\_console" to change directory to the folder: ./alt\_eth/hwtesting/system\_console as shown in Figure 2-29.

- Type "source gen\_conf.tcl" to generates and sends about 4 billion packets as shown in Figure 2-30.

- 10. Type "source monitor\_conf.tcl" to checks the number of good and bad packets received. as shown in **Figure 2-31**.

- 11. Type "source show\_stats.tcl" to checks the number of good and bad packets received. as shown in **Figure 2-32**.

- 12. Wait 6 minutes to complete loopback task, then re-type "source monitor\_conf.tcl" to see "0xffff2000" good packets.

| 🖀 System Console - Toolkits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |                                                                                                                      |                  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|--|

| File Tools Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              |                                                                                                                      |                  |  |  |  |  |

| System Explorer 🗖                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |                                                                                                                      |                  |  |  |  |  |

| ↓ /<br>i ···· ·······························                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADC Toolkit (Beta)                                                                                                                           |                                                                                                                      |                  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | The ADC Toolkit allows for the evaluation of ADC signal path performance.                                                                    |                                                                                                                      |                  |  |  |  |  |

| 🗄 🄑 designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No associated hardware detected.                                                                                                             |                                                                                                                      |                  |  |  |  |  |

| instances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NO associated hardware detected.                                                                                                             |                                                                                                                      |                  |  |  |  |  |

| a anto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |                                                                                                                      |                  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bus Analyzer (Beta)                                                                                                                          |                                                                                                                      |                  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | The Bus Analyzer provides real-time performance analysis of bus traffic in the system.                                                       |                                                                                                                      |                  |  |  |  |  |

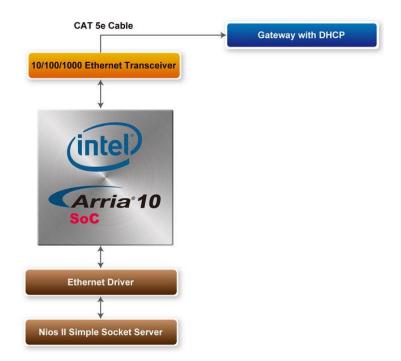

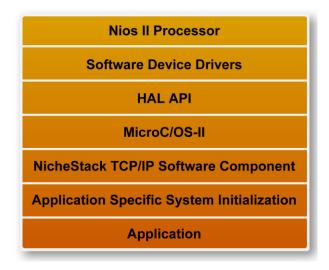

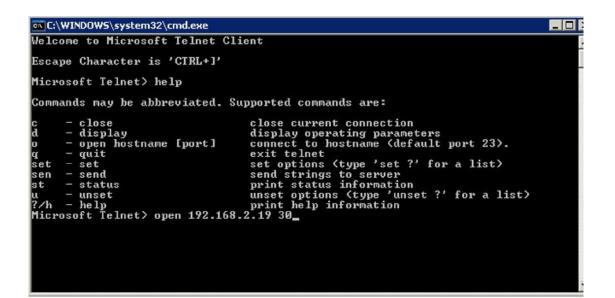

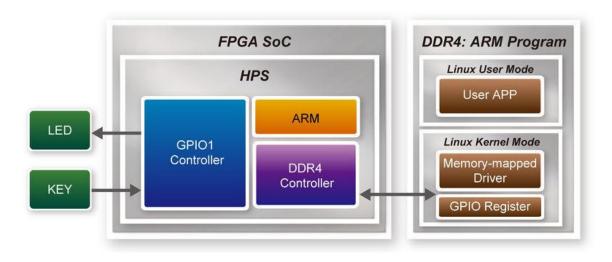

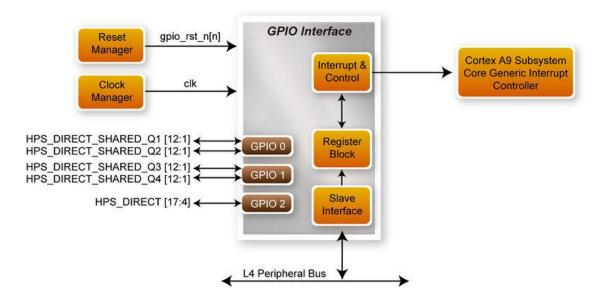

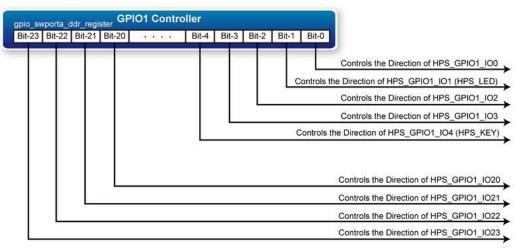

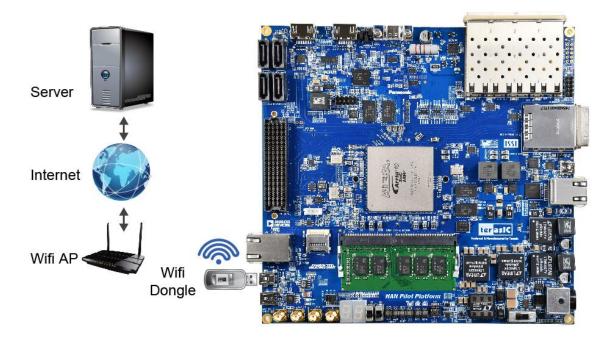

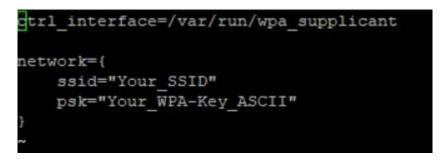

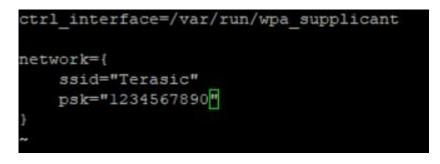

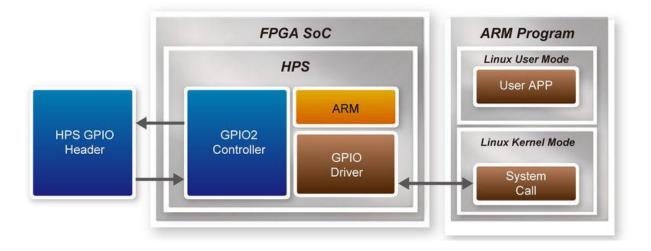

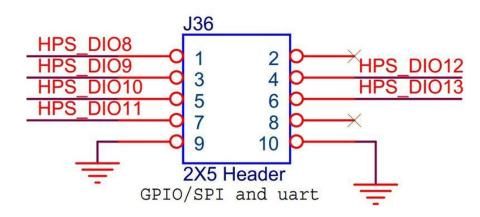

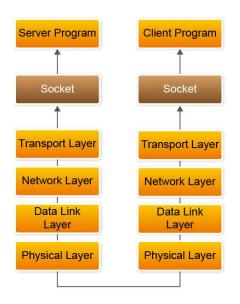

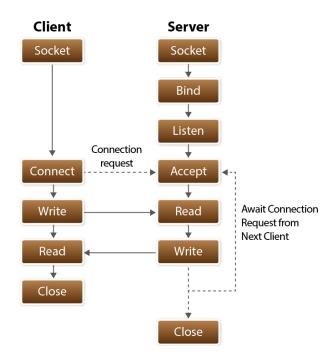

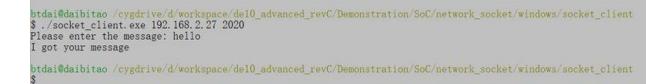

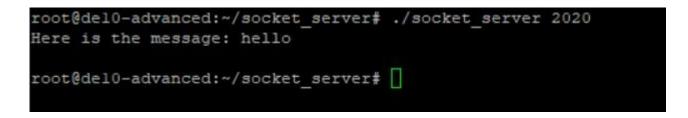

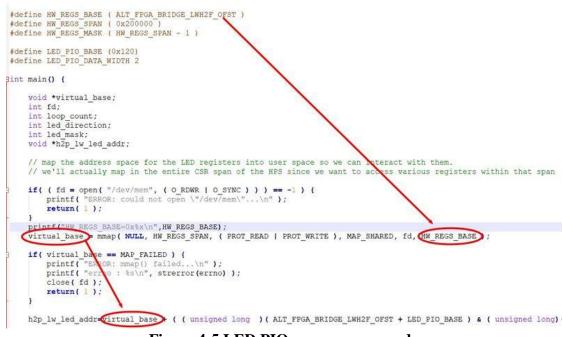

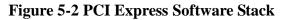

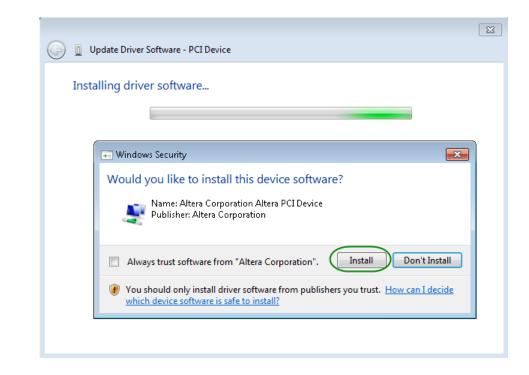

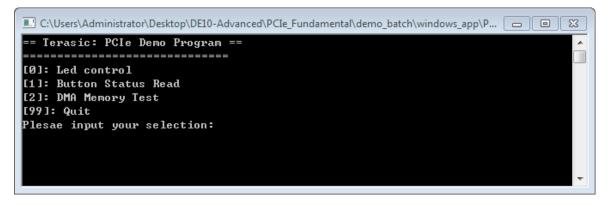

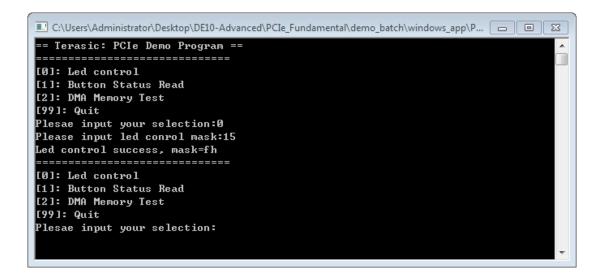

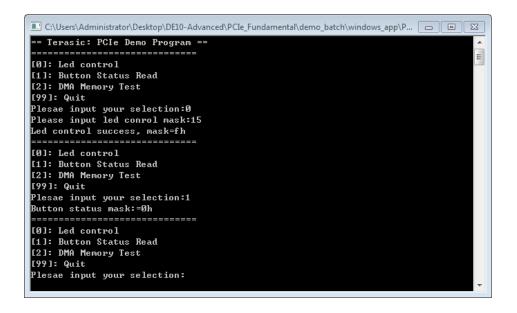

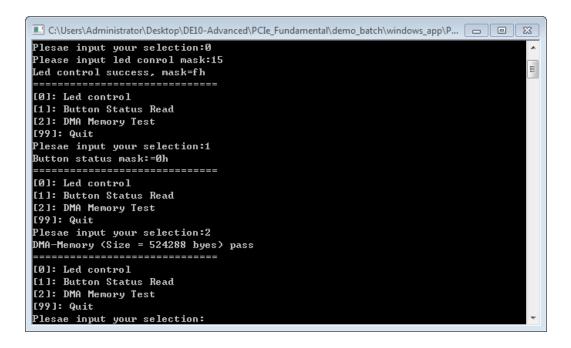

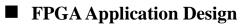

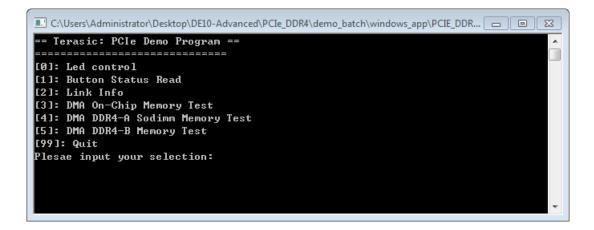

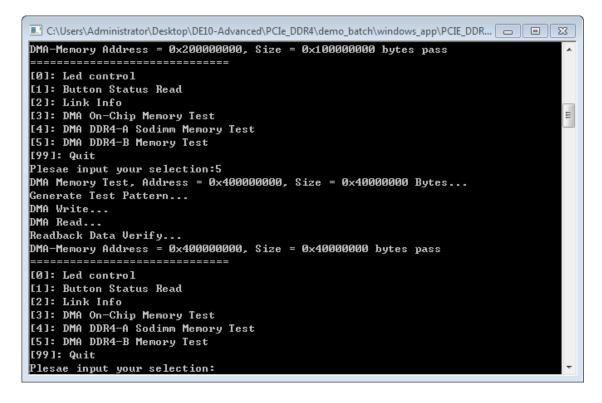

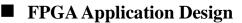

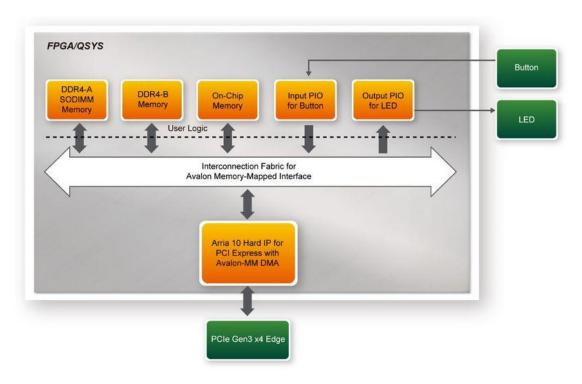

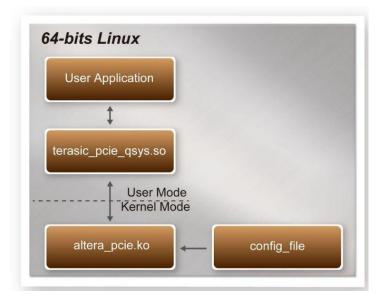

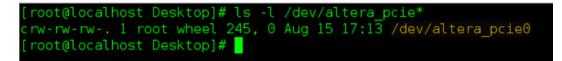

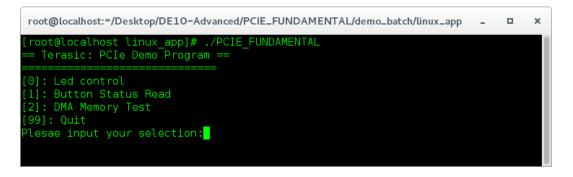

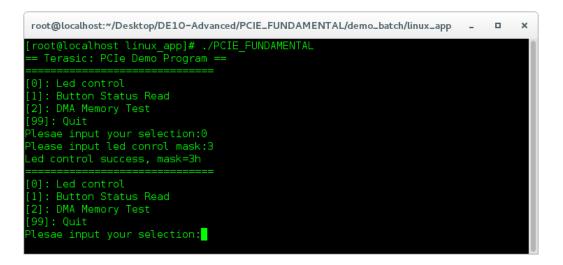

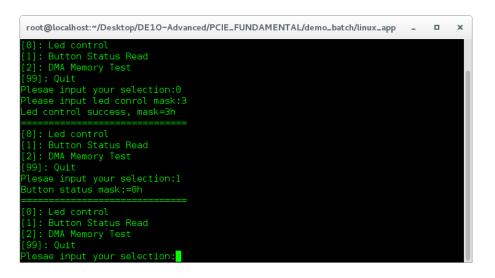

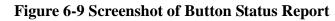

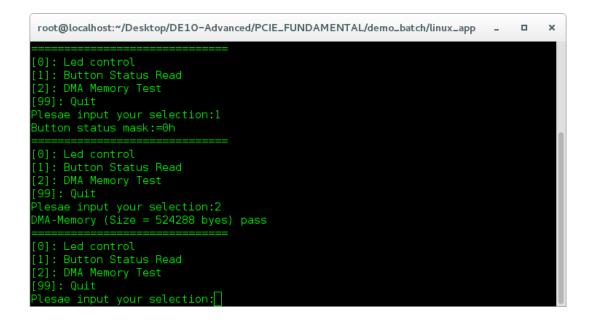

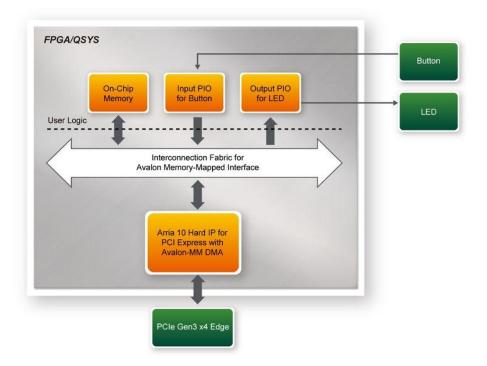

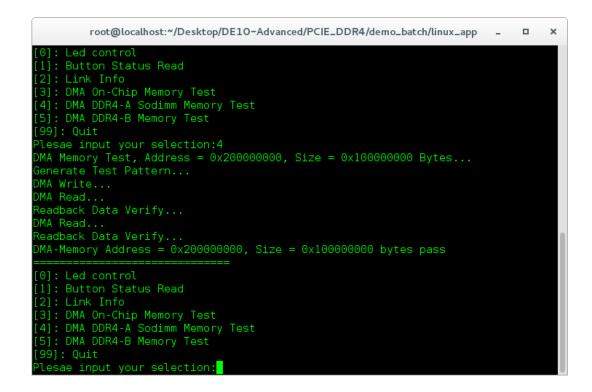

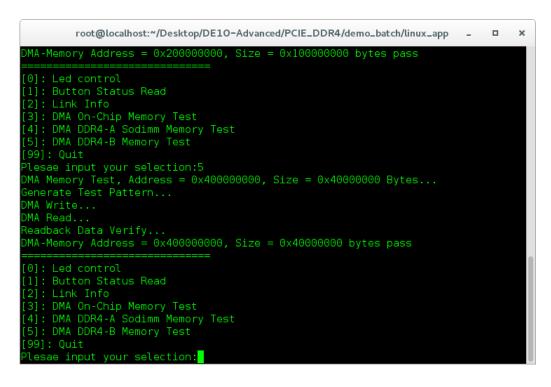

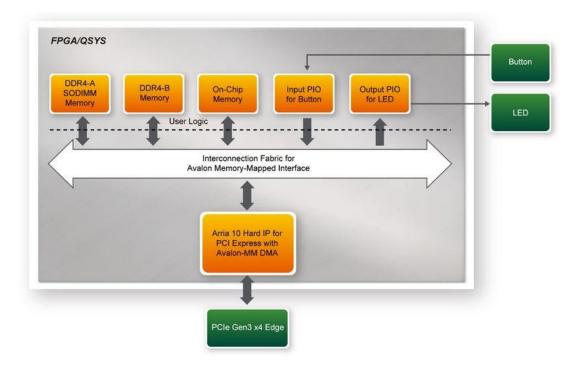

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              |                                                                                                                      |                  |  |  |  |  |