# Nexys4™ FPGA Board Reference Manual

Revised September 6, 2013 This manual applies to the Nexys4 rev. B

### **Overview**

The Nexys4 board is a complete, ready-to-use digital circuit development platform based on the latest Artix-7™ Field Programmable Gate Array (FPGA) from Xilinx. With its large, high-capacity FPGA (Xilinx part number XC7A100T-1CSG324C), generous external memories, and collection of USB, Ethernet, and other ports, the Nexys4 can host designs ranging from introductory combinational circuits to powerful embedded processors. Several built-in peripherals, including an accelerometer, temperature sensor, MEMs digital microphone, speaker amplifier and lots of I/O devices allow the Nexys4 to be used for a wide range of designs without needing any other components.

The Artix-7 FPGA is optimized for high performance logic, and offers more capacity, higher performance, and more resources than earlier designs. Artix-7 100T features include:

- 15,850 logic slices, each with four 6-input LUTs and 8 flip-flops

- 4,860 Kbits of fast block RAM

- Six clock management tiles, each with phase-locked loop (PLL)

- 240 DSP slices

- Internal clock speeds exceeding 450MHz

- On-chip analog-to-digital converter (XADC)

The Nexys4 also offers an improved collection of ports and peripherals, including:

- USB-UART Bridge

- 12-bit VGA output

- 3-axis accelerometer

- 16Mbyte CellularRAM

- Pmod for XADC signals

- 16 user LEDs

- Two tri-color LEDs

- PWM audio output

- Temperature sensor

- Serial Flash

- Digilent Adept USB port for programming and data

- Micro SD card connector

- PDM microphone

- 10/100 Ethernet PHY

- Four Pmod ports

- USB HID Host for mice, keyboards and memory sticks

The Nexys4 is compatible with Xilinx's new high-performance Vivado Design Suite as well as the ISE toolset, which includes ChipScope and EDK. Xilinx offers free "Webpack" versions of these toolsets, so designs can be implemented for no additional cost.

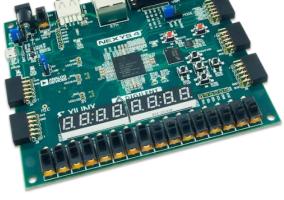

| Callout | Component Description                    | Callout | Component Description                |

|---------|------------------------------------------|---------|--------------------------------------|

| 1       | Power select jumper and battery header   | 13      | FPGA configuration reset button      |

| 2       | Adept USB (JTAG and UART)                | 14      | CPU reset button (for soft cores)    |

| 3       | External configuration jumper (SD / USB) | 15      | Analog signal Pmod connector (XADC)  |

| 4       | Pmod connector(s)                        | 16      | Programming mode jumper              |

| 5       | Microphone                               | 17      | Audio connector                      |

| 6       | Power supply test point(s)               | 18      | VGA connector                        |

| 7       | LEDs (16)                                | 19      | FPGA programming done LED            |

| 8       | Slide switches                           | 20      | Ethernet connector                   |

| 9       | Eight digit 7-seg display                | 21      | USB host connector                   |

| 10      | JTAG port for (optional) external cable  | 22      | PIC24 programming port (factory use) |

| 11      | Five pushbuttons                         | 23      | Power switch                         |

| 12      | Temperature sensor                       | 24      | Power jack                           |

#### 1. Nexys4 board features

A growing collection of board support IP, reference designs, and add-on boards are available on the Digilent website. See the Nexys4 page at <a href="https://www.digilentinc.com">www.digilentinc.com</a> for more information.

# 1 Power Supplies

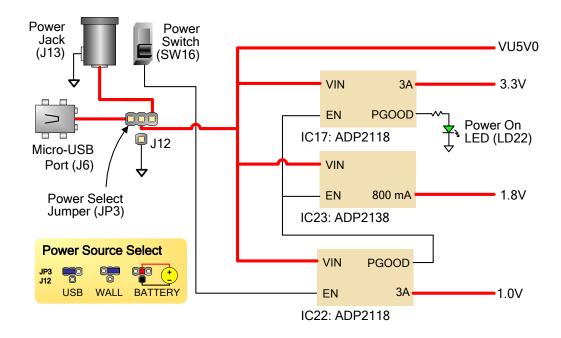

The Nexys4 board can receive power from the Digilent USB-JTAG port (J6) or from an external power supply. Jumper JP3 (near the power jack) determines which source is used.

All Nexys4 power supplies can be turned on and off by a single logic-level power switch (SW16). A power-good LED (LD22), driven by the "power good" output of the ADP2118 supply, indicates that the supplies are turned on and operating normally. An overview of the Nexys4 power circuit is shown in Figure 2.

Figure 2. Nexys4 Power Circuit

The USB port can deliver enough power for the vast majority of designs. A few demanding applications, including any that drive multiple peripheral boards, might require more power than the USB port can provide. Also some applications may need to run without being connected to a PC's USB port. In these instances an external power supply or battery pack can be used.

An external power supply can be used by plugging into to the power jack (JP3) and setting jumper J13 to "wall". The supply must use a coax, center-positive 2.1mm internal-diameter plug, and deliver 4.5VDC to 5.5VDC and at least 1A of current (i.e., at least 5W of power). Many suitable supplies can be purchased through Digikey or other catalog vendors.

An external battery pack can be used by connecting the battery's positive terminal to the center pin of JP3 and the negative terminal to the pin labeled J12 directly below JP3. Since the main regulator on the Nexys4 cannot accommodate input voltages over 5.5VDC, an external battery pack must be limited to 5.5VDC. The minimum voltage of the battery pack depends on the application - if the USB Host function (J5) is used, at least 4.6V need to be provided. In other cases the minimum voltage is 3.6V.

Voltage regulator circuits from Analog Devices create the required 3.3V, 1.8V, and 1.0V supplies from the main power input. **Error! Reference source not found.** provides additional information (typical currents depend strongly n FPGA configuration and the values provided are typical of medium size/speed designs).

Voltage regulator circuits from Analog Devices create the required 3.3V, 1.8V, and 1.0V supplies from the main power input. **Error! Reference source not found.** provides additional information (typical currents depend strongly n FPGA configuration and the values provided are typical of medium size/speed designs).

| Supply | Circuits                                                                      | Device        | Current (max/typical) |

|--------|-------------------------------------------------------------------------------|---------------|-----------------------|

| 3.3V   | FPGA I/O, USB ports, Clocks,<br>RAM I/O, Ethernet, SD slot,<br>Sensors, Flash | IC17: ADP2118 | 3A/0.1 to 1.5A        |

| 1.0V   | FPGA Core                                                                     | IC22: ADP2118 | 3A/ 0.2 to 1.3A       |

| 1.8V   | FPGA Auxiliary and Ram                                                        | IC23: ADP2138 | 800mA/ 0.05 to 0.15A  |

Table 2. Nexys4 Power Supplies

# 2 FPGA Configuration

After power-on, the Artix-7 FPGA must be configured (or programmed) before it can perform any functions. You can configure the FPGA in one of four ways:

- 1. A PC can use the Digilent USB-JTAG circuitry (portJ6, labeled "PROG") to program the FPGA any time the power is on

- 2. A file stored in the nonvolatile serial (SPI) flash device can be transferred to the FPGA using the SPI port.

- 3. A programming file can be transferred to the FPGA from a micro SD card.

- 4. A programming file can be transferred from a USB memory stick attached to the USB HID port.

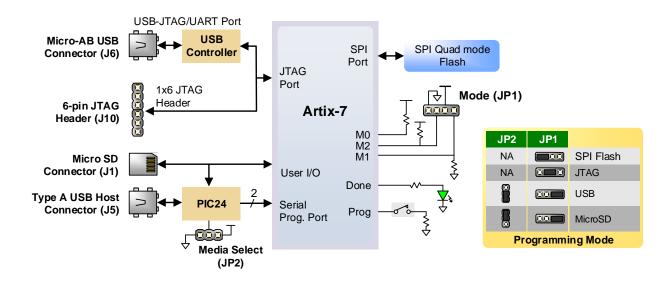

Figure 3 Shows the different options available for configuring the FPGA. An on-board "mode" jumper (JP1) and a media selection jumper (JP2) select between the programming modes.

Figure 3. Nexys4 Configuration Options

The FPGA configuration data is stored in files called bitstreams that have the .bit file extension. The ISE or Vivado software from Xilinx can create bitstreams from VHDL, Verilog, or schematic-based source files (in the ISE toolset, EDK is used for MicroBlaze™ embedded processor-based designs).

Bitstreams are stored in SRAM-based memory cells within the FPGA. This data defines the FPGA's logic functions and circuit connections, and it remains valid until it is erased by removing board power, by pressing the reset button attached to the PROG input, or by writing a new configuration file using the JTAG port.

An Artix-7 100T bitstream is typically 30,606,304 bits and can take a long time to transfer. The time it takes to program the Nexys4 can be decreased by compressing the bitstream before programming, and then allowing the FPGA to decompress the bitsream itself during configuration. Depending on design complexity, compression ratios of 10x can be achieved. Bitstream compression can be enabled within the Xilinx tools (ISE or Vivado) to occur during generation. For instructions on how to do this, consult the Xilinx documentation for the toolset being used.

After being successfully programmed, the FPGA will cause the "DONE" LED to illuminate. Pressing the "PROG" button at any time will reset the configuration memory in the FPGA. After being reset, the FPGA will immediately attempt to reprogram itself from whatever method has been selected by the programming mode jumpers.

The following sections provide greater detail about programming the Nexys4 using the different methods available.

### 2.1 JTAG Programming

The Xilinx tools typically communicate with FPGAs using the Test Access Port and Boundary-Scan Architecture, commonly referred to as JTAG. During JTAG programming, a .bit file is transferred from the PC to the FPGA using the onboard Digilent USB-JTAG circuitry (port J6) or an external JTAG programmer, such as the Digilent JTAG-HS2, attached to port J10. You can perform JTAG programming any time after the Nexys4 has been powered on, regardless of what the mode jumper (JP1) is set to. If the FPGA is already configured, then the existing configuration is overwritten with the bitstream being transmitted over JTAG. Setting the mode jumper to the JTAG setting (seen in Error! Reference source not found.) is useful to prevent the FPGA from being configured from any ther bitstream source until a JTAG programming occurs.

Programming the Nexys4 with an uncompressed bitstream using the on-board USB\_JTAG circuitry usually takes around five seconds.

JTAG programming can be done using the hardware server in Vivado or the iMPACT tool included with ISE and the labtools version of Vivado.

The demonstration project available at digilentinc.com gives an in depth tutorials on how to program your board.

# 2.2 Quad-SPI Programming

When programming a nonvolatile flash device, a bitstream file is transferred to the flash in a two-step process. First, the FPGA is programmed with a circuit that can program flash devices, and then data is transferred to the flash device via the FPGA circuit (this complexity is hidden from the user by the Xilinx tools). After the flash device has been programmed, it can automatically configure the FPGA at a subsequent power-on or reset event as determined by the mode jumper setting (see **Error! Reference source not found.**). Programming files stored in the lash device will remain until they are overwritten, regardless of power-cycle events.

Programming the flash can take as long as four to five minutes, which is mostly due to the lengthy erase process inherent to the memory technology. Once written however, FPGA configuration can be very fast, less than a second. Bitstream compression, SPI bus width, and configuration rate are factors controlled by the Xilnx tools that can affect configuration speed.

Quad-SPI programming can be done using the iMPACT tool included with ISE or the labtools version of Vivado.

### 2.3 USB Host and Micro SD Programming

You can program the FPGA from a pen drive attached to the USB-HID port (J5) or a microSD card inserted into J1 by doing the following:

- 1. Format the storage device (Pen drive or microSD card) with a FAT32 file system.

- 2. Place a single .bit configuration file in the root directory of the storage device.

- 3. Attach the storage device to the Nexys4.

- 4. Set the JP1 Programming Mode jumper on the Nexys4 to "USB/SD".

- 5. Select the desired storage device using JP2.

- 6. Push the PROG button or power-cycle the Nexys4.

The FPGA will automatically configure with the .bit file on the selected storage device. Any .bit files that are not built for the proper Artix-7 device will be rejected by the FPGA.

The Auxiliary Function Status or "BUSY" LED gives visual feedback on the state of the configuration process when the FPGA is not yet programmed:

- When steadily lit the auxiliary microcontroller is either booting up or currently reading the configuration medium (microSD or pen drive) and downloading a bitstream to the FPGA.

- A slow pulse means the microcontroller is waiting for a configuration medium to be plugged in.

- In case of an error during configuration the LED will blink rapidly.

When the FPGA is has been successfully configured, the behavior of the LED is application-specific. For example, if a USB keyboard is plugged in, a rapid blink will signal the receipt of an HID input report from the keyboard.

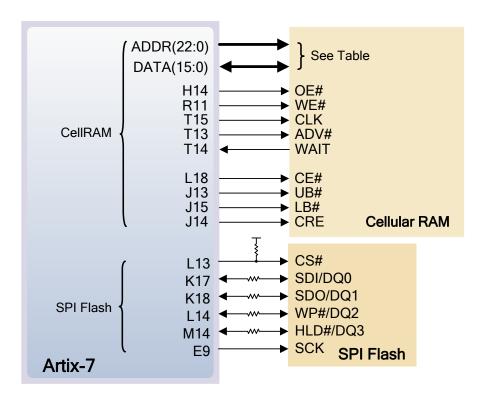

# 3 Memory

The Nexys4 board contains two external memories: a 128Mbit Cellular RAM (pseudo-static DRAM) and a 128Mbit non-volatile serial Flash device. The Cellular RAM has an SRAM interface, and the serial Flash is on a dedicated quad-mode (x4) SPI bus. The connections and pin assignments between the FPGA and external memories are shown in Figure 4 and Table 3.

The 16Mbyte Cellular RAM (Micron part number M45W8MW16) has a 16-bit bus that supports 8 or 16 bit data access. It can operate as a typical asynchronous SRAM with read and write cycle times of 70ns, or as a synchronous memory with a 104MHz bus. When operated as an asynchronous SRAM, the Cellular RAM automatically refreshes its internal DRAM arrays, allowing for a simplified memory controller (similar to any SRAM controller). When operated in synchronous mode, continuous transfers of up to 104MHz are possible.

FPGA configuration files can be written to the Quad SPI Flash (Spansion part number S25FL128S), and mode settings are available to cause the FPGA to automatically read a configuration from this device at power on. An

Artix-7 100T configuration file requires just under four Mbytes of memory, leaving about 77% of the flash device available for user data.

NOTE: Refer to the manufacturer's data sheets and the reference designs posted on Digilent's website for more information about the memory devices.

Figure 4. Nexys4 External Memories

| Address Bus |             |            | Data Bus    |            |

|-------------|-------------|------------|-------------|------------|

| ADDR22: U13 | ADDR13: U16 | ADDR4: H16 | DATA15: P17 | DATA6: T18 |

| ADDR21: M16 | ADDR12: P14 | ADDR3: J17 | DATA14: N17 | DATA5: R17 |

| ADDR20: T10 | ADDR11: V12 | ADDR2: H15 | DATA13: P18 | DATA4: U18 |

| ADDR19: U17 | ADDR10: V14 | ADDR1: H17 | DATA12: M17 | DATA3: R13 |

| ADDR18: V17 | ADDR9: U14  | ADDR0: J18 | DATA11: M18 | DATA2: U12 |

| ADDR17: M13 | ADDR8: V16  |            | DATA10: G17 | DATA1: T11 |

| ADDR16: N16 | ADDR7: N15  |            | DATA9: G18  | DATA0: R12 |

| ADDR15: N14 | ADDR6: K13  |            | DATA8: F18  |            |

| ADDR14: R15 | ADDR5: K15  |            | DATA7: R18  |            |

Table 3. CellRAM Address and Data Bus Pin Assignments

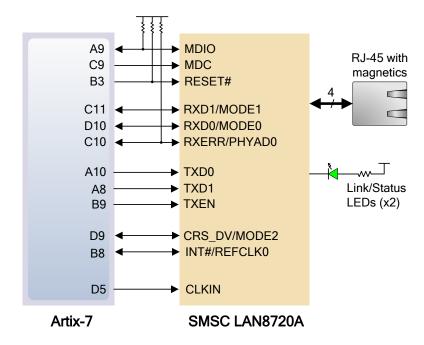

### **4 Ethernet PHY**

The Nexys4 board includes an SMSC 10/100 Ethernet PHY (SMSC part number LAN8720A) paired with an RJ-45 Ethernet jack with integrated magnetics. The SMSC PHY uses the RMII interface and supports 10/100 Mb/s. Figure 5 illustrates the pin connections between the Artix-7 and the Ethernet PHY. At power-on reset, the PHY is set to the following defaults:

- RMII mode interface

- Auto-negotiation enabled, advertising all 10/100 mode capable

- PHY address=00001

Two on-board LEDs (LD23 = LED2, LD24 = LED1) connected to the PHY provide link status and data activity feedback. See the PHY datasheet for details.

EDK-based designs can access the PHY using either the axi\_ethernetlite (AXI EthernetLite) IP core or the axi\_ethernet (Tri Mode Ethernet MAC) IP core. A mii\_to\_rmii core (Ethernet PHY MII to Reduced MII) needs to be inserted to convert the MAC interface from MII to RMII. Also a 50 MHz clock needs to be generated for the mii\_to\_rmii core and the CLKIN pin of the external PHY. To account for skew introduced by the mii\_to\_rmii core, generate each clock individually, with the external PHY clock having a 45 degree phase shift relative to the mii\_to\_rmii Ref\_Clk. An EDK demonstration project that properly uses the Ethernet PHY can be found on the Nexys4 product page at <a href="https://www.digilentinc.com">www.digilentinc.com</a>.

ISE designs can use the IP Core Generator wizard to create an Ethernet MAC controller IP core.

NOTE: Refer to the LAN8720A data sheet on the www.smsc.com website for further information.

Figure 5. Pin connections between the Artix-7 and the Ethernet PHY

### 5 Oscillators/Clocks

The Nexys4 board includes a single 100MHz crystal oscillator connected to pin E3 (E3 is a MRCC input on bank 35). The input clock can drive MMCMs or PLLs to generate clocks of various frequencies and with known phase relationships that may be needed throughout a design. Some rules restrict which MMCMs and PLLs may be driven by the 100MHz input clock. For a full description of these rules and of the capabilities of the Artix-7 clocking resources, refer to the "7 Series FPGAs Clocking Resources User Guide" available from Xilinx.

Xilinx offers the Clocking Wizard IP core to help users generate the different clocks required for a specific design. This wizard will properly instantiate the needed MMCMs and PLLs based on the desired frequencies and phase relationships specified by the user. The wizard will then output an easy to use wrapper component around these clocking resources that can be inserted into the user's design. The clocking wizard can be accessed from within the Project Navigator or Core Generator tools.

# 6 USB-UART Bridge (Serial Port)

The Nexys4 includes an FTDI FT2232HQ USB-UART bridge (attached to connector J6) that lets you use PC applications to communicate with the board using standard Windows COM port commands. Free USB-COM port drivers, available from www.ftdichip.com under the "Virtual Com Port" or VCP heading, convert USB packets to UART/serial port data. Serial port data is exchanged with the FPGA using a two-wire serial port (TXD/RXD) and optional hardware flow control (RTS/CTS). After the drivers are installed, I/O commands can be used from the PC directed to the COM port to produce serial data traffic on the C4 and D4 FPGA pins.

Two on-board status LEDs provide visual feedback on traffic flowing through the port: the transmit LED (LD20) and the receive LED (LD19). Signal names that imply direction are from the point-of-view of the DTE (Data Terminal Equipment), in this case the PC.

The FT2232HQ is also used as the controller for the Digilent USB-JTAG circuitry, but the USB-UART and USB-JTAG functions behave entirely independent of one another. Programmers interested in using the UART functionality of the FT2232 within their design do not need to worry about the JTAG circuitry interfering with the UART data transfers, and vice-versa. The combination of these two features into a single device allows the Nexys4 to be programmed, communicated with via UART, and powered from a computer attached with a single Micro USB cable.

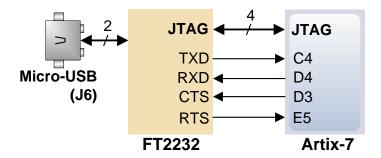

The connections between the FT2232HQ and the Artix-7 are shown in Figure 6.

Figure 6. Nexys4 FT2232HQ connections

### 7 USB HID Host

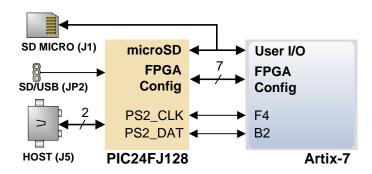

The Auxiliary Function microcontroller (Microchip PIC24FJ128) provides the Nexys4 with USB HID host capability. After power-up, the microcontroller is in configuration mode, either downloading a bitstream to the FPGA, or waiting to be programmed from other sources. Once the FPGA is programmed, the microcontroller switches to application mode, which is USB HID Host in this case. Firmware in the microcontroller can drive a mouse or a keyboard attached to the type A USB connector at J5 labeled "USB Host." Hub support is not currently available, so only a single mouse or a single keyboard can be used. The PIC24 drives several signals into the FPGA – two are used to implement a standard PS/2 interface for communication with a mouse or keyboard, and the others are connected to the FPGA's two-wire serial programming port, so the FPGA can be programmed from a file stored on a USB pen drive or microSD card.

Figure 7. Nexys4 PIC24 Connections

#### 7.1 HID Controller

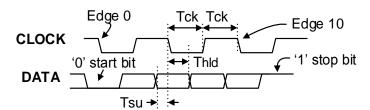

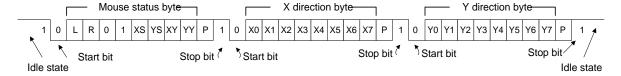

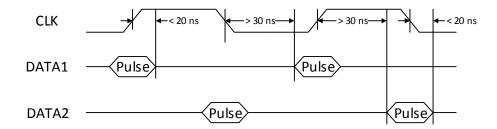

The Auxiliary Function microcontroller hides the USB HID protocol from the FPGA and emulates an old-style PS/2 bus. The microcontroller behaves just like a PS/2 keyboard or mouse would. This means new designs can re-use existing PS/2 IP cores. Mice and keyboards that use the PS/2 protocol use a two-wire serial bus (clock and data) to communicate with a host. On the Nexys4, the microcontroller emulates a PS/2 device, while the FPGA plays the role of the host. Both the mouse and the keyboard use 11-bit words that include a start bit, data byte (LSB first), odd parity, and stop bit, but the data packets are organized differently, and the keyboard interface allows bidirectional data transfers (so the host device can illuminate state LEDs on the keyboard). Bus timings are shown in Figure 8.

| Symbol           | Parameter                | Min  | Max  |

|------------------|--------------------------|------|------|

| T <sub>CK</sub>  | Clock time               | 30us | 50us |

| T <sub>SU</sub>  | Data-to-clock setup time | 5us  | 25us |

| T <sub>HLD</sub> | Clock-to-data hold time  | 5us  | 25us |

Figure 8. PS/2 Device-to-Host Timing Diagram

The clock and data signals are only driven when data transfers occur; otherwise they are held in the idle state at logic '1.' This requires that when the PS/2 signals are used in a design, internal pull-ups must be enabled in the FPGA on the data and clock pins. The clock signal is normally driven by the device, but may be held low by the host in special cases. The timings define signal requirements for mouse-to-host communications and bi-directional keyboard communications. A PS/2 interface circuit can be implemented in the FPGA to create a keyboard or mouse interface.

When a keyboard or mouse is connected to the Nexys4, a "self-test passed" command (0xAA) is sent to the host. After this, commands may be issued to the device. Since both the keyboard and the mouse use the same PS/2 port, one can tell the type of device connected using the device ID. This ID can be read by issuing a Read ID command (0xF2). Also, a mouse sends its ID (0x00) right after the "self-test passed" command, which distinguishes it from a keyboard.

### 7.2 Keyboard

The keyboard uses open-collector drivers so the keyboard, or an attached host device, can drive the two-wire bus (if the host device will not send data to the keyboard, then the host can use input-only ports).

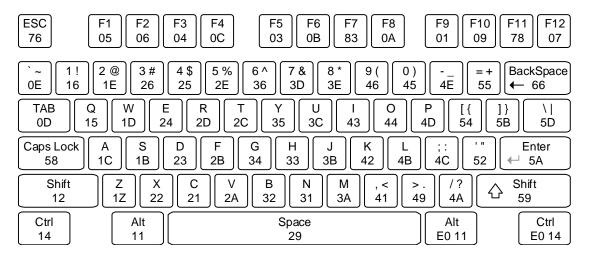

PS/2-style keyboards use scan codes to communicate key press data. Each key is assigned a code that is sent whenever the key is pressed. If the key is held down, the scan code will be sent repeatedly about once every 100ms. When a key is released, an F0 key-up code is sent, followed by the scan code of the released key. If a key can be shifted to produce a new character (like a capital letter), then a shift character is sent in addition to the scan code, and the host must determine which ASCII character to use. Some keys, called extended keys, send an E0 ahead of the scan code (and they may send more than one scan code). When an extended key is released, an E0 F0 key-up code is sent, followed by the scan code. Scan codes for most keys are shown in Figure 9.

Figure 9. Keyboard scan codes

A host device can also send data to the keyboard. Table 4 shows a list of some common commands a host might send.

| Command | Action                                                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ED      | Set Num Lock, Caps Lock, and Scroll Lock LEDs. Keyboard returns FA after receiving ED, then host sends a byte to set LED status: bit 0 sets Scroll Lock, bit 1 sets Num Lock, and bit 2 sets Caps lock. Bits 3 to 7 are ignored. |

| EE      | Echo (test). Keyboard returns EE after receiving EE                                                                                                                                                                              |

| F3      | Set scan code repeat rate. Keyboard returns F3 on receiving FA, then host sends second byte to set the repeat rate.                                                                                                              |

| FE      | Resend. FE directs keyboard to re-send most recent scan code.                                                                                                                                                                    |

| FF      | Reset. Resets the keyboard.                                                                                                                                                                                                      |

Table 4. Keyboard commands

The keyboard can send data to the host only when both the data and clock lines are high (or idle). Because the host is the bus master, the keyboard must check to see whether the host is sending data before driving the bus. To facilitate this, the clock line is used as a "clear to send" signal. If the host drives the clock line low, the keyboard must not send any data until the clock is released. The keyboard sends data to the host in 11-bit words that contain a '0' start bit, followed by 8-bits of scan code (LSB first), followed by an odd parity bit and terminated with a '1' stop bit. The keyboard generates 11 clock transitions (at 20 to 30KHz) when the data is sent, and data is valid on the falling edge of the clock.

#### 7.3 Mouse

Once entered in stream mode and data reporting enabled the mouse outputs a clock and data signal when it is moved: otherwise, these signals remain at logic '1.' Each time the mouse is moved, three 11-bit words are sent from the mouse to the host device, as shown in **Error! Reference source not found.**. Each of the 11-bit words ontains a '0' start bit, followed by 8 bits of data (LSB first), followed by an odd parity bit, and terminated with a '1' stop bit. Thus, each data transmission contains 33 bits, where bits 0, 11, and 22 are '0' start bits, and bits 11, 21, and 33 are '1' stop bits. The three 8-bit data fields contain movement data as shown in the figure above. Data is valid at the falling edge of the clock, and the clock period is 20 to 30KHz.

The mouse assumes a relative coordinate system wherein moving the mouse to the right generates a positive number in the X field, and moving to the left generates a negative number. Likewise, moving the mouse up generates a positive number in the Y field, and moving down represents a negative number (the XS and YS bits in the status byte are the sign bits – a '1' indicates a negative number). The magnitude of the X and Y numbers represent the rate of mouse movement – the larger the number, the faster the mouse is moving (the XV and YV bits in the status byte are movement overflow indicators – a '1' means overflow has occurred). If the mouse moves continuously, the 33-bit transmissions are repeated every 50ms or so. The L and R fields in the status byte indicate Left and Right button presses (a '1' indicates the button is being pressed).

Figure 10. Mouse Data Format

The microcontroller also supports Microsoft Intellimouse-type extensions for reporting back a third axis representing the mouse wheel, as shown in Table 5.

| Command | Action                                                                                                                                                                                                                                                      |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EA      | Set stream mode. The mouse responds with "acknowledge" (0xFA) then resets its movement counters and enters stream mode.                                                                                                                                     |

| F4      | Enable data reporting. The mouse responds with "acknowledge" (0xFA) then enables data reporting and resets its movement counters. This command only affects behavior in stream mode. Once issued, mouse movement will automatically generate a data packet. |

| F5      | Disable data reporting. The mouse responds with "acknowledge" (0xFA) then disables data reporting and resets its movement counters.                                                                                                                         |

| F3      | Set mouse sample rate. The mouse responds with "acknowledge" (0xFA) then reads one more byte from the host. This byte is then saved as the new sample rate, and a new "acknowledge" packet is issued.                                                       |

| FE      | Resend. FE directs mouse to re-send last packet.                                                                                                                                                                                                            |

| FF      | Reset. The mouse responds with "acknowledge" (0xFA) then enters reset mode.                                                                                                                                                                                 |

Table 5. Microsoft Intellimouse-type extensions, commands and actions

### **8 VGA Port**

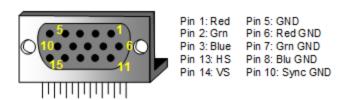

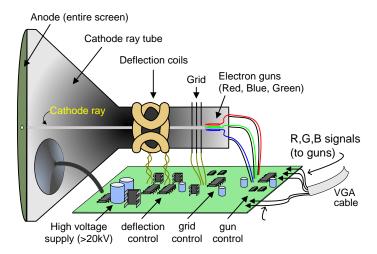

The Nexys4 board uses 14 FPGA signals to create a VGA port with 4 bits-per-color and the two standard sync signals (HS – Horizontal Sync, and VS – Vertical Sync). The color signals use resistor-divider circuits that work in conjunction with the 75-ohm termination resistance of the VGA display to create 16 signal levels each on the red, green, and blue VGA signals. This circuit, shown in Figure 11, produces video color signals that proceed in equal increments between 0V (fully off) and 0.7V (fully on). Using this circuit, 4096 different colors can be displayed, one for each unique 12-bit pattern. A video controller circuit must be created in the FPGA to drive the sync and color signals with the correct timing in order to produce a working display system.

Figure 11. Nexys4 VGA Interface

# 8.1 VGA System Timing

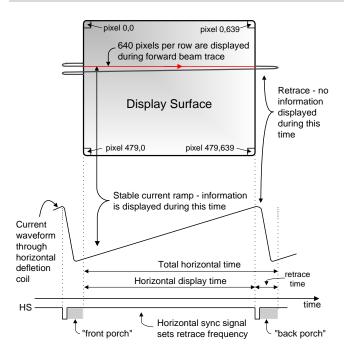

VGA signal timings are specified, published, copyrighted and sold by the VESA organization (www.vesa.org). The following VGA system timing information is provided as an example of how a VGA monitor might be driven in 640 by 480 mode.

NOTE: For more precise information, or for information on other VGA frequencies, refer to documentation available at the VESA website.

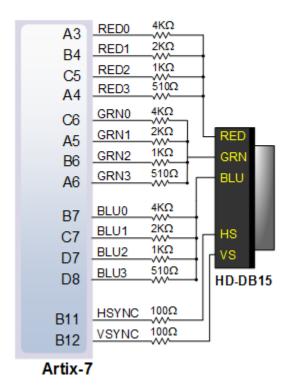

CRT-based VGA displays use amplitude-modulated moving electron beams (or cathode rays) to display information on a phosphor-coated screen. LCD displays use an array of switches that can impose a voltage across a small amount of liquid crystal, thereby changing light permittivity through the crystal on a pixel-by-pixel basis. Although the following description is limited to CRT displays, LCD displays have evolved to use the same signal timings as CRT displays (so the "signals" discussion below pertains to both CRTs and LCDs). Color CRT displays use three electron beams (one for red, one for blue, and one for green) to energize the phosphor that coats the inner side of the display end of a cathode ray tube (see **Error! Reference source not found.1**2).

Figure 12. Color CRT display

Electron beams emanate from "electron guns" which are finely-pointed heated cathodes placed in close proximity to a positively charged annular plate called a "grid." The electrostatic force imposed by the grid pulls rays of energized electrons from the cathodes, and those rays are fed by the current that flows into the cathodes. These particle rays are initially accelerated towards the grid, but they soon fall under the influence of the much larger electrostatic force that results from the entire phosphor-coated display surface of the CRT being charged to 20kV (or more). The rays are focused to a fine beam as they pass through the center of the grids, and then they accelerate to impact on the phosphor-coated display surface. The phosphor surface glows brightly at the impact point, and it continues to glow for several hundred microseconds after the beam is removed. The larger the current fed into the cathode, the brighter the phosphor will glow.

Between the grid and the display surface, the beam passes through the neck of the CRT where two coils of wire produce orthogonal electromagnetic fields. Because cathode rays are composed of charged particles (electrons), they can be deflected by these magnetic fields. Current waveforms are passed through the coils to produce magnetic fields that interact with the cathode rays and cause them to transverse the display surface in a "raster" pattern, horizontally from left to right and vertically from top to bottom, as shown in Figure 14. As the cathode ray moves over the surface of the display, the current sent to the electron guns can be increased or decreased to change the brightness of the display at the cathode ray impact point.

Information is only displayed when the beam is moving in the "forward" direction (left to right and top to bottom), and not during the time the beam is reset back to the left or top edge of the display. Much of the potential display time is therefore lost in "blanking" periods when the beam is reset and stabilized to begin a new horizontal or vertical display pass. The size of the beams, the frequency at which the beam can be traced across the display, and the frequency at which the electron beam can be modulated determine the display resolution.

Modern VGA displays can accommodate different resolutions, and a VGA controller circuit dictates the resolution by producing timing signals to control the raster patterns. The controller must produce synchronizing pulses at 3.3V (or 5V) to set the frequency at which current flows through the deflection coils, and it must ensure that video data is applied to the electron guns at the correct time. Raster video displays define a number of "rows" that corresponds to the number of horizontal passes the cathode makes over the display area, and a number of "columns" that corresponds to an area on each row that is assigned to one "picture element" or pixel. Typical displays use from 240 to 1200 rows and from 320 to 1600 columns. The overall size of a display and the number of rows and columns determines the size of each pixel.

Figure 13. VGA Horizontal Synchronization

Video data typically comes from a video refresh memory, with one or more bytes assigned to each pixel location (the Nexys4 uses 12 bits per pixel). The controller must index into video memory as the beams move across the display, and retrieve and apply video data to the display at precisely the time the electron beam is moving across a given pixel.

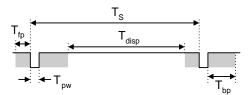

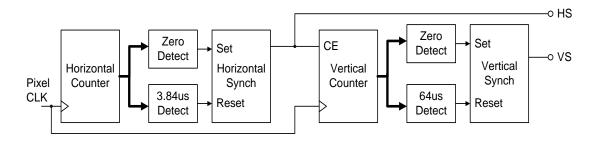

A VGA controller circuit must generate the HS and VS timings signals and coordinate the delivery of video data based on the pixel clock. The pixel clock defines the time available to display one pixel of information. The VS signal defines the "refresh" frequency of the display, or the frequency at which all information on the display is redrawn. The minimum refresh frequency is a function of the display's phosphor and electron beam intensity, with practical refresh frequencies falling in the 50Hz to 120Hz range. The number of lines to be displayed at a given refresh frequency defines the horizontal "retrace" frequency. For a 640-pixel by 480-row display using a 25MHz pixel clock and 60 +/-1Hz refresh, the signal timings shown in Figure 14 can be derived. Timings for sync pulse width and front and back porch intervals (porch intervals are the pre- and post-sync pulse times during which information cannot be displayed) are based on observations taken from actual VGA displays.

| Symbol          | Parameter    | Vertical Sync |         |       | Horiz. Sync |      |

|-----------------|--------------|---------------|---------|-------|-------------|------|

| Symbol          |              | Time          | Clocks  | Lines | Time        | Clks |

| TS              | Sync pulse   | 16.7ms        | 416,800 | 521   | 32 us       | 800  |

| T disp          | Display time | 15.36ms       | 384,000 | 480   | 25.6 us     | 640  |

| Tpw             | Pulse width  | 64 us         | 1,600   | 2     | 3.84 us     | 96   |

| T <sub>fp</sub> | Front porch  | 320 us        | 8,000   | 10    | 640 ns      | 16   |

| T <sub>bp</sub> | Back porch   | 928 us        | 23,200  | 29    | 1.92 us     | 48   |

Figure 14. Signal timings for a 640-pixel by 480 row display using a 25MHz pixel clock and 60Hz vertical refresh

A VGA controller circuit, such as the one diagramed in Figure 15, decodes the output of a horizontal-sync counter driven by the pixel clock to generate HS signal timings. You can use this counter to locate any pixel location on a given row. Likewise, the output of a vertical-sync counter that increments with each HS pulse can be used to generate VS signal timings, and you can use this counter to locate any given row. These two continually running counters can be used to form an address into video RAM. No time relationship between the onset of the HS pulse and the onset of the VS pulse is specified, so you can arrange the counters to easily form video RAM addresses, or to minimize decoding logic for sync pulse generation.

Figure 15. VGA display controller block diagram

### 9 Basic VO

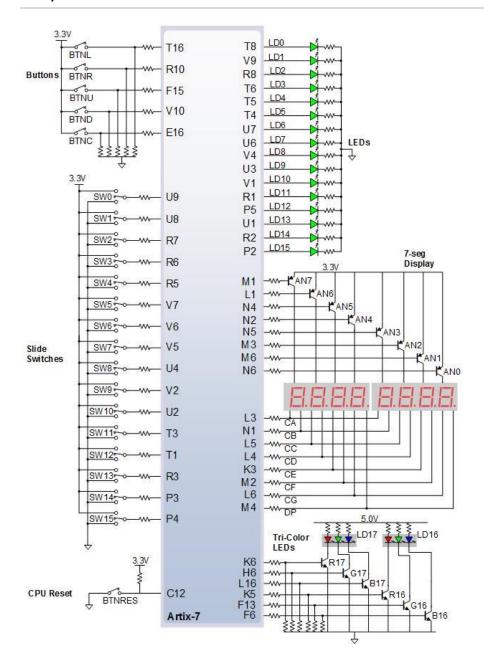

The Nexys4 board includes two tri-color LEDs, sixteen slide switches, six push buttons, sixteen individual LEDs, and an eight-digit seven-segment display, as shown in Figure 16. The pushbuttons and slide switches are connected to the FPGA via series resistors to prevent damage from inadvertent short circuits (a short circuit could occur if an FPGA pin assigned to a pushbutton or slide switch was inadvertently defined as an output). The five pushbuttons arranged in a plus-sign configuration are "momentary" switches that normally generate a low output when they are at rest, and a high output only when they are pressed. The red pushbutton labeled "CPU RESET," on the other hand, generates a high output when at rest and a low output when pressed. The CPU RESET button is intended to be used in EDK designs to reset the processor, but you can also use it as a general purpose pushbutton. Slide switches generate constant high or low inputs depending on their position.

The sixteen individual high-efficiency LEDs are anode-connected to the FPGA via 330-ohm resistors, so they will turn on when a logic high voltage is applied to their respective I/O pin. Additional LEDs that are not user-accessible indicate power-on, FPGA programming status, and USB and Ethernet port status.

# 9.1 Seven-Segment Display

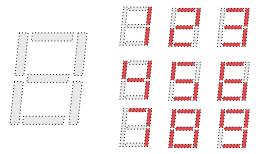

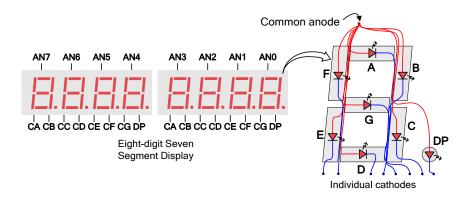

The Nexys4 board contains two four-digit common anode seven-segment LED displays, configured to behave like a single eight-digit display. Each of the eight digits is composed of seven segments arranged in a "figure 8" pattern, with an LED embedded in each segment. Segment LEDs can be individually illuminated, so any one of 128 patterns can be displayed on a digit by illuminating certain LED segments and leaving the others dark, as shown in Figure 17. Of these 128 possible patterns, the ten corresponding to the decimal digits are the most useful.

Figure 17. An un-illuminated seven-segment display, and nine illumination patterns corresponding to decimal digits

The anodes of the seven LEDs forming each digit are tied together into one "common anode" circuit node, but the LED cathodes remain separate, as shown in Figure 18. The common anode signals are available as eight "digit enable" input signals to the 8-digit display. The cathodes of similar segments on all four displays are connected into seven circuit nodes labeled CA through CG (so, for example, the eight "D" cathodes from the eight digits are grouped together into a single circuit node called "CD"). These seven cathode signals are available as inputs to the 8-digit display. This signal connection scheme creates a multiplexed display, where the cathode signals are common to all digits but they can only illuminate the segments of the digit whose corresponding anode signal is asserted.

To illuminate a segment, the anode should be driven high, while the cathode is driven low. However, since the Nexys4 uses transistors to drive enough current into the common anode point, so the anode enables are inverted. Therefore, both the ANO..7 and the CA..G/DP signals are driven low, when active.

Figure 18. Common anode circuit node

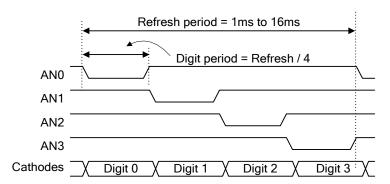

A scanning display controller circuit can be used to show an eight-digit number on this display. This circuit drives the anode signals and corresponding cathode patterns of each digit in a repeating, continuous succession, at an update rate that is faster than the human eye can detect. Each digit is illuminated just one-eighth of the time, but because the eye cannot perceive the darkening of a digit before it is illuminated again, the digit appears continuously illuminated. If the update or "refresh" rate is slowed to around 45 hertz,, a flicker can be noticed in the display.

For each of the four digits to appear bright and continuously illuminated, all eight digits should be driven once every 1 to 16ms, for a refresh frequency of about 1KHz to 60Hz. For example, in a 62.5Hz refresh scheme, the entire display would be refreshed once every 16ms, and each digit would be illuminated for 1/8 of the refresh cycle, or 2ms. The controller must drive low the cathodes with the correct pattern when the corresponding anode signal is driven high. To illustrate the process, if ANO is asserted while CB and CC are asserted, then a "1" will be

displayed in digit position 1. Then, if AN1 is asserted while CA, CB and CC are asserted, a "7" will be displayed in digit position 2. If AN0, CB, and CC are driven for 4ms, and then AN1, CA, CB, and CC are driven for 4ms in an endless succession, the display will show "71" in the first two digits. An example timing diagram for a four-digit controller is shown in Figure 19.

Figure 19. Four digit scanning display controller timing diagram

#### 9.2 Tri-Color LEDs

The Nexys4 board contains two tri-color LEDs. Each tri-color LED has three input signals that drive the cathodes of three smaller internal LEDs: one red, one blue, and one green. Driving the signal corresponding to one of these colors high will illuminate the internal LED. The input signals are driven by the FPGA through a transistor, which inverts the signals. Therefore, to light up the tri-color LED, the corresponding signals need to be driven high. The tri-color LED will emit a color dependent on the combination of internal LEDs that are currently being illuminated. For example, if the red and blue signals are driven high, and green is driven low, the tri-color LED will emit a purple color.

Note: Digilent strongly recommends that the use of Pulse-Width Modulation (PWM) when driving the tri-color LEDs (for information on PWM, see section 15.1Error! Reference source not found., Error! Reference source not und.). Driving any of the inputs to a steady logic '1' will result in the LED being illuminated at an uncomfortably bright level. You can avoid this by ensuring that none of the tri-color signals are driven with more than a 50% duty cycle. Using PWM also greatly expands the potential color palette of the tri-color led. Individually adjusting the duty cycle of each color between 50% and 0% causes the different colors to be illuminated at different intensities, allowing virtually any color to be displayed.

### **10 Pmod Connectors**

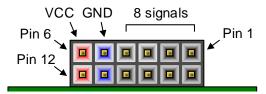

The Pmod connectors are arranged in a 2x6 right-angle, and are100-mil female connectors that mate with standard 2x6 pin headers.. Each 12-pin Pmod connector provides two 3.3V VCC signals (pins 6 and 12), two Ground signals (pins 5 and 11), and eight logic signals, as shown in Figure 20. The VCC and Ground pins can deliver up to 1A of current. Pmod data signals are not matched pairs, and they are routed using best-available tracks without impedance control or delay matching. Pin assignments for the Pmod I/O connected to the FPGA are shown in Error! Reference source not found.

Figure 20. PMOD Connectors- Front view as loaded on PCB

| PMOD<br>Pinouts |           |          |          |              |

|-----------------|-----------|----------|----------|--------------|

| JA1: B13        | JP1: G14  | JC1: K2  | JD1: H4  | JXADC1: A13  |

| JA2: F14        | JB2: P15  | JC2: E7  | JD2: H1  | JXADC2: A15  |

| JA3: D17        | JB3: V11  | JC3: J3  | JD3: G1  | JXADC3: B16  |

| JA4: E17        | JB4: V15  | JC4: J4  | JD4: G3  | JXADC4: B18  |

| JA7: G13        | JB7: K16  | JC7: K1  | JD7: H2  | JXADC7: A14  |

| JA8: C17        | JB8: R16  | JC8: E6  | JD8: G4  | JXADC8: A16  |

| JA9: D18        | JB9: T9   | JC9: J2  | JD9: G2  | JXADC9: B17  |

| JA10: E18       | JB10: U11 | JC10: G6 | JD10: F3 | JXADC10: A18 |

Table 6. Nexys4 Pmod Pin Assignments

Digilent produces a large collection of Pmod accessory boards that can attach to the Pmod expansion connectors to add ready-made functions like A/D's, D/A's, motor drivers, sensors, and other functions. See <a href="https://www.digilentinc.com">www.digilentinc.com</a> for more information.

# 10.1 Dual Analog/ Digital Pmod

The on-board Pmod expansion connector labeled "JXADC" is wired to the auxiliary analog input pins of the FPGA. Depending on the configuration, this connector can be used to input differential analog signals to the analog-to-digital converter inside the Artix-7 (XADC). Any or all pairs in the connector can be configured either as analog input or digital input-output.

The Dual Analog/Digigal Pmod on the Nexys4differs from the rest in the routing of its traces. The eight data signals are grouped into four pairs, with the pairs routed closely coupled for better analog noise immunity. Furthermore, each pair has a partially loaded anti-alias filter laid out on the PCB. The filter does not have capacitors C60-C63. In designs where such filters are desired, the capacitors can be manually loaded by the user.

NOTE: The coupled routing and the anti-alias filters might limit the data speeds when used for digital signals.

The XADC core within the Artix-7 is a dual channel 12-bit analog-to-digital converter capable of operating at 1 MSPS. Either channel can be driven by any of the auxiliary analog input pairs connected to the JXADC header. The XADC core is controlled and accessed from a user design via the Dynamic Reconfiguration Port (DRP). The DRP also provides access to voltage monitors that are present on each of the FPGA's power rails, and a temperature sensor that is internal to the FPGA. For more information on using the XADC core, refer to the Xilinx document titled "7 Series FPGAs and Zynq-7000 All Programmable SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter."

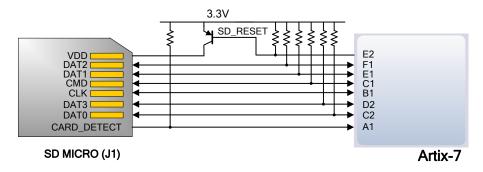

### 11 MicroSD Slot

The Nexys4 provides a microSD slot for both FPGA configuration and user access. The on-board Auxiliary Function microcontroller shares the SD card bus with the FPGA. Before the FPGA is configured the microcontroller must have access to the SD card via a SPI interface. Once a bit file is downloaded to the FPGA (from any source), the microcontroller power cycles the SD slot and relinquishes control of the bus. This enables any SD card in the slot to reset its internal state machines and boot up in SD native bus mode. All of the SD pins on the FPGA are wired to support full SD speeds in native interface mode, as shown in Figure 21. The SPI interface is also available, if needed. Once control over the SD bus is passed from the microcontroller to the FPGA, the SD\_RESET signal needs to be actively driven low by the FPGA to power the microSD card slot. For information on implementing an SD card controller, refer to the SD card specification available at <a href="https://www.sdcard.org">www.sdcard.org</a>.

Figure 21. Artix-7 microSD card connector interface (PIC24 connections not shown)

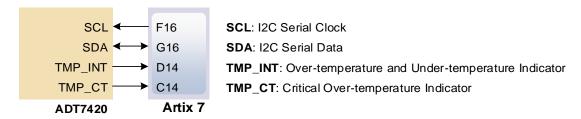

# **12 Temperature Sensor**

The Nexys4 includes an Analog Device ADT7420 temperature sensor. The sensor provides up to 16 bit resolution with a typical accuracy better than 0.25 degrees Celsius. The interface between the temperature sensor and FPGA is shown in Figure 22.

Figure 22. Temperature Sensor interface

#### 12.1 I2C Interface

The ADT7420 chip acts as a slave device using the industry standard I2C communication scheme. To communicate with ADT7420 chip, the I2C master must specify a slave address (0x4B) and a flag indicating whether the communication is a read (1) or a write (0). Once specifications are made for communication a data transfer takes place. For ADT7420, the data transfer should consist of the address of the desired device register followed by the data to be written to the specified register. To read from a register, the master must write the desired register

address to the ADT7420, then send an I2C restart condition, and send a new read request to the ADT7420. If the master does not generate a restart condition prior to attempting the read, the value written to the address register will be reset to 0x00.

As some registers store 16-bit values as 8-bit register pairs, the ADT7420 will automatically increment the address register of the device when accessing certain registers, such as the temperature registers and the threshold registers. This allows for the master to use a single read or write request to access both the low and high bytes of these registers. A complete listing of registers and their behavior can be found in the ADT7420 datasheet available on the Analog Devices web site.

### 12.2 Open Drain Outputs

The ADT7420 provides two open drain output signals to indicate when pre-set temperature thresholds are reached. If the temperature leaves a range defined by registers TLOW (0x06:0x07) and THIGH (0x04:0x05), the INT pin can be driven low or high based upon the configuration of the device. Similarly, the CT pin can be driven low or high if the temperature exceeds a critical threshold defined in TCRIT (0x08:0x09). Both of these pins need internal FPGA pull-ups when used.

For details on their electrical specifications and configuration of the INT and CT pins, refer to the ADT7420 datasheet.

### 12.3 Quick Start Operation

When the ADT7420 is powered up, it is in a mode that can be used as a simple temperature sensor without any initial configuration. By default, the device address register points to the temperature MSB register, so a two byte read without specifying a register will read the value of the temperature register from the device. The first byte read back will be the most significant byte (MSB) of the temperature data, and the second will be the least significant byte (LSB) of the data. These two bytes form a two's complement 16-bit integer, if the result is shifted to the right three bits and multiplied by 0.0625 the resulting signed floating point value will be a temperature reading in degrees Celsius.

For information on reading and writing to the other registers of the device, as well as notes on the accuracy of the temperature measurements, refer to the ADT7420 datasheet.

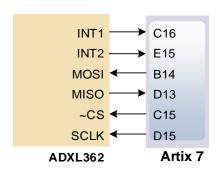

# 13 Accelerometer

The Nexys4 includes an Analog Device ADXL362 accelerometer. The ADXL362 is a 3-axis MEMS accelerometer that consumes less than 2  $\mu$ A at a 100 Hz output data rate and 270 nA when in motion triggered wake-up mode. Unlike accelerometers that use power duty cycling to achieve low power consumption, the ADXL362 does not alias input signals by under-sampling; it samples the full bandwidth of the sensor at all data rates. The ADXL362 always provides 12-bit output resolution; 8-bit formatted data is also provided for more efficient single-byte transfers when a lower resolution is sufficient. Measurement ranges of  $\pm 2$  g,  $\pm 4$  g, and  $\pm 8$  g are available, with a resolution of 1 mg/LSB on the  $\pm 2$  g range. The FPGA can talk with the ADXL362 via SPI interface. While the ADXL362 is in Measurement Mode, it continuously measures and stores acceleration data in the X-data, Y-data, and Z-data registers. The interface between the FPGA and accelerometer can be seen in Figure 23.

INT1: Interrupt One INT2: Interrupt Two

MOSI: Master Out Slave In

MISO: Master In Slave Out

~CS: Slave Select (Active Low)

SCLK: Serial Clock

#### 13.1 SPI Interface

The ADXL362 acts as a slave device using an SPI communication scheme. The recommended SPI clock frequency ranges from 1MHz to 5MHz. The SPI interface operates in SPI mode 0 with CPOL = 0 and CPHA = 0. All communications with the device must specify a register address and a flag that indicate whether the communication is a read or a write. Actual data transfer always follows the register address and communication flag. Device configuration can be performed by writing to the control registers within the accelerometer. Access accelerometer data by reading the device registers.

For a full list of registers, their functionality, and communication specifications, see the ADXL362 datasheet available at: <a href="https://www.analog.com">www.analog.com</a>.

### 13.2 Interrupts

Several of the built-in functions of the ADXL362 can trigger interrupts that alert the host processor of certain status conditions. Interrupts can be mapped to either (or both) of two interrupt pins (INT1, INT2). Both of these pins require internal FPGA pull-ups when used. For more details about the interrupts, see the ADXL362 datasheet available at: <a href="https://www.analog.com">www.analog.com</a>.

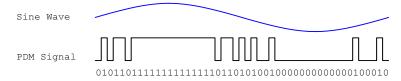

# 14 Microphone

The Nexys4 board includes an omnidirectional MEMS microphone. The microphone uses an Analog Device ADMP421 chip which has a high signal to noise ratio (SNR) of 61dBA and high sensitivity of -26 dBFS. It also has a flat frequency response ranging from 100Hz to 15kHz. The digitized audio is output in the pulse density modulated (PDM) format.

The component architecture is shown in Figure 24.

**CLK**: Clock Input to Microphone

**DATA**: Data Output Signal

L/R SEL: Left/Right Channel Select

Figure 24. Microphone Block Diagaram

# 14.1 Pulse Density Modulation (PDM)

PDM data connections are becoming more and more popular in portable audio applications such as cellphones and tablets. With PDM, two channels can be transmitted with only two wires. The frequency of a PDM signal usually

Page 24 of

falls in the range of 1MHz to 3MHz. In a PDM bit stream, a 1 corresponds a positive pulse and a 0 corresponds a negative pulse. A run consisting of all '1's would corresponds to the maximum positive value and a run of '0's would corresponds to the minimum amplitude value. **Error! Reference source not found.**5 shows how a sine wave s represented in PDM signal.

Figure 25. PDM representation of a sine wave

A PDM signal is generated from an analog signal through a process called Delta-Sigma Modulation. A simple idealized circuit of Delta-Sigma Modulator is shown as Figure 26.

Figure 26. Simple Delta-Sigma Modulator Circuit

To keep things simple here, assume that the analog input and digital output have the same voltage range 0~Vdd. The input of the flip-flop acts like a comparator (any signal above Vdd/2 is considered as '1' and any input bellow Vdd/2 is considered '0'). The input of the integral circuit is the difference of the input analog signal and the PDM signal of the previous clock cycle. Then the integral circuit integrates both these inputs, and the output of the integral circuit is sampled by a D-Flip-flop.. **Error! Reference source not found.** shows the function of the deltaigma modulator with an input of 0.4Vdd.

| Sum        | Integrator Out | Flip-flop Output |

|------------|----------------|------------------|

| 0.4-0=0.4  | 0+0.4=0.4      | 0                |

| 0.4-0=0.4  | 0.4+0.4=0.8    | 1                |

| 0.4-1=-0.6 | 0.8-0.6=0.2    | 0                |

| 0.4-0=0.4  | 0.2+0.4=0.6    | 1                |

| 0.4-1=-0.6 | 0.6-0.6=0      | 0                |

| 0.4-0=0.4  | 0+0.4=0.4      | 0                |

| 0.4-0=0.4  | 0.4+0.4=0.8    | 1                |

| 0.4-1=-0.6 | 0.8-0.6=0.2    | 0                |

Table 7. Sigma Delta Modulator with a 0.4Vdd input

Note that the average of the flip-flop output equals the value of the input analog signal. So, in order to get the value of analog input, all that is needed is a counter that counts the '1's for a certain period of time.

# 14.2 Microphone Digital Interface Timing

The clock input of the microphone can range from 1MHz to 3.3MHz based on the sampling rate and data precision requirement of the applications. The L/R Select signal must be set to a valid level, depending on which edge of the

clock the data bit will be read. A low level on L/RSEL makes data available on the rising edge of the clock, while a high level corresponds to the falling edge of the clock, as shown in Figure 27.

Figure 27. PDM Timing Diagram

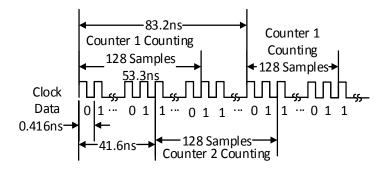

The typical value of the clock frequency is 2.4MHz. Assuming that the application requires 7-bit precision and 24KHz, there can be two counters that count 128 samples at 12KHz, as shown in Figure 28.

Figure 28. Sampling PDM with two counters

# **15 Mono Audio Output**

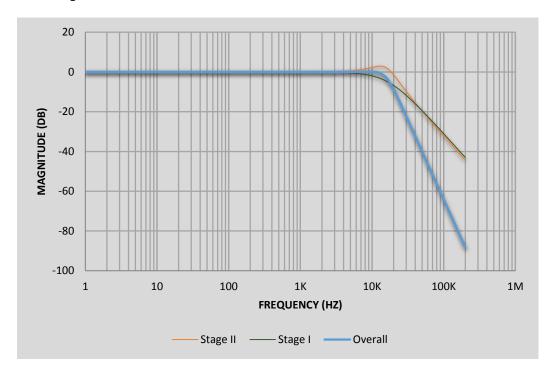

The on-board audio jack (J8) is driven by a Sallen-Key Butterworth Low-pass 4<sup>th</sup> Order Filter that provides mono audio output. The circuit of the low pass filter is shown in Figure 29. The input of the filter (AUD\_PWM) is connected to the FPGA pin A11. A digital input will typically be a pulse width modulated (PWM) signal or pulse density modulated (PDM) signal produced by the FPGA. The low pass filter on the input will act as a reconstruction filter to convert the pulse width modulated digital signal into an analog voltage on the audio jack output.

#### Sallen-Key Butterworth Low Pass 4th Order Filter J7 1х1 No Load AD8592ARMZ IC3B AD8592ARMZ IC3A TP R166 C24 AUD PWM AUDIO 1.3K 10K R169 1nF 26.1K 1% R168 1nF **≤**10.7K 26.1K 1% 1% J8 **≷**R270 1% 1% C28 100K 100uF 2K R271 /SDA C26 C27 /SDB AUD SD GND 820pH 150pF AUD SD PRG18BB330 5% 5% R170 R171 GND 2K 10K GND No Load GND

fc = 16.3KHz

G = 1

Figure 29. Sallen-Key Butterworth Low Pass 4th Order Fliter

The frequency response of SK Butterworth Low Pass Filter is shown in Figure 30. The AC analysis of the circuit is done using NI Multism 12.0.

fc = 12.5KHz

G = 1

Figure 30. SK Butterworth Low Pass Filter frequency response

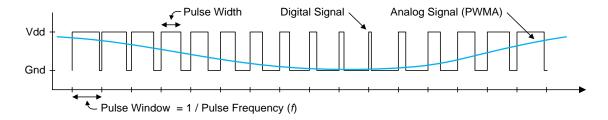

#### 15.1 Pulse-Width Modulation

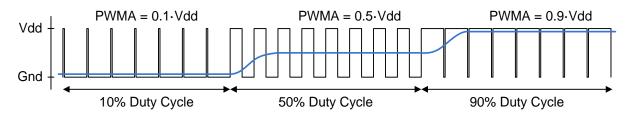

A pulse-width modulated (PWM) signal is a chain of pulses at some fixed frequency, with each pulse potentially having a different width. This digital signal can be passed through a simple low-pass filter that integrates the digital waveform to produce an analog voltage proportional to the average pulse width over some interval (the interval is determined by the 3dB cut-off frequency of the low pass filter and the pulse frequency). For example, if the pulses

are high for an average of 10% of the available pulse period, then an integrator will produce an analog value that is 10% of the Vdd voltage. Figure 31 shows a waveform represented as a PWM signal.

Figure 31. Simple Waveform represented as PWM

The PWM signal must be integrated to define an analog voltage. The low pass filter 3dB frequency should be an order of magnitude lower than the PWM frequency, so that signal energy at the PWM frequency is filtered from the signal. For example, if an audio signal must contain up to 5KHz of frequency information, then the PWM frequency should be at least 50KHz (and preferably even higher). In general, in terms of analog signal fidelity, the higher the PWM frequency, the better. **Error! Reference source not found.**2 shows a representation of a PWM ntegrator producing an output voltage by integrating the pulse train. Note the steady-state filter output signal amplitude ratio to Vdd is the same as the pulse width duty cycle (duty cycle is defined as pulse-high time divided by pulse-window time).

Figure 32. Representation of a PWM integrator production an output voltage by integrating the pulse train

### 16 Built-In Self-Test

A demonstration configuration is loaded into the SPI Flash device on the Nexys4 board during manufacturing. The source code and prebuilt bitstream for this design are available for download from the Digilent website. If the demo configuration is present in the SPI Flash device and the Nexys4 board is powered on in SPI mode, the demo project will allow basic hardware verification. Here is an overview of how this demo drives the different onboard components:

- The user LEDs are illuminated when the corresponding user switch is placed in the on position.

- The tri-color LEDs are controlled by some of the user buttons. Pressing BTNL, BTNC, or BTNR causes them to illuminate either red, green or blue, respectively. Pressing BTND causes them to begin cycling through many colors. Repeatedly pressing BTND will turn the two LEDs on or off.

- Pressing BTNU will trigger a 5 second recording from the onboard PDM microphone. This recording is then

immediately played back on the mono audio out port. The status of the recording and playback is

displayed on the user LEDs.

- The VGA port displays feedback from the onboard microphone, temperature sensors, accelerometer, RGB LEDs and USB Mouse.

- Connecting a mouse to the USB-HID Mouse port will allow the pointer on the VGA display to be controlled. Note that some Microsoft mice have difficulty communicating with this demo.

- On power-up, the seven-segment display will show the results of an automated test for the onboard

CellRAM, accelerometer, and temperature sensor. It will then display a moving snake pattern. Note that

the accelerometer test will fail if the board is on an unstable or un-level surface when it is powered on,

and the temperature sensor test may fail if the board is in an extreme thermal climate. With these two

considerations in mind, if your board is reporting a failure, make note of the error code and contact

Digilent support at support@digilentinc.com.

All Nexys4 boards are 100% tested during the manufacturing process. If any device on the Nexys4 board fails test or is not responding properly, it is likely that damage occurred during transport or during use. Typical damage includes stressed solder joints and contaminants in switches and buttons resulting in intermittent failures. Stressed solder joints can be repaired by reheating and reflowing solder and contaminants can be cleaned with off-the-shelf electronics cleaning products. If a board fails test within the warranty period, it will be replaced at no cost. Contact Digilent for more details.