# Industry's Lowest-Power Ambient Light Sensor with ADC

### **General Description**

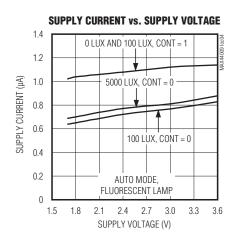

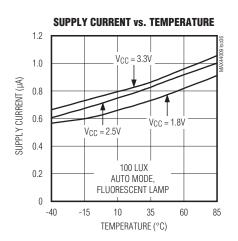

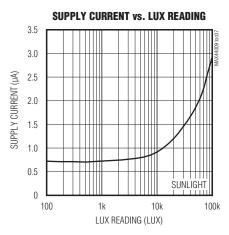

The MAX44009 ambient light sensor features an I2C digital output that is ideal for a number of portable applications such as smartphones, notebooks, and industrial sensors. At less than 1µA operating current, it is the lowest power ambient light sensor in the industry and features an ultra-wide 22-bit dynamic range from 0.045 lux to 188,000 lux.

Low-light operation allows easy operation in dark-glass applications.

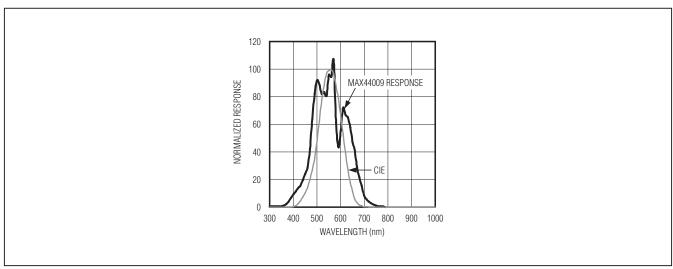

The on-chip photodiode's spectral response is optimized to mimic the human eye's perception of ambient light and incorporates IR and UV blocking capability. The adaptive gain block automatically selects the correct lux range to optimize the counts/lux.

The IC is designed to operate from a 1.7V to 3.6V supply voltage range and consumes only  $0.65\mu A$  in full operation. It is available in a small,  $2mm \times 2mm \times 0.6mm$  UTDFN-Opto package.

### \_Applications

Tablet PCs/Notebook Computers TVs/Projectors/Displays Digital Lighting Management Portable Devices Cellular Phones/Smartphones Security Systems

#### **Features**

- ♦ Wide 0.045 Lux to 188,000 Lux Range

- ♦ Small, 2mm x 2mm x 0.6mm UTDFN-Opto

- ♦ Vcc = 1.7V to 3.6V

- ♦ Icc = 0.65µA Operating Current

- **♦** -40°C to +85°C Temperature Range

- ♦ Device Address Options 1001 010x and 1001 011x

### **Ordering Information**

| PART         | PIN-PACKAGE      | TEMP RANGE     |  |  |

|--------------|------------------|----------------|--|--|

| MAX44009EDT+ | 6 UTDFN-Opto-EP* | -40°C to +85°C |  |  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

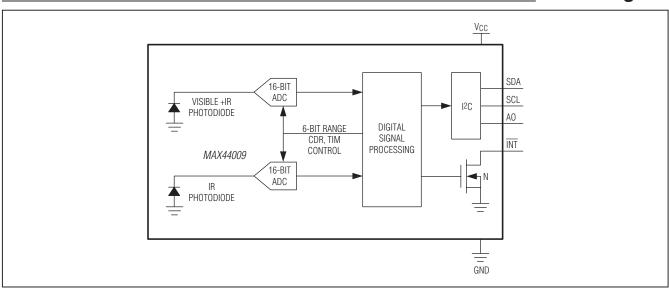

### **Block Diagram**

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

<sup>\*</sup>EP = Exposed pad.

# Industry's Lowest-Power Ambient Light Sensor with ADC

### **ABSOLUTE MAXIMUM RATINGS**

| INT to GND0.3V to (VCC + 0.3V)                          | Continuous Input Current into Any Terminal±20mA  |

|---------------------------------------------------------|--------------------------------------------------|

| All Other Pins to GND0.3V to +4V                        | Continuous Power Dissipation                     |

| INT Short-Circuit Current Duration                      | 6 UTDFN-Opto (derate 11.9mW/°C above +70°C)953mW |

| All Other Pins Short-Circuit Current DurationContinuous | Operating Temperature Range40°C to +85°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(VCC = 1.8V, TMIN to TMAX =  $-40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted.) (Note 1)

| PARAMETER SYMBOL COM                |                                   | CONDITIONS                                                   | MIN                     | TYP     | MAX          | UNITS   |  |

|-------------------------------------|-----------------------------------|--------------------------------------------------------------|-------------------------|---------|--------------|---------|--|

| OPTICAL CHARACTERISTICS             |                                   |                                                              |                         |         |              |         |  |

| Maximum Lux Sensitivity             |                                   | Fluorescent light                                            |                         | 0.045   |              | Lux/LSB |  |

| Saturation Ambient Lux Level        |                                   | Sunlight                                                     |                         | 188,000 |              | Lux     |  |

| Total Error                         | TE                                | Green LED 538nm response,<br>T <sub>A</sub> = +25°C (Note 2) |                         |         |              | %       |  |

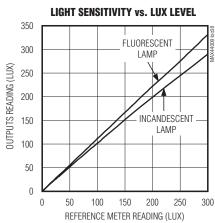

| Light Source Matching               |                                   | Fluorescent/incandescent light                               |                         | 10      |              | %       |  |

| Infrared Transmittance at 940nm     | IRR                               | $T_A = +25^{\circ}C \text{ (Note 3)}$                        |                         | 0       | 0.5          | %       |  |

| Ultraviolet Transmittance at 363nm  | UVR                               | T <sub>A</sub> = +25°C (Note 3)                              |                         | 1.2     |              | %       |  |

| Dark Level Count                    | 0LUX                              | 0 lux, T <sub>A</sub> = +25°C, 800ms range                   |                         | 0       | 0.045        | Lux     |  |

| Maximum Signal Integration Time     |                                   | Has 50/60Hz rejection                                        |                         | 800     |              | ms      |  |

| Min Oi III II T                     |                                   | Automatic mode, has 50/60Hz rejection                        |                         | 100     |              |         |  |

| Minimum Signal Integration Time     |                                   | Manual mode only                                             |                         | 6.25    |              | ms      |  |

| ADC Conversion Time                 | ACT                               | 100ms range, T <sub>A</sub> = +25°C                          | 99.6                    | 100     | 100.4        | ma      |  |

| ADC Conversion Time                 | ACT                               | 100ms range                                                  | 97                      | 103     | 107          | ms      |  |

| POWER SUPPLY                        |                                   |                                                              |                         |         |              |         |  |

| Power-Supply Voltage                | Vcc                               | Guaranteed by TE test                                        | 1.7                     |         | 3.6          | V       |  |

| Power-Supply Current                | Icc                               | $T_A = +25$ °C, 90 lux, I <sup>2</sup> C inputs inactive     |                         | 0.65    | 1.2          | μΑ      |  |

| Tower-Supply Guiterit               | 100                               | $T_A = -40$ °C to $+85$ °C                                   | 1.6                     |         | 1.6          | μA      |  |

| DIGITAL I/O CHARACTERISTICS         | 3                                 |                                                              |                         |         |              | ,       |  |

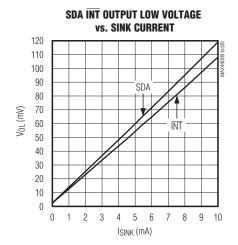

| Output Low Voltage SDA, INT         | Vol                               | ISINK = 6mA                                                  |                         | 0.06    | 0.4          | V       |  |

| INT Leakage Current                 |                                   | TA = +25°C                                                   |                         | 0.01    | 20           | nA      |  |

| SCL, SDA, A0 Input Current          | I <sub>IH</sub> , I <sub>IL</sub> | $T_A = +25^{\circ}C$                                         |                         | 0.01    | 20           | nA      |  |

| I <sup>2</sup> C Input Low Voltage  | VIL_I2C                           | SDA, SCL                                                     |                         |         | 0.3 x<br>VCC | V       |  |

| I <sup>2</sup> C Input High Voltage | VIH_I2C                           | SDA, SCL                                                     | 0.7 x<br>VCC            |         |              | V       |  |

| Address Input Low Voltage           | VIL_A0                            | A0                                                           |                         |         | 0.3          | V       |  |

| Address Input High Voltage          | VIH_A0                            | AO                                                           | V <sub>C</sub> C - 0.3V |         |              | V       |  |

| Input Capacitance                   |                                   |                                                              |                         | 3       |              | pF      |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

(VCC = 1.8V, TMIN to TMAX =  $-40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted.) (Note 1)

| PARAMETER                                          | SYMBOL  | CONDITIONS                                                                                                          | MIN | TYP | MAX | UNITS |

|----------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| I <sup>2</sup> C TIMING                            |         |                                                                                                                     |     |     |     |       |

| Serial-Clock Frequency                             | fscl    |                                                                                                                     |     |     | 400 | kHz   |

| Bus Free Time Between a STOP and a START Condition | tBUF    |                                                                                                                     | 1.3 |     |     | μs    |

| Hold Time (Repeated) START Condition               | tHD,STA |                                                                                                                     | 0.6 |     |     | μs    |

| Low Period of the SCL Clock                        | tLOW    |                                                                                                                     | 1.3 |     |     | μs    |

| High Period of the SCL Clock                       | tHIGH   |                                                                                                                     | 0.6 |     |     | μs    |

| Setup Time for a Repeated START Condition          | tsu,sta |                                                                                                                     | 0.6 |     |     | μs    |

| Data Hold Time                                     | thd,dat | (Note 4)                                                                                                            | 0   |     | 0.9 | μs    |

| Data Setup Time                                    | tsu,dat |                                                                                                                     | 100 |     |     | ns    |

| Fall Time of SDA Transmitting                      | tF      | ISINK ≤ 6mA, t <sub>R</sub> and t <sub>F</sub> are measured between 0.3 x V <sub>DD</sub> and 0.7 x V <sub>DD</sub> |     | 100 |     | ns    |

| Setup Time for STOP Condition                      | tsu,sto |                                                                                                                     | 0.6 |     |     | μs    |

| Pulse Width of Spike<br>Suppressed                 | tsp     | Input filters on the SDA and SCL inputs suppress noise spikes                                                       | 0   |     | 50  | ns    |

Note 1: All devices are 100% production tested at  $T_A = +25^{\circ}C$ . Temperature limits are guaranteed by design.

Note 2: Green 538nm LED chosen for production is such that the IC responds to 100 lux fluorescent light with 100 lux.

**Note 3:** With respect to green LED 538nm response.

Note 4: A master device must provide a hold time of at least 300ns for the SDA signal (referred to V<sub>IL</sub> of the SCL signal) to bridge the undefined region of SCL's falling edge.

# Industry's Lowest-Power Ambient Light Sensor with ADC

## **Typical Operating Characteristics**

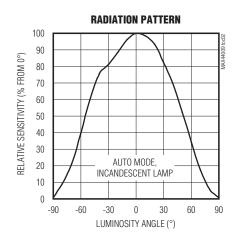

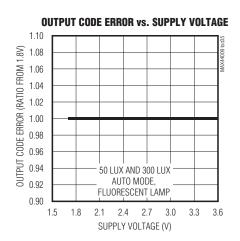

$(V_{CC} = 1.8V, default power-up setting, unless otherwise noted.)$

# Industry's Lowest-Power Ambient Light Sensor with ADC

## **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 1.8V, default power-up setting; unless otherwise noted.)

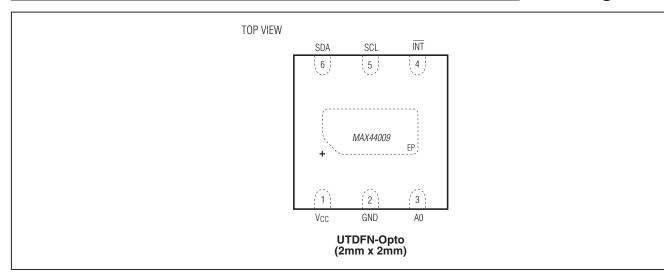

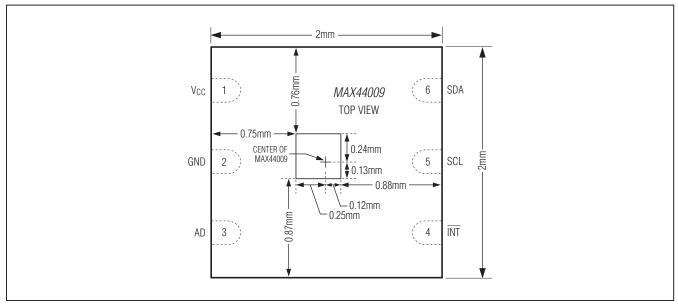

### **Pin Configuration**

## Pin Description

| PIN | NAME | PIN DESCRIPTION                                                                           |

|-----|------|-------------------------------------------------------------------------------------------|

| 1   | Vcc  | Power Supply                                                                              |

| 2   | GND  | Ground                                                                                    |

| 3   | A0   | Address Select. Pull high to select address 1001 011x or low to select address 1001 010x. |

| 4   | ĪNT  | Interrupt Output. Use an external pullup resistor.                                        |

| 5   | SCL  | I <sup>2</sup> C Clock Bus                                                                |

| 6   | SDA  | I <sup>2</sup> C Data Bus                                                                 |

| _   | EP   | Exposed Pad. Connect EP to ground.                                                        |

# Industry's Lowest-Power Ambient Light Sensor with ADC

### **Detailed Description**

The MAX44009 is an ambient light sensor with integrated photodiode and ADC with an I<sup>2</sup>C digital interface. To measure ambient light, the die is placed inside an optically transparent (UTDFN-Opto) package. A photodiode inside the IC converts the light to a current that is then processed by low-power circuitry into a digital bit stream. This is digitally processed and stored in an output register that is read by an I<sup>2</sup>C interface. An on-chip programmable interrupt function eliminates the need for continually polling the device for data and results in significant power saving.

A package-level optical filter prevents ultraviolet and infrared from reaching the photodiode. Its optical response is also designed to match the spectral response of the human eye. A second photodiode array, sensitive primarily to the infrared spectrum, is then used to match flourescent and incandescent light response from the part.

Two key features of the IC analog design are its ultra-low current consumption (typically 0.65µA) and an extremely wide dynamic light range that extends from 0.045 lux to 188,000 lux—more than a 4,000,000 to 1 range. The onchip autoranging scheme requires no user intervention for the gain-range setting.

The IC can be customized to operate at enhanced sensitivity in applications where it needs to operate behind a dark glass.

The default integration time of the ADC is 100ms, giving it inherent rejection of 50Hz and 60Hz ripple common in certain line-powered light sources.

# Human Eye CIE Curve and Different Light Sources

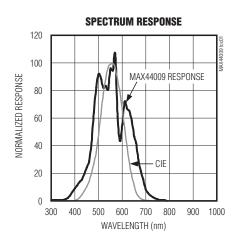

The IC is designed to detect brightness in the same way as human eyes do. To achieve this, the sensor needs to have a spectral sensitivity that is similar to that of human eyes. Figure 1 shows the spectral sensitivity of the IC and the human eye (CIE curve).

As can be seen, the human eye has its peak sensitivity at 555nm (green), while that of blue ( $\sim$ 470nm) and red ( $\sim$ 630nm) is much lower. The human eye also is blind to infrared (> 700nm) and ultraviolet (< 400nm) radiation.

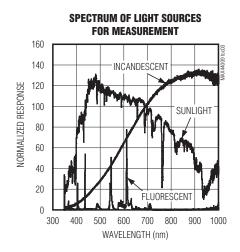

Light sources can have similar visible brightness (lux), but different IR radiation content (because the human eye is blind to it). The differences in the light spectra affect brightness measurement because some of this infrared radiation is picked up by silicon photodiodes. For example, light sources with high IR content, such as an incandescent bulb or sunlight, would suggest a much brighter environment than our eyes would perceive them to be. Other light sources, such as fluorescent and LED-based systems, have very little infrared content. The IC exhibits good IR rejection and internal IR compensation scheme to minimize these effects and give an accurate lux response.

Figure 1. Spectral Sensitivity of the MAX44009 and Human Eye

### Register and Bit Descriptions

Table 1. Register Map

| REGISTER                     |               |        |     | BIT |     |     |         |      | REGISTER | POWER-ON RESET |     |

|------------------------------|---------------|--------|-----|-----|-----|-----|---------|------|----------|----------------|-----|

| REGISTER                     | 7             | 6      | 5   | 4   | 3   | 2   | 1       | 0    | ADDRESS  | STATE          | R/W |

| STATUS                       |               |        |     | '   |     | ,   | ,       |      |          |                |     |

| Interrupt Status             | -             | _      | _   | _   | _   | _   | _       | INTS | 0x00     | 0x00           | R   |

| Interrupt Enable             | _             | _      | _   | _   | _   | _   | _       | INTE | 0x01     | 0x00           | R/W |

| CONFIGURATION                | CONFIGURATION |        |     |     |     |     |         |      |          |                |     |

| Configuration                | CONT          | MANUAL | _   | _   | CDR |     | TIM[2:0 | ]    | 0x02     | 0x03           | R/W |

| LUX READING                  |               |        |     |     |     |     |         |      |          |                |     |

| Lux High Byte                | E3            | E2     | E1  | E0  | M7  | M6  | M5      | M4   | 0x03     | 0x00           | R   |

| Lux Low Byte                 | _             | _      | _   | _   | МЗ  | M2  | M1      | MO   | 0x04     | 0x00           | R   |

| THRESHOLD SET                |               |        |     |     |     |     |         |      |          |                |     |

| Upper Threshold<br>High Byte | UE3           | UE2    | UE1 | UE0 | UM7 | UM6 | UM5     | UM4  | 0x05     | 0xFF           | R/W |

| Lower Threshold<br>High Byte | LE3           | LE2    | LE1 | LE0 | LM7 | LM6 | LM5     | LM4  | 0x06     | 0×00           | R/W |

| Threshold Timer              | T7            | T6     | T5  | T4  | T3  | T2  | T1      | T0   | 0x07     | 0xFF           | R/W |

#### **Interrupt Status 0x00**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | REGISTER<br>ADDRESS |

|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| _     | _     | _     | _     | _     | _     | _     | INTS  | 0x00                |

If the INTE bit is set to 1, then the INTS status bit is asserted if the light intensity exceeds either upper or lower threshold limits (as specified by registers 0x05 and 0x06, respectively) for a period longer than that defined by the Threshold Timer register (0x07). This bit resets to 0 after the host reads this register. See Table 2.

This bit is also reflected on the  $\overline{\text{INT}}$  pin. When the INTS bit is set, the  $\overline{\text{INT}}$  pin is asserted low, and when the INTS bit is set to 0, the  $\overline{\text{INT}}$  pin is pulled high by an external resistor.

Once this bit is set, it can be cleared either by reading the Interrupt Status register 0x00 or by writing a 0 to the Interrupt Enable register 0x01.

### **Table 2. Interrupt Status Register**

| BIT 0 | OPERATION                                                                                       |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0     | No interrupt trigger event has occurred.                                                        |  |  |  |  |  |

| 1     | Ambient light intensity is outside the threshold window range for a longer than specified time. |  |  |  |  |  |

#### **Interrupt Enable 0x01**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | REGISTER<br>ADDRESS |

|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| _     | _     | _     | _     | _     | _     | _     | INTS  | 0x01                |

# Industry's Lowest-Power Ambient Light Sensor with ADC

Interrupt events set the INTS bit (register 0x00, bit 0) and the  $\overline{\text{INT}}$  pin only if the INTE bit is set to 1. If the INTE bit is set (interrupt is enabled) and the interrupt condition is triggered, then the  $\overline{\text{INT}}$  pin is pulled low (asserted) and the INTS bit in the Interrupt Status register is set to 1. See Table 3.

### **Table 3. Interrupt Enable Register**

| BIT 0 | OPERATION                                                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The INT pin and the INTS bit are not asserted even if an interrupt event has occurred.                                              |

| 1     | Detection of an interrupt event triggers a hardware interrupt (INT pin is pulled low) and sets the INTS bit (register 0x00, bit 0). |

#### **Configuration 0x02**

| BIT 7 | BIT 6  | BIT 5 | BIT 4 | BIT 3 | BIT 2    | BIT 1 | BIT 0 | REGISTER<br>ADDRESS |

|-------|--------|-------|-------|-------|----------|-------|-------|---------------------|

| CONT  | MANUAL | _     | _     | CDR   | TIM[2:0] |       | 0x02  |                     |

#### Continuous Mode

### **Table 4. Continuous Mode Register**

| BIT 7 | OPERATION                                                                                                                                                                                                                                                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Default mode. The IC measures lux intensity only once every 800ms regardless of integration time. This mode allows the part to operate at its lowest possible supply current.                                                                                                                                                             |

| 1     | Continuous mode. The IC continuously measures lux intensity. That is, as soon as one reading is finished, a new one begins. If integration time is 6.25ms, readings are taken every 6.25ms. If integration time is 800ms, readings are taken every 800ms. In this mode, the part consumes slightly higher power than in the default mode. |

Note: Continuous mode is independent of the manual configuration mode setting.

#### Manual Configuration Mode

In automatic mode (MANUAL = 0), reading the contents of TIM[2:0] and CDR bits reflects the automatically generated values from an internal timing register and are read-only. In manual mode (MANUAL = 1), the contents of TIM[2:0] and CDR bits can be modified by the users through the I2C bus.

### **Table 5. Manual Configuration Register**

| BIT 6 | OPERATION                                                                                                                                                        |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Default mode of configuration is used for the IC. In this mode, CDR, TIM[2:0] bits are automatically determined by the internal autoranging circuitry of the IC. |

| 1     | Manual mode of configuration is used for the IC. In this mode, CDR, and TIM[2:0] bits can be programmed by the user.                                             |

#### Current Division Ratio (CDR)

The CDR bit controls the current division ratio. The photodiode current is divided as shown in Table 6.

#### **Table 6. Current Division Ratio Register**

| BIT 3 | OPERATION                                                                                                                  |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| 0     | Current not divided. All of the photodiode current goes to the ADC.                                                        |

| 1     | Current divided by 8. Only 1/8 of the photodiode current goes to the ADC. This mode is used in high-brightness situations. |

Integration Timer Bits (TIM[2:0])

The TIM[2:0] bits can be used to program the signal integration time.

In automatic mode (MANUAL = 0), integration time is automatically selected by the on-chip algorithm to be either 100 ms/200 ms/400 ms/800 ms. In manual mode, integration time can be varied by the user all the way from 6.25 ms to 800 ms. See Table 7.

### **Table 7. Integration Time**

| TIM[2:0] | INTEGRATION<br>TIME (ms) | COMMENTS                                                     |

|----------|--------------------------|--------------------------------------------------------------|

| 000      | 800                      | This is a preferred mode for boosting low-light sensitivity. |

| 001      | 400                      |                                                              |

| 010      | 200                      | _                                                            |

| 011      | 100                      | This is a preferred mode for high-brightness applications.   |

| 100      | 50                       | Manual mode only.                                            |

| 101      | 25                       | Manual mode only.                                            |

| 110      | 12.5                     | Manual mode only.                                            |

| 111      | 6.25                     | Manual mode only.                                            |

#### Lux High-Byte Register 0x03

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | REGISTER<br>ADDRESS |

|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| E3    | E2    | E1    | E0    | M7    | M6    | M5    | M4    | 0x03                |

Bits in Lux High-Byte register 0x03 give the 4 bits of exponent E3:E0 and 4 most significant bits of the mantissa byte M7:M4, and represent the lux reading of ambient light. The remaining 4 bits of the mantissa byte M3:M0 are in the Lux Low-Byte register 0x04 and enhance resolution of the lux reading from the IC.

Exponent (E[3:0]): Exponent bits of the lux reading (0000 to 1110). **Note:** A reading of 1111 represents an overrange condition.

Mantissa (M[7:4]): Four most significant bits of mantissa byte of the lux reading (0000 to 1111).

$Lux = 2^{(exponent)} x mantissa x 0.72$

Exponent = 8xE3 + 4xE2 + 2xE1 + E0

Mantissa = 8xM7 + 4xM6 + 2xM5 + M4

A code of 0000 0001 calculates to be 0.72 lux.

A code of 1110 1111 calculates to be 176,947 lux.

A code of 1110 1110 calculates to be 165,151 lux.

Update of the contents of this register is internally disabled during I<sup>2</sup>C read operations to ensure proper data transfer between internal ADC and I<sup>2</sup>C registers. Update of I<sup>2</sup>C registers is resumed when the master sends a STOP command.

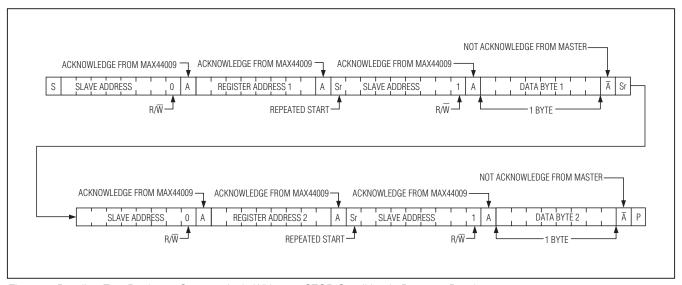

If user wants to read both the Lux High-Byte register 0x03 and Lux Low-Byte register 0x04, then the master should not send a STOP command between the reads of the two registers. Instead a Repeated START command should be used. This ensures accurate data is obtained from the I<sup>2</sup>C registers (by disabling internal updates during the read process).

# Industry's Lowest-Power Ambient Light Sensor with ADC

#### Lux Low-Byte Register 0x04

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | REGISTER<br>ADDRESS |

|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| _     | _     | _     | _     | M3    | M2    | M1    | MO    | 0x04                |

Bits in Lux Low-Byte register 0x04 give the 4 least significant bits of the mantissa byte representing the lux reading of ambient light. Combined with the Lux High-Byte register 0x03, it extends the resolution and dynamic range of lux measurements of the IC.

E3-E0: Exponent bits of lux reading

M7-M0: Mantissa byte of lux reading

$Lux = 2^{(exponent)} x mantissa x 0.045$

Exponent = 8xE3 + 4xE2 + 2xE1 + E0

Mantissa = 128xM7 + 64xM6 + 32xM5 + 16xM4 + 8xM3 + 4xM2 + 2xM1 + M0

Combining contents of register 0x03 and 0x04:

A code of 0000 0000 0001 calculates to be 0.045 lux.

A code of 0000 0001 0000 calculates to be 0.72 lux.

A code of 0001 0001 0001 calculates to be 0.765 lux.

A code of 1110 1111 1111 calculates to be 188,006 lux.

A code of 1110 1111 1110 calculates to be 187,269 lux.

The Lux High-Byte 0x03 and Lux Low-Byte 0x04 register updates are internally disabled at the start of a valid address transmission from the master. Updating reinitiates at the next valid STOP condition. This prevents erroneous readings in the event an update occurs between readings of registers 0x03 and 0x04.

Update of the contents of this register is internally disabled during I<sup>2</sup>C read operations to ensure proper data transfer between internal ADC and I<sup>2</sup>C registers. Update of I<sup>2</sup>C registers is resumed when the master sends a STOP command.

If the user wants to read both the Lux High-Byte register 0x03 and Lux Low-Byte register 0x04, then the master should not send a STOP command between the reads of the two registers. Instead a Repeated START command should be used. This ensures accurate data is obtained from the I<sup>2</sup>C registers (by disabling internal updates during the read process).

#### **Upper Threshold High-Byte Register 0x05**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | REGISTER<br>ADDRESS |

|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| UE3   | UE2   | UE1   | UE0   | UM7   | UM6   | UM5   | UM4   | 0x05                |

The Upper Threshold High-Byte register exponent with the four most significant bits of the mantissa sets the upper trip level for interrupt functionality. This upper limit is relevant only if the INTE bit in the interrupt enable register is set. If the lux level is greater than this light level for a time greater than that specified in the Threshold Timer register, the INTS bit in the Interrupt Status register is set and the  $\overline{\text{INT}}$  pin is pulled low.

Mantissa (UM[7:4]): Four most significant bits of mantissa upper threshold

Exponent (UE[3:0]): Exponent bits upper threshold

Upper lux threshold =  $2^{\text{(exponent)}}$  x mantissa x 0.045

Exponent = 8xUE3 + 4xUE2 + 2xUE1 + UE0

Mantissa = 128xUM7+ 64xUM6+ 32xUM5 + 16xUM4 + 15

### Lower Threshold High-Byte Register 0x06

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | REGISTER<br>ADDRESS |

|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| LE3   | LE2   | LE1   | LE0   | LM7   | LM6   | LM5   | LM4   | 0x06                |

The Lower Threshold High-Byte register exponent with the four most significant bits of the mantissa sets the lower trip level for interrupt functionality. This lower limit is relevant only if the INTE bit in the Interrupt Enable register is set. If the lux level is below this light level for a time greater than that specified in the Threshold Timer register, the INTS bit in the Interrupt Status register is set and the  $\overline{\rm INT}$  pin is pulled low.

Mantissa (LM[7:4]): Four most significant bits of mantissa lower threshold

Exponent (LE[3:0]): Exponent bits lower threshold Lower lux threshold =  $2^{\text{(exponent)}}$  x mantissa x 0.045

Exponent = 8xLE3 + 4xLE2 + 2xLE1 + LE0

Mantissa = 128xLM7 + 64xLM6 + 32xLM5 + 16xLM4

#### **Threshold Timer Register 0x07**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | REGISTER<br>ADDRESS |

|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| T7    | T6    | T5    | T4    | T3    | T2    | T1    | TO    | 0x07                |

If the INTE bit = 1 and the ambient light level exceed either threshold limit for a time longer than that specified by the Threshold Timer register, then the INTS bit is set to 1 and the  $\overline{\text{INT}}$  pin is pulled low.

The value in this register sets the time used to control this delay. A value of 0x00 in this register (with INTE bit = 1 in the Interrupt Enable register) configures the IC to assert the interrupt pin as soon as the light level exceeds either threshold. Time delay =  $(128xT7 + 64xT6 + 32xT5 + 16xT4 + 8xT3 + 4xT2 + 2xT1 + T0) \times 100ms$ .

### **Applications Information**

#### **Auto and Manual Modes**

In auto mode configuration (default setting), CDR and TIM bits are internally generated. The autoranging circuit uses two different methods to change its sensitivity. For light intensities greater than 700 lux, a current divider reduces the photodiode's current by a factor of 8. The default, as in the previous example, is a division of 1: current goes directly into the I-to-F converter. As light intensity decreases, the autoranging circuit increases the integration time from 100ms to 200ms to 400ms, or to 800ms. The combination of the current divider and the different integration times give the A/D a range 8 times higher, as well as 8 times lower, than its nominal 16-bit range. This gives a dynamic range of 22 bits or slightly over 4,000,000 to 1.

In manual mode, the user has access to 4 bits (CDR and TIM[2:0]) to override the autoranging circuitry. These affect the integration time of the A/D and the current division ratio. See the register description for manual configuration mode (0x02, bit 6).

#### **Data Format of Lux Reading**

The IC has a user-friendly digital output format. It consists of a 4-bit exponent followed by an 8-bit mantissa. In its highest sensitivity mode, 1 count represents 0.045 lux. The mantissa has a maximum value of 255, and the exponent has a maximum value of 14. This gives a maximum range:  $255 \times 214 = 4,177,920$ . At 0.045 lux/LSB, the maximum lux reading is 188,000 lux. Any reading greater than that (i.e., exponent = 15) is considered to be an overload. No conversion formulas are needed as in the case of dual-diode ambient light sensors.

The IC's output (registers 0x03 and 0x04) comprises a 12-bit result that represents the ambient light expressed in units of lux.

Here is how lux is calculated:

$Lux = (2^{(exponent)} x mantissa) x 0.045$

The exponent is a 4-bit number ranging from 0000 to 1110 (zero to 14).

The mantissa is an 8-bit number ranging from 0000 0000 to 1111 1111 (zero to 255).

# Industry's Lowest-Power Ambient Light Sensor with ADC

The count is multiplied by 0.045, which is the LSB.

Because of the logarithmic nature of autoranging circuitry implemented on the IC, resolution of ambient lux readings scale with the absolute measurement. Table 8 lists the lux resolution and the lux ranges obtained from the IC

#### **Interrupt Settings**

Interrupt is enabled by setting bit 0 of register 0x01 to 1 (see Table 1).  $\overline{\text{INT}}$ , an open-drain output, pulls low when an interrupt condition occurs (lux readings that exceed threshold limits for a period greater than that set by the Threshold Timer register). The interrupt status bit is cleared automatically if register 0x00 is read or if the interrupt is disabled (INTE = 0).

#### **Threshold Register Data Format**

The IC's interrupt circuit requires the upper and lower limit thresholds to be in a specific format to be properly interpreted. The upper and lower limits, from registers 0x05 and 0x06 must match the lux high-byte format. This consists of the 4 bits of the exponent and the 4 most significant bits of the mantissa (E3 E2 E1 E0 M7 M6 M5 M4).

In this case, there is the following formula:

Lower lux threshold =  $(2^{(exponent)} \times mantissa) \times 0.045$ The exponent is a 4-bit number ranging from 0000 to 1110 (zero to 14). The mantissa is an 8-bit number ranging from 0000 0000 to 1111 0000 (zero to 240).

Upper lux threshold =  $(2^{(exponent)} \times mantissa) \times 0.045$ The exponent is a 4-bit number ranging from 0000 to 1110 (zero to 14).

The mantissa is an 8-bit number ranging from 0000 1111 to 1111 1111 (15 to 255).

In the auto range mode (MANUAL = 0), the upper threshold and lower threshold bytes must be in a format that matches the format used in register 0x03, the lux high byte. There are only two rules to follow:

- For very low lux levels (light levels below 11.5 lux), set the exponent to zero, the code is merely: 0000 MMMM where the 4 zeroes are the exponent, and the MMMM represent the 4 most significant bits of the mantissa.

- For all other conditions (light levels above 11.5 lux) where the exponent is not zero, the format is: EEEE 1MMM. Notice that bit M7 (most significant bit) must always be a 1. The other bits do not matter. EEEE is limited to a maximum value of 1110. The maximum usable setting is a code of 1110 1111.

In manual mode (MANUAL = 1), Table 9 gives the range of exponent (E3 E2 E1 E0) that can be used for each TIM[2:0] and CDR bit setting.

Table 8. Lux per LSB in Automatic Mode

| LUX (MIN) | LUX (MAX) | LUX PER LSB IN<br>AUTOMATIC MODE | COUNTS (MIN) | COUNTS (MAX) |

|-----------|-----------|----------------------------------|--------------|--------------|

| 0         | 11.5      | 0.045                            | 0            | 256          |

| 11.5      | 23.0      | 0.09                             | 256          | 512          |

| 23.0      | 46.1      | 0.18                             | 512          | 1024         |

| 46.1      | 92.2      | 0.36                             | 1024         | 2048         |

| 92.2      | 184.3     | 0.72                             | 2048         | 4096         |

| 184.3     | 368.6     | 1.44                             | 4096         | 8192         |

| 368.6     | 737.3     | 2.88                             | 8192         | 16,384       |

| 737.3     | 1474.6    | 5.76                             | 16,384       | 32,768       |

| 1474.6    | 2949.1    | 11.52                            | 32,768       | 65,536       |

| 2949.1    | 5898.2    | 23.04                            | 65,536       | 131,072      |

| 5898.2    | 11,796.5  | 46.08                            | 131,072      | 262,144      |

| 11,796.5  | 23,593.0  | 92.16                            | 262,144      | 524,288      |

| 23,593.0  | 47,185.9  | 184.32                           | 524,288      | 1,048,576    |

| 47,185.9  | 94,371.8  | 368.64                           | 1,048,576    | 2,097,152    |

| 94,371.8  | 188,006.4 | 737.28                           | 2,097,152    | 4,177,920    |

Table 9. Recommended Manual Mode Settings for Configuration Register (0x02) and Threshold Registers (0x05, 0x06)

|                  | APPLICATIO   | ON CONDITIO      | DNS                      | FOR CONF | ED SETTINGS<br>IGURATION<br>ER (0x03) | RANGE OF EXPONENTS FOR<br>UPPER AND LOWER REGISTERS<br>(0x05 AND 0x06) |                   |  |

|------------------|--------------|------------------|--------------------------|----------|---------------------------------------|------------------------------------------------------------------------|-------------------|--|

| LUX LSB<br>(MIN) | LUX<br>(MAX) | LUX LSB<br>(MAX) | INTEGRATION<br>TIME (ms) | TIM      | CDR                                   | EXPONENT<br>(MIN)                                                      | EXPONENT<br>(MAX) |  |

| 0.045            | 2938         | 11.52            | 800                      | 000      | 0                                     | 0000                                                                   | 1000              |  |

| 0.09             | 5875         | 23.04            | 400                      | 001      | 0                                     | 0001                                                                   | 1001              |  |

| 0.18             | 11,750       | 46.08            | 200                      | 010      | 0                                     | 0010                                                                   | 1010              |  |

| 0.26             | 22 501       | 00.16            | 100                      | 011      | 0                                     | 0011                                                                   | 1011              |  |

| 0.36             | 23,501       | 92.16            | 800                      | 000      | 1                                     | 0011                                                                   | 1011              |  |

| 0.70             | 47.000       | 104.00           | 50                       | 100      | 0                                     | 0100                                                                   | 1100              |  |

| 0.72             | 47,002       | 184.32           | 400                      | 001      | 1                                     | 0100                                                                   | 1100              |  |

| 1.44             | 04.000       | 200.04           | 25                       | 101      | 0                                     | 0101                                                                   | 1101              |  |

| 1.44             | 94,003       | 368.64           | 200                      | 010      | 1                                     | 0101                                                                   | 1101              |  |

| 0.00             | 100.000      | 707.00           | 12.5                     | 110      | 0                                     | 0110                                                                   | 4440              |  |

| 2.88             | 188,006      | 737.28           | 100                      | 011      | 1                                     | 0110                                                                   | 1110              |  |

| F 70             | 100.000      | 707.00           | 6.25                     | 111      | 0                                     | 0444                                                                   | 4440              |  |

| 5.76             | 188,006      | 737.28           | 50                       | 100      | 1                                     | 0111                                                                   | 1110              |  |

| 11.52            | 188,006      | 737.28           | 25                       | 101      | 1                                     | 1000                                                                   | 1110              |  |

| 23.04            | 188,006      | 737.28           | 12.5                     | 110      | 1                                     | 1001                                                                   | 1110              |  |

| 46.08            | 188,006      | 737.28           | 6.25                     | 111      | 1                                     | 1010                                                                   | 1110              |  |

Note: In manual mode, exceeding the lux (max) causes an overload error (exponent = 1111).

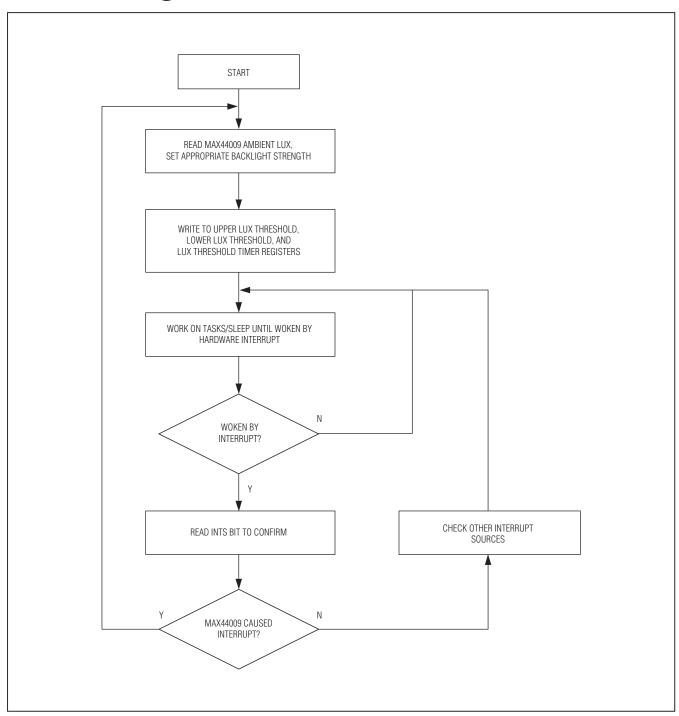

#### **Typical Operating Sequence**

To utilize the ultra-low power consumption of the IC in end applications, an interrupt pin is provided to eliminate the need for the system to poll the device continuously. Since every clock and data bit transmitted on I²C can consume up to 1mA (assuming 1.8k $\Omega$  pullup resistor to a 1.8V rail), minimizing the number of I²C transactions on the data bus can save a lot of power. In addition, eliminating the need to poll the device frees up processing resources for the master, improving overall system performance.

The typical sequence of communication with the IC is as follows:

1) Master reads lux reading from registers 0x03 and 0x04.

- Master sets the upper lux threshold and lower lux threshold in registers 0x05 and 0x06 so that a userprogrammed window is defined around the current lux readings.

- 3) Master sets suitable threshold timer data in register

- 4) Master works on other tasks until alerted by the INT pin going low. This is where the master spends much of its time.

- 5) When alerted by the INT pin going low, the master reads the Interrupt Status register 0x00 to confirm the source of interrupt was the IC. The master takes appropriate action.

6) Repeat from Step 1.

# Industry's Lowest-Power Ambient Light Sensor with ADC

Figure 2. Typical Operating Sequence

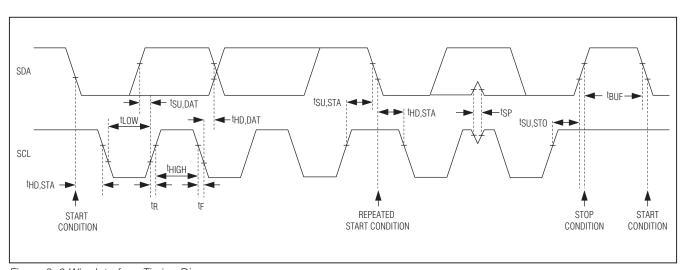

#### I<sup>2</sup>C Serial Interface

The IC features an I2C/SMBus™-compatible, 2-wire serial interface consisting of a serial-data line (SDA) and a serial-clock line (SCL). SDA and SCL facilitate communication between the IC and the master at clock rates up to 400kHz. Figure 3 shows the 2-wire interface timing diagram. The master generates SCL and initiates data transfer on the bus. A master device writes data to the IC by transmitting the proper slave address followed by the register address and then the data word. Each transmit sequence is framed by a START (S) or Repeated START (Sr) condition and a STOP (P) condition. Each word transmitted to the IC is 8 bits long and is followed by an acknowledge clock pulse. A master reading data from the IC transmits the proper slave address followed by a series of nine SCL pulses. The IC transmits data on SDA in sync with the master-generated SCL pulses. The master acknowledges receipt of each byte of data. Each read sequence is framed by a START or Repeated START condition, a not acknowledge, and a STOP condition. SDA operates as both an input and an open-drain output. A pullup resistor, typically greater than  $500\Omega$ , is required on the SDA bus. SCL operates as only an input. A pullup resistor, typically greater than  $500\Omega$ , is required on SCL if there are multiple masters on the bus, or if the master in a single-master system has an open-drain SCL output. Series resistors in line with SDA and SCL are optional. Series resistors protect the digital inputs of the IC from high-voltage spikes on the bus lines, and minimize crosstalk and undershoot of the bus signals.

#### **Bit Transfer**

One data bit is transferred during each SCL cycle. The data on SDA must remain stable during the high period of the SCL pulse. Changes in SDA while SCL is high are control signals (see the *START* and *STOP Conditions* section). SDA and SCL idle high when the I2C bus is not busy.

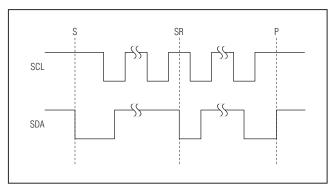

#### **START and STOP Conditions**

SDA and SCL idle high when the bus is not in use. A master initiates communication by issuing a START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA while SCL is high (Figure 4). A START condition from the master signals the beginning of a transmission to the IC. The master terminates transmission, and frees the bus by issuing a STOP condition. The bus remains active if a REPEATED START condition is generated instead of a STOP condition.

#### **Early STOP Conditions**

The IC recognizes a STOP condition at any point during data transmission except if the STOP condition occurs in the same high pulse as a START condition. For proper operation, do not send a STOP condition during the same SCL high pulse as the START condition.

Figure 3. 2-Wire Interface Timing Diagram

SMBus is a trademark of Intel Corp.

# Industry's Lowest-Power Ambient Light Sensor with ADC

Figure 4. START, STOP, and Repeated START Conditions

### Slave Address

The slave address is controlled by the A0 pin. Connect A0 to either ground or V<sub>CC</sub> to set the address. Table 10 shows the two possible addresses for the IC.

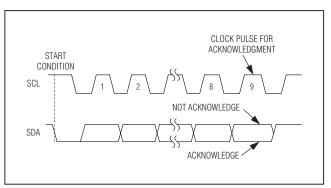

#### **Acknowledge**

The acknowledge bit (ACK) is a clocked 9th bit that the IC uses to handshake receipt each byte of data when in write mode (see Figure 5). The IC pulls down SDA during the entire master-generated ninth clock pulse if the previous byte is successfully received. Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master can retry communication. The master pulls down SDA during the ninth clock cycle to acknowledge receipt of data when the IC is in read mode. An acknowledge is sent by the master after each read byte to allow data transfer to continue. A not acknowledge is sent when the master reads the final byte of data from the IC, followed by a STOP condition.

#### **Write Data Format**

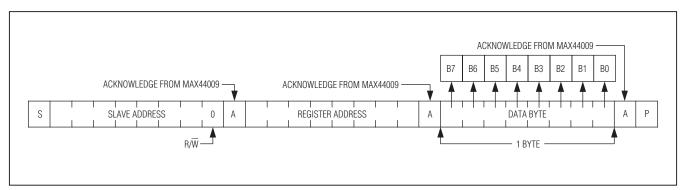

A write to the IC includes transmission of a START condition, the slave address with the  $R/\overline{W}$  bit set to 0, 1 byte of data to configure the internal register address pointer, 1 or more bytes of data, and a STOP condition. Figure 6 illustrates the proper frame format for writing 1 byte of data to the IC.

Table 10. Slave Address

| Α0  | SLAVE ADDRESS<br>FOR WRITING | SLAVE ADDRESS<br>FOR READING |

|-----|------------------------------|------------------------------|

| GND | 1001 0100                    | 1001 0101                    |

| Vcc | 1001 0110                    | 1001 0111                    |

Figure 5. Acknowledge

The slave address with the  $R/\overline{W}$  bit set to 0 indicates that the master intends to write data to the IC. The IC acknowledges receipt of the address byte during the master-generated ninth SCL pulse.

The second byte transmitted from the master configures the IC's internal register address pointer. The pointer tells the IC where to write the next byte of data. An acknowledge pulse is sent by the IC upon receipt of the address pointer data.

The third byte sent to the IC contains the data that is written to the chosen register. The master signals the end of transmission by issuing a STOP condition.

#### Read Data Format

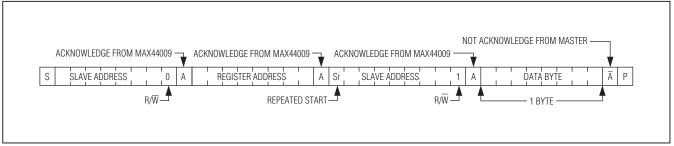

To read a byte of data, the register pointer must first be set through a write operation (Figure 7). Send the slave address with the R/W set to 0, followed by the address of the register that needs to be read. After a Repeated START condition, send the slave address with the R/W bit set to 1 to initiate a read operation. The IC then sends an acknowledge pulse followed by the contents of the register to be read. Transmitted data is valid on the rising edge of the master-generated serial clock (SCL).

Figure 8 illustrates the frame format for reading two registers consecutively without a STOP condition in between reads. This applies to reading the Lux Data registers 0x03 and 0x04 consecutively only.

#### **Sensor Position**

The photo sensitive area of the IC is 0.37mm x 0.37mm and much smaller than the device itself. When placing the part behind a light guide, only this sensitive area has to be taken into account. Figure 9 shows the position and size of the photo-sensitive area within the package.

# Industry's Lowest-Power Ambient Light Sensor with ADC

Figure 6. Writing 1 Byte of Data to the IC

Figure 7. Reading 1 Indexed Byte of Data from the IC

Figure 8. Reading Two Registers Consecutively Without a STOP Condition in Between Reads

# Industry's Lowest-Power Ambient Light Sensor with ADC

Figure 9. Sensor Position

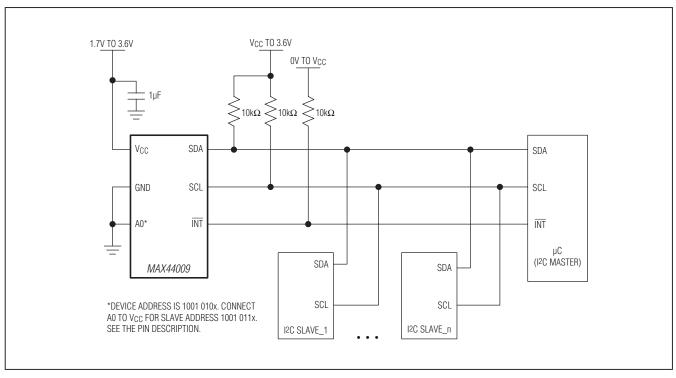

## **Typical Application Circuit**

**Chip Information**

PROCESS: BICMOS

# Industry's Lowest-Power Ambient Light Sensor with ADC

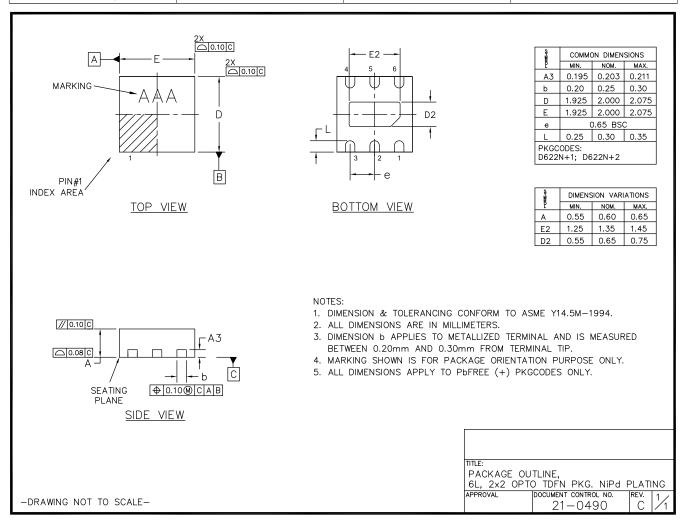

### **Package Information**

For the latest package outline information and land patterns, go to <u>www.maxim-ic.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO. |

|--------------|--------------|----------------|------------------|

| 6 UTDFN-Opto | D622+1       | <u>21-0490</u> | 90-0344          |

# Industry's Lowest-Power Ambient Light Sensor with ADC

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 1/11          | Initial release | _                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated Products:

MAX44009EDT+T MAX44009PMB1#