# i.MX23 Applications Processor Reference Manual

IMX23RM Rev. 1 11/2009

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or

+1-480-768-2130

www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd.

Exchange Building 23F

No. 118 Jianguo Road

Chaoyang District

Beijing 100022

China

+86 010 5879 8000

support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

+1-800 441-2447 or

+1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor

@ hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks or registered trademarks of Freescale Semiconductor, Inc. in the U.S. and other countries. All other product or service names are the property of their respective owners. ARM is the registered trademark of ARM Limited. ARM926EJ-S is the trademark of ARM Limited.

© Freescale Semiconductor, Inc., 2009. All rights reserved.

Document Number: IMX23RM

Rev. 1, 11/2009

Paragraph Page Number Title Number

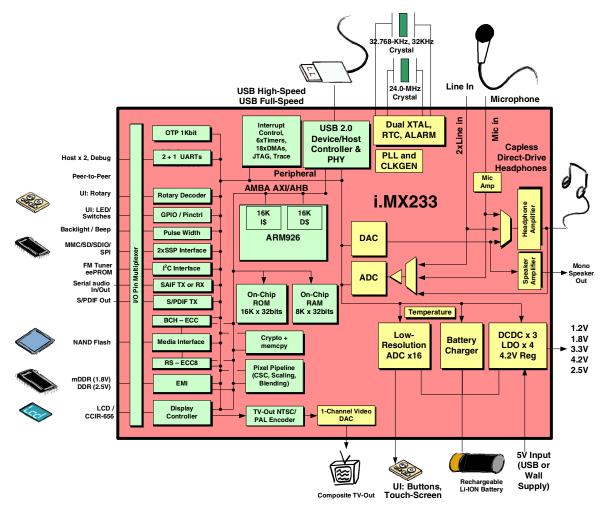

# Chapter 1 Product Overview

| 1.1      | Hardware Features                                                  | 1-2  |

|----------|--------------------------------------------------------------------|------|

| 1.2      | i.MX23 Product Features                                            | 1-5  |

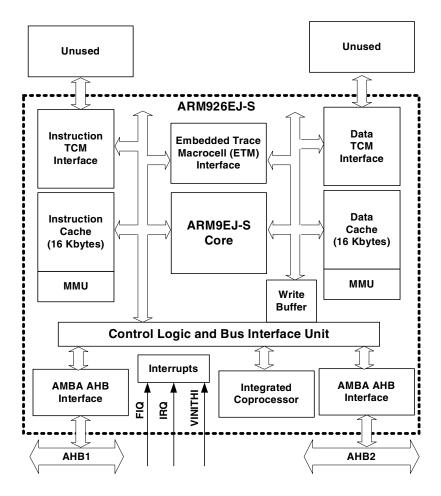

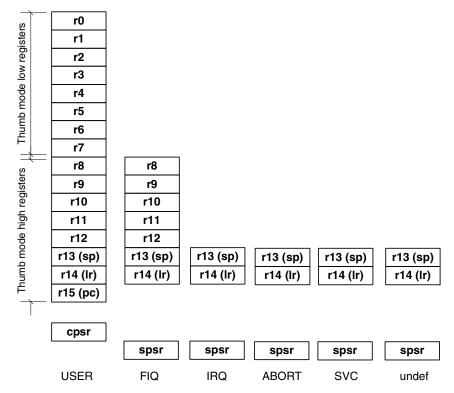

| 1.2.1    | ARM 926 Processor Core                                             | 1-7  |

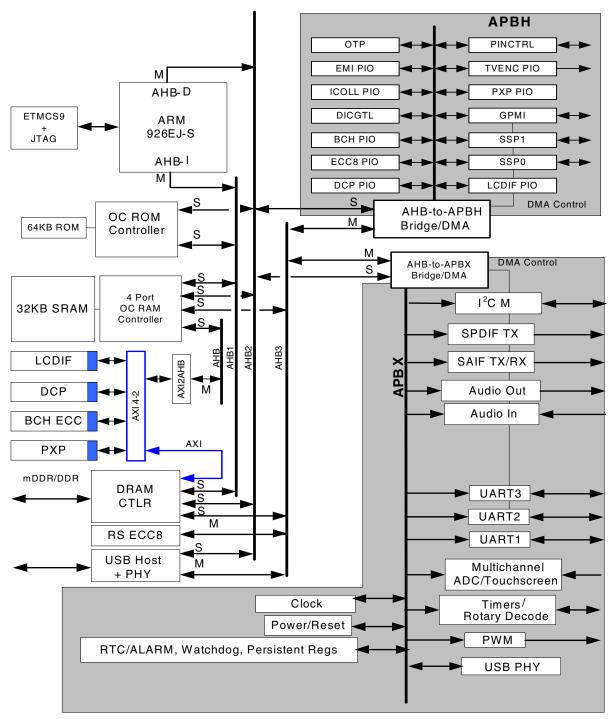

| 1.2.2    | System Buses                                                       | 1-7  |

| 1.2.2.1  | AXI Bus                                                            | 1-9  |

| 1.2.2.2  | AHB Bus                                                            | 1-9  |

| 1.2.2.3  | APB Buses                                                          | 1-9  |

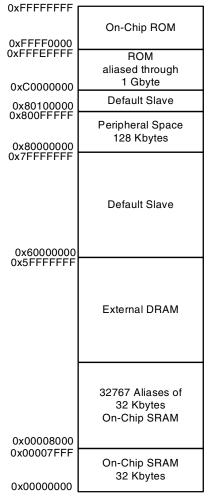

| 1.2.3    | On-Chip RAM and ROM                                                | 1-10 |

| 1.2.4    | External Memory Interface                                          | 1-10 |

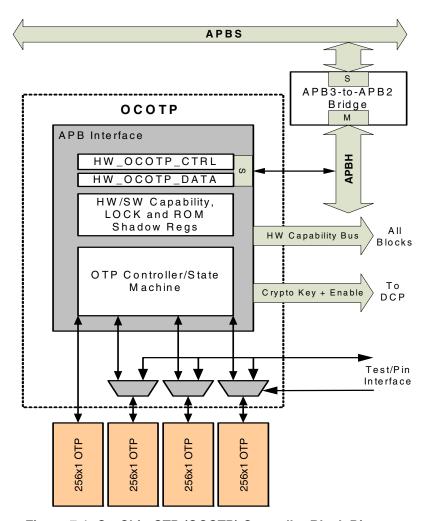

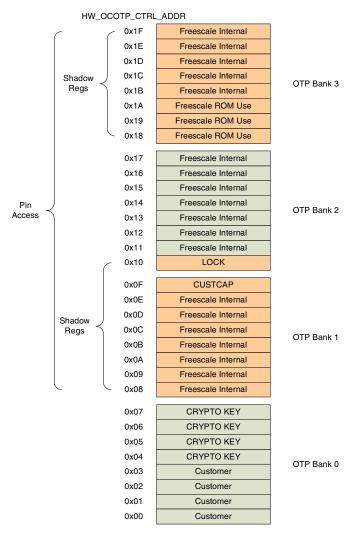

| 1.2.5    | On-Chip One-Time-Programmable (OCOTP) ROM                          | 1-12 |

| 1.2.6    | Interrupt Collector                                                |      |

| 1.2.7    | DMA Controller                                                     | 1-12 |

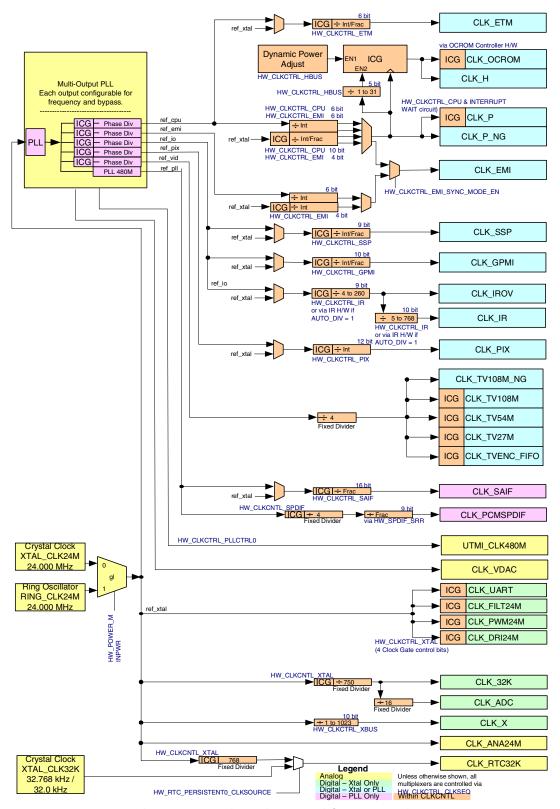

| 1.2.8    | Clock Generation Subsystem                                         | 1-13 |

| 1.2.9    | Power Management Unit                                              | 1-13 |

| 1.2.10   | USB Interface                                                      | 1-14 |

| 1.2.11   | General-Purpose Media Interface (GPMI)                             | 1-15 |

| 1.2.12   | Hardware Acceleration for ECC for Robust External Storage          |      |

| 1.2.12.1 | Reed-Solomon ECC Engine                                            | 1-16 |

| 1.2.12.2 | Bose Ray-Choudhury Hocquenghem ECC Engine                          | 1-16 |

| 1.2.13   | Data Co-Processor (DCP)—Memory Copy, Crypto,                       |      |

|          | and Color-Space Converter                                          | 1-17 |

| 1.2.14   | Mixed Signal Audio Subsystem                                       | 1-17 |

| 1.2.15   | Master Digital Control Unit (DIGCTL)                               | 1-19 |

| 1.2.16   | Synchronous Serial Port (SSP)                                      | 1-19 |

| 1.2.17   | I <sup>2</sup> C Interface                                         |      |

| 1.2.18   | General-Purpose Input/Output (GPIO)                                |      |

| 1.2.19   | Display Processing                                                 |      |

| 1.2.19.1 | Display Controller / LCD Interface (LCDIF)                         | 1-20 |

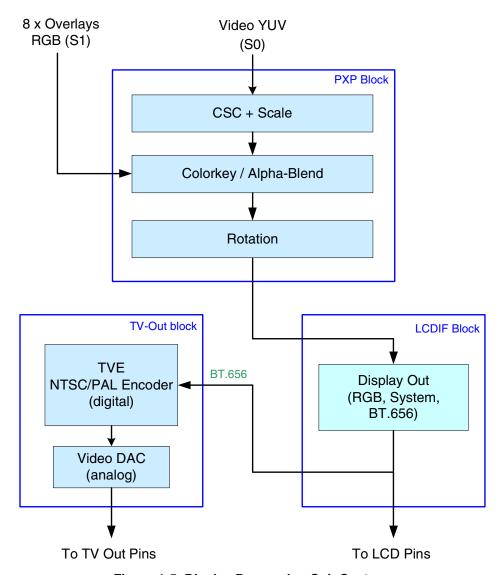

| 1.2.19.2 | Pixel Processing Pipeline (PXP)                                    | 1-21 |

| 1.2.19.3 | PAL/NTSC TV-Encoder                                                | 1-21 |

| 1.2.19.4 | Video DAC                                                          | 1-22 |

| 1.2.20   | SPDIF Transmitter                                                  | 1-22 |

| 1.2.21   | Dual Serial Audio Interfaces                                       | 1-22 |

| 1.2.22   | Timers and Rotary Decoder                                          | 1-22 |

| 1.2.23   | UARTs                                                              |      |

| 1.2.24   | Low-Resolution ADC, Touch-Screen Interface, and Temperature Sensor | 1-23 |

| 1.2.25   | Pulse Width Modulator (PWM) Controller                             |      |

|          |                                                                    |      |

| Paragraph<br>Number | Title                                                       | Page<br>Number |

|---------------------|-------------------------------------------------------------|----------------|

| 1.2.26              | Real-Time Clock, Alarm, Watchdog, Persistent Bits           | 1-24           |

|                     | Chapter 2                                                   |                |

|                     | Characteristics and Specifications                          |                |

| 2.1                 | Absolute Maximum Ratings                                    | 2-1            |

| 2.2                 | Recommended Operating Conditions                            | 2-2            |

| 2.3                 | DC Characteristics                                          | 2-4            |

| 2.3.1               | Recommended Operating Conditions for Specific Clock Targets | 2-9            |

| 2.4                 | AC Characteristics                                          |                |

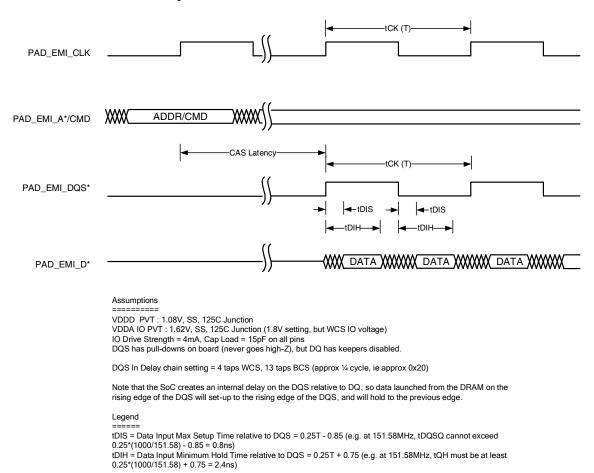

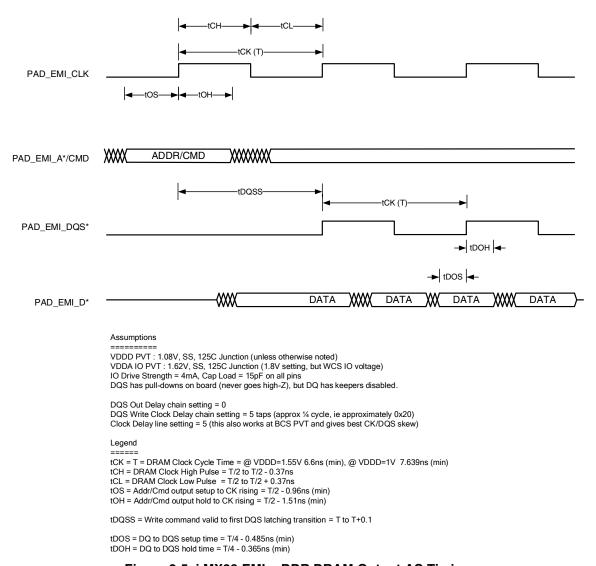

| 2.4.1               | EMI Electrical Specifications                               | 2-12           |

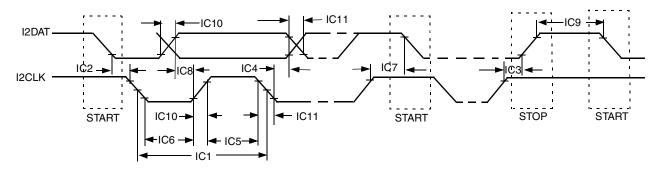

| 2.4.2               | I <sup>2</sup> C Electrical Specifications                  | 2-14           |

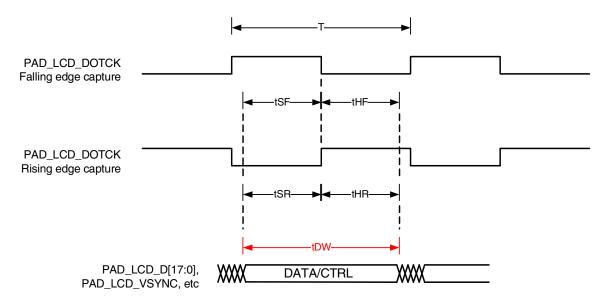

| 2.4.3               | LCD AC Output Electrical Specifications                     | 2-15           |

|                     | Chapter 3                                                   |                |

|                     | ARM CPU Complex                                             |                |

| 3.1                 | ARM 926 Processor Core                                      | 3-1            |

| 3.2                 | JTAG Debugger                                               | 3-3            |

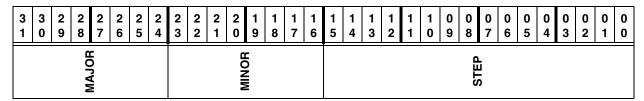

| 3.2.1               | JTAG READ ID                                                | 3-3            |

| 3.2.2               | JTAG Hardware Reset                                         | 3-3            |

| 3.2.3               | JTAG Interaction with CPUCLK                                | 3-4            |

| 3.3                 | Embedded Trace Macrocell (ETM) Interface (169BGA-only)      | 3-4            |

|                     | Chapter 4                                                   |                |

|                     | Clock Generation and Control                                |                |

| 4.1                 | Overview                                                    | 4-1            |

| 4.2                 | Clock Structure                                             | 4-1            |

| 4.2.1               | Table of System Clocks                                      | 4-2            |

| 4.2.2               | Logical Diagram of Clock Domains                            | 4-4            |

| 4.2.3               | Clock Domain Description                                    | 4-5            |

| 4.2.3.1             | CLK_P, CLK_H                                                | 4-5            |

| 4.2.3.2             | CLK_EMI                                                     | 4-6            |

| 4.2.3.3             | System Clocks                                               | 4-6            |

| 4.3                 | CLKCTRL Digital Clock Divider                               | 4-6            |

| 4.3.1               | Integer Clock Divide Mode                                   |                |

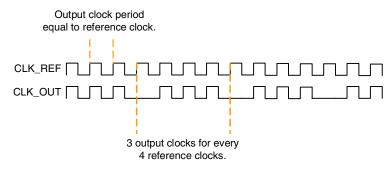

| 4.3.2               | Fractional Clock Divide Mode                                |                |

| 4.3.2.1             | Fractional Clock Divide Example, Divide by 3.5              | 4-7            |

| 4.3.2.1.1           | Fractional ClockDivide Example, Divide by 3/8               |                |

| 4.3.3               | Gated Clock Divide Mode                                     | 4-8            |

|                     |                                                             |                |

| Paragraph<br>Number                                                                     | Title                                                                                                                                                                                                                                                                   | Page<br>Number                  |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 4.4                                                                                     | Clock Frequency Management                                                                                                                                                                                                                                              | 4-9                             |

| 4.5                                                                                     | Analog Clock Control                                                                                                                                                                                                                                                    | 4-9                             |

| 4.6                                                                                     | CPU and EMI Clock Programming                                                                                                                                                                                                                                           |                                 |

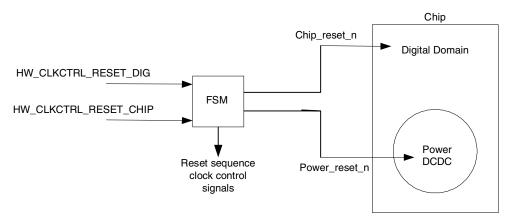

| 4.7                                                                                     | Chip Reset                                                                                                                                                                                                                                                              |                                 |

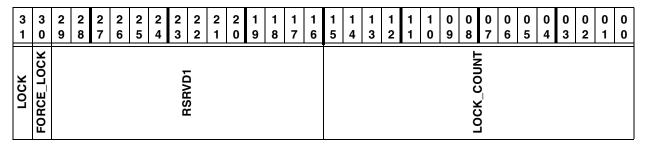

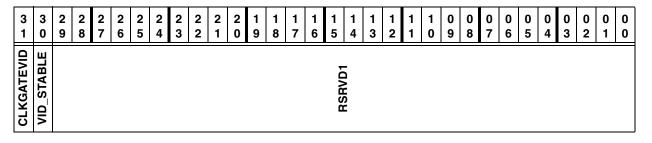

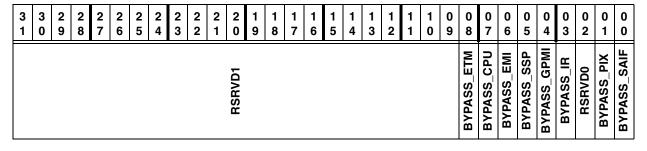

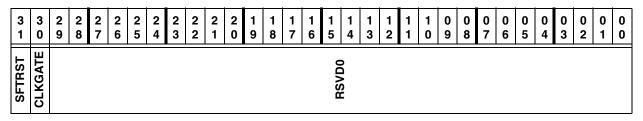

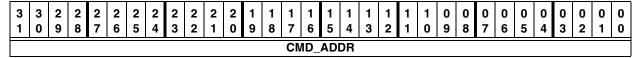

| 4.8                                                                                     | Programmable Registers                                                                                                                                                                                                                                                  | 4-11                            |

|                                                                                         | Chapter 5<br>Interrupt Collector                                                                                                                                                                                                                                        |                                 |

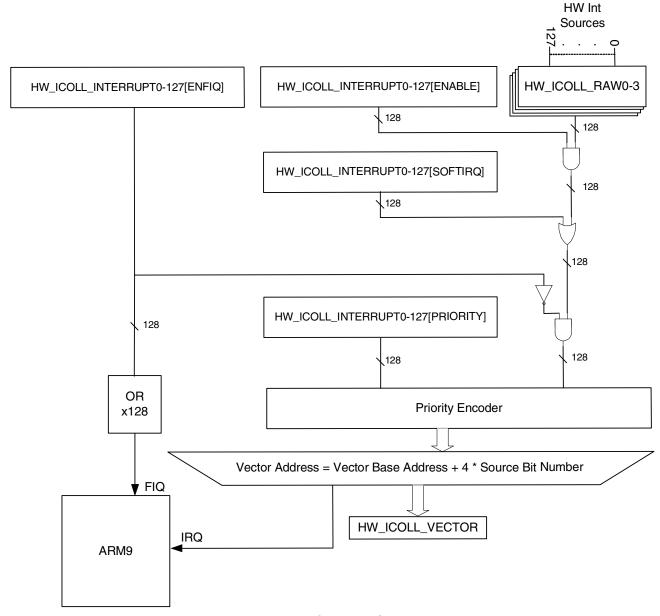

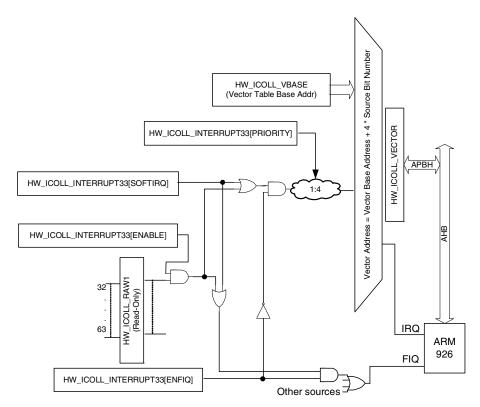

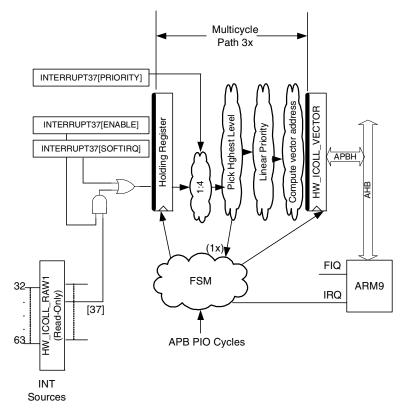

| 5.1                                                                                     | Overview                                                                                                                                                                                                                                                                | 5-1                             |

| 5.2                                                                                     | Operation                                                                                                                                                                                                                                                               |                                 |

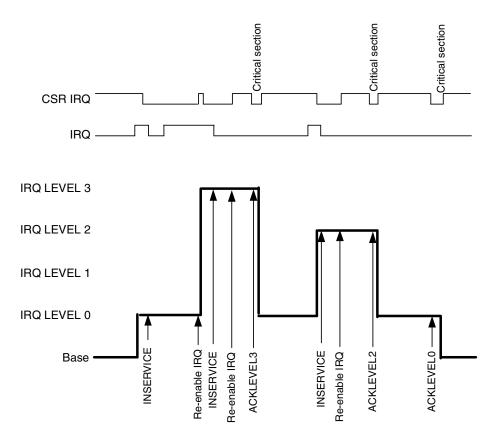

| 5.2.1                                                                                   | Nesting of Multi-Level IRQ Interrupts                                                                                                                                                                                                                                   | 5-4                             |

| 5.2.2                                                                                   | FIQ Generation                                                                                                                                                                                                                                                          |                                 |

| 5.2.3                                                                                   | Interrupt Sources                                                                                                                                                                                                                                                       | 5-6                             |

| 5.2.4                                                                                   | CPU Wait-for-Interrupt Mode                                                                                                                                                                                                                                             |                                 |

| 5.3                                                                                     | Behavior During Reset                                                                                                                                                                                                                                                   | 5-10                            |

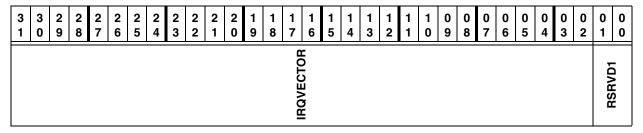

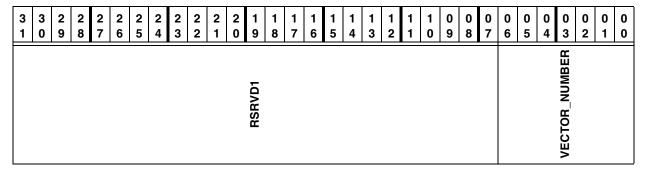

| 5.4                                                                                     | Programmable Registers                                                                                                                                                                                                                                                  |                                 |

|                                                                                         | Chapter 6 Digital Control and On-Chip RAM                                                                                                                                                                                                                               |                                 |

| 6.1                                                                                     | Overview                                                                                                                                                                                                                                                                | 6-1                             |

| 6.2                                                                                     | SRAM Controls                                                                                                                                                                                                                                                           | 6-2                             |

| 0.2                                                                                     |                                                                                                                                                                                                                                                                         |                                 |

| 6.3                                                                                     | Miscellaneous Controls                                                                                                                                                                                                                                                  |                                 |

|                                                                                         |                                                                                                                                                                                                                                                                         | 6-3                             |

| 6.3                                                                                     | Miscellaneous Controls                                                                                                                                                                                                                                                  | 6-3<br>6-3                      |

| 6.3<br>6.3.1                                                                            | Miscellaneous Controls Performance Monitoring                                                                                                                                                                                                                           |                                 |

| 6.3<br>6.3.1<br>6.3.2                                                                   | Miscellaneous Controls Performance Monitoring High-Entropy PRN Seed                                                                                                                                                                                                     | 6-3<br>6-3<br>6-4<br>6-4        |

| 6.3<br>6.3.1<br>6.3.2<br>6.3.3                                                          | Miscellaneous Controls                                                                                                                                                                                                                                                  |                                 |

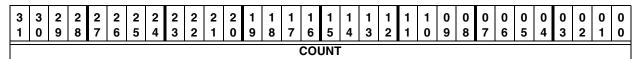

| 6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                                                 | Miscellaneous Controls  Performance Monitoring  High-Entropy PRN Seed  Write-Once Register  Microseconds Counter                                                                                                                                                        |                                 |

| 6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                                                 | Miscellaneous Controls Performance Monitoring High-Entropy PRN Seed Write-Once Register Microseconds Counter Programmable Registers  Chapter 7 On-Chip OTP (OCOTP) Controller                                                                                           | 6-3<br>6-3<br>6-4<br>6-4<br>6-4 |

| 6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.4                                          | Miscellaneous Controls Performance Monitoring High-Entropy PRN Seed Write-Once Register Microseconds Counter Programmable Registers  Chapter 7 On-Chip OTP (OCOTP) Controller  Overview                                                                                 |                                 |

| 6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.4                                          | Miscellaneous Controls.  Performance Monitoring.  High-Entropy PRN Seed.  Write-Once Register  Microseconds Counter.  Programmable Registers  Chapter 7  On-Chip OTP (OCOTP) Controller  Overview.  Operation                                                           |                                 |

| 6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.4                                          | Miscellaneous Controls. Performance Monitoring. High-Entropy PRN Seed. Write-Once Register Microseconds Counter. Programmable Registers  Chapter 7 On-Chip OTP (OCOTP) Controller  Overview. Operation Software Read Sequence                                           |                                 |

| 6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.4<br>7.1<br>7.2<br>7.2.1                   | Miscellaneous Controls.  Performance Monitoring.  High-Entropy PRN Seed.  Write-Once Register  Microseconds Counter.  Programmable Registers  Chapter 7  On-Chip OTP (OCOTP) Controller  Overview.  Operation                                                           |                                 |

| 6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.4<br>7.1<br>7.2<br>7.2.1<br>7.2.2          | Miscellaneous Controls. Performance Monitoring. High-Entropy PRN Seed. Write-Once Register Microseconds Counter. Programmable Registers  Chapter 7 On-Chip OTP (OCOTP) Controller  Overview. Operation Software Read Sequence Software Write Sequence. Write Postamble. |                                 |

| 6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.4<br>7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3 | Miscellaneous Controls. Performance Monitoring. High-Entropy PRN Seed. Write-Once Register Microseconds Counter. Programmable Registers  Chapter 7 On-Chip OTP (OCOTP) Controller  Overview. Operation Software Read Sequence Software Write Sequence                   |                                 |

i.MX23 Applications Processor Reference Manual, Rev. 1

| Paragraph<br>Number | Title                                                    | Page<br>Number |

|---------------------|----------------------------------------------------------|----------------|

|                     | Chapter 8                                                |                |

|                     | USB High-Speed Host/Device Controller                    |                |

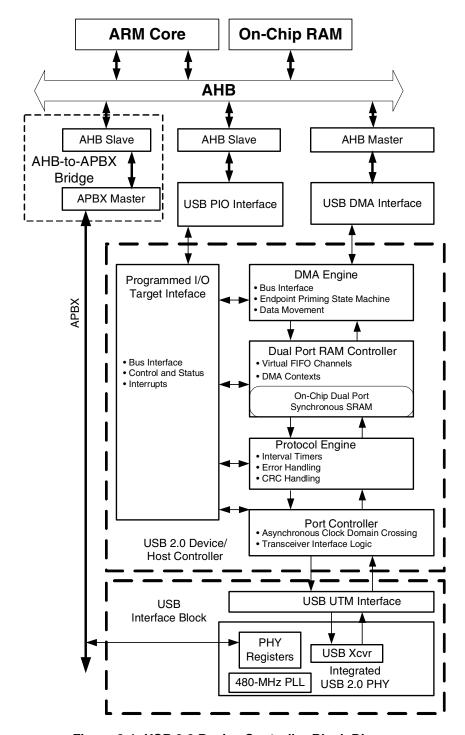

| 8.1                 | Overview                                                 | 8-1            |

| 8.2                 | USB Programmed I/O (PIO) Target Interface                |                |

| 8.3                 | USB DMA Interface                                        |                |

| 8.4                 | USB UTM Interface                                        | 8-3            |

| 8.4.1               | Digital/Analog Loopback Test Mode                        | 8-3            |

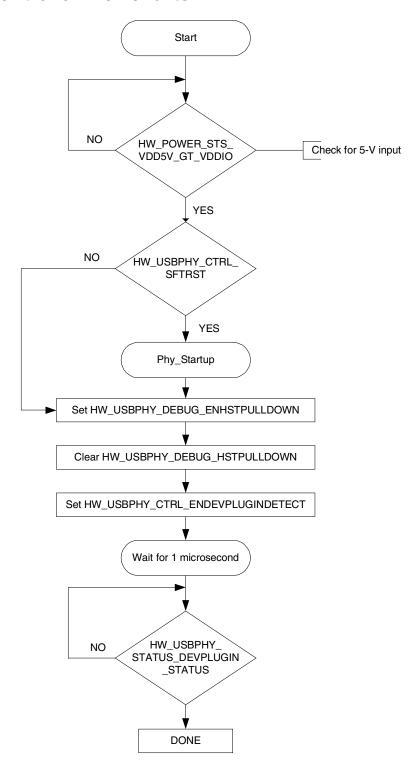

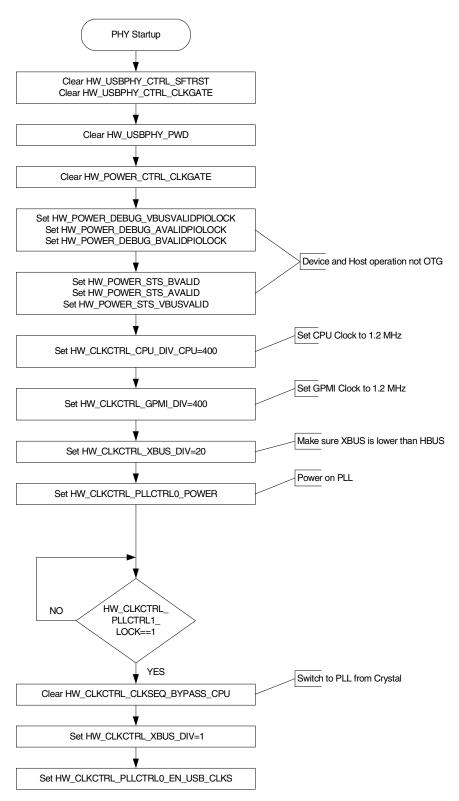

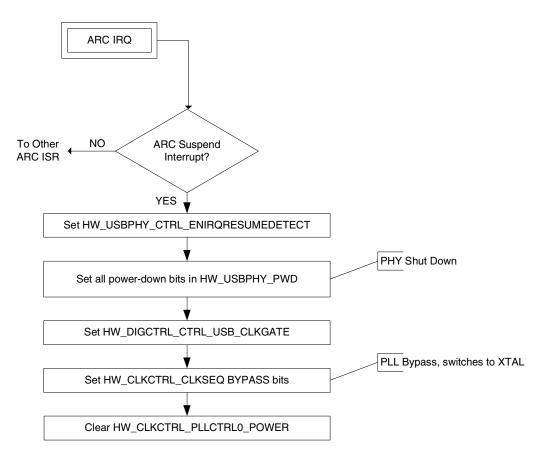

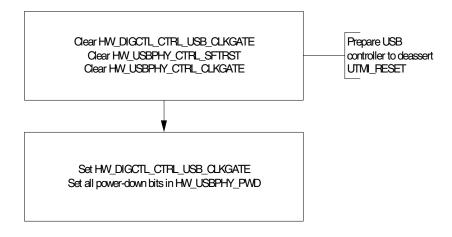

| 8.5                 | USB Controller Flowcharts                                | 8-4            |

| 8.5.1               | References                                               | 8-7            |

| 8.6                 | Programmable Registers                                   | 8-7            |

|                     | Chapter 9                                                |                |

|                     | Integrated USB 2.0 PHY                                   |                |

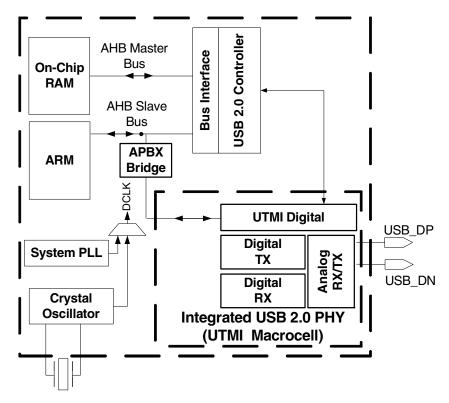

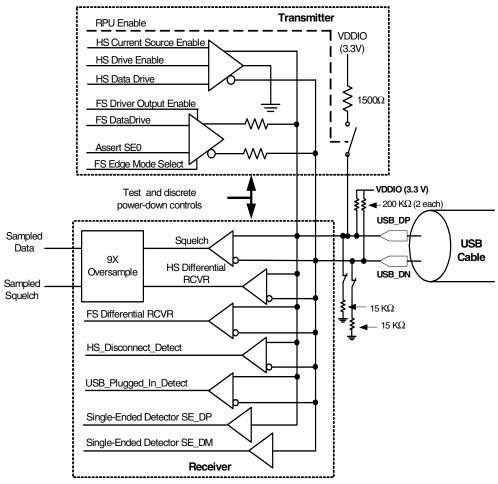

| 9.1                 | Overview                                                 | 9-1            |

| 9.2                 | Operation                                                | 9-2            |

| 9.2.1               | UTMI                                                     | 9-2            |

| 9.2.2               | Digital Transmitter                                      | 9-2            |

| 9.2.3               | Digital Receiver                                         | 9-2            |

| 9.2.4               | Analog Receiver                                          | 9-2            |

| 9.2.4.1             | HS Differential Receiver                                 | 9-3            |

| 9.2.4.2             | Squelch Detector                                         | 9-3            |

| 9.2.4.3             | FS Differential Receiver                                 | 9-4            |

| 9.2.4.4             | HS Disconnect Detector                                   | 9-4            |

| 9.2.4.5             | USB Plugged-In Detector                                  | 9-4            |

| 9.2.4.6             | Single-Ended USB_DP Receiver                             | 9-4            |

| 9.2.4.7             | Single-Ended USB_DN Receiver                             | 9-4            |

| 9.2.4.8             | 9X Oversample Module                                     | 9-4            |

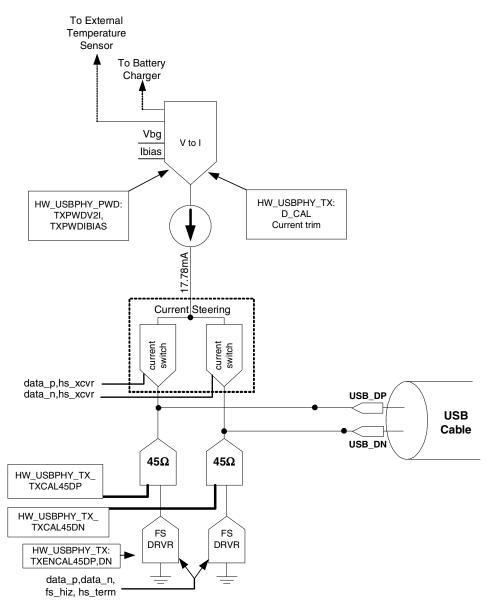

| 9.2.5               | Analog Transmitter                                       | 9-4            |

| 9.2.5.1             | Switchable High-Speed 45Ω Termination Resistors          |                |

| 9.2.5.2             | Full-Speed Differential Driver                           | 9-5            |

| 9.2.5.3             | High-Speed Differential Driver                           | 9-5            |

| 9.2.5.4             | Switchable 1.5KΩ USB_DP Pullup Resistor                  |                |

| 9.2.5.5             | Switchable 15KΩ USB_DP Pulldown Resistor                 |                |

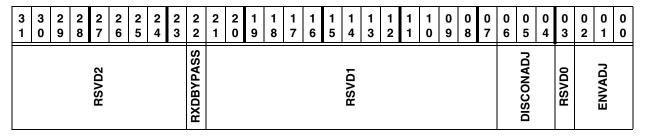

| 9.2.6               | Recommended Register Configuration for USB Certification |                |

| 9.3                 | Behavior During Reset                                    |                |

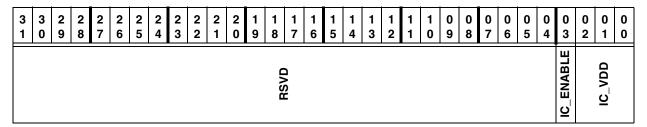

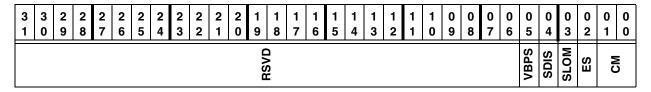

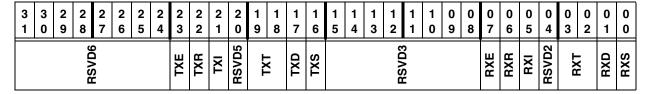

| 9.4                 | Programmable Registers                                   |                |

| Paragraph<br>Number | Title                                                  | Page<br>Number |

|---------------------|--------------------------------------------------------|----------------|

|                     | Chapter 10                                             |                |

|                     | AHB-to-APBH Bridge with DMA                            |                |

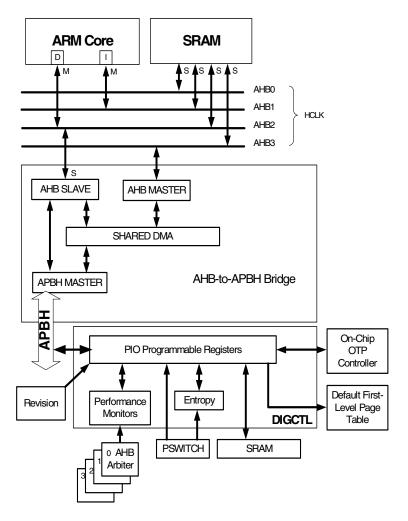

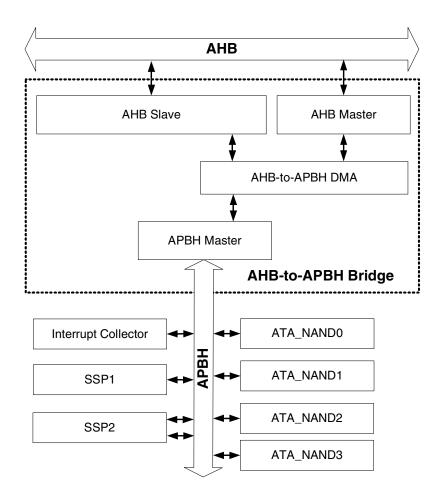

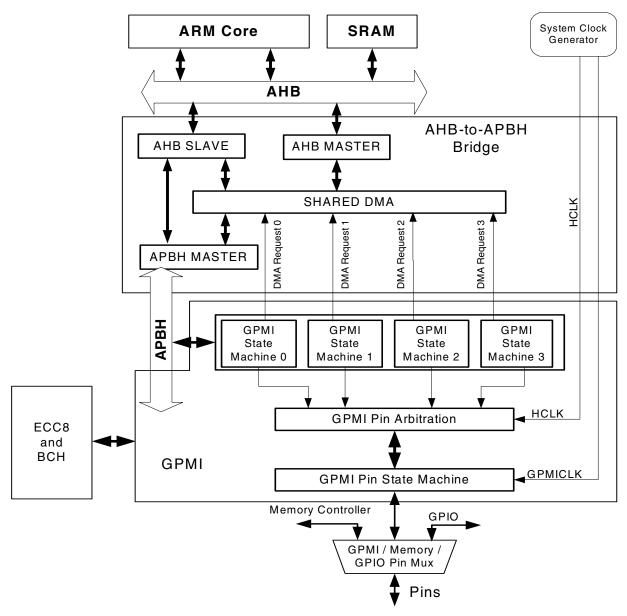

| 10.1                | Overview                                               | 10-1           |

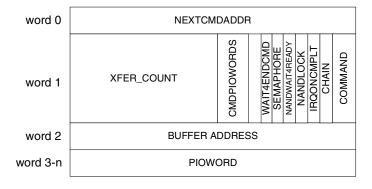

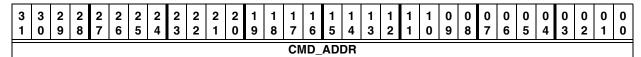

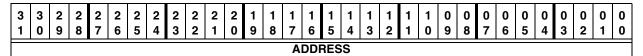

| 10.2                | AHBH DMA                                               | 10-2           |

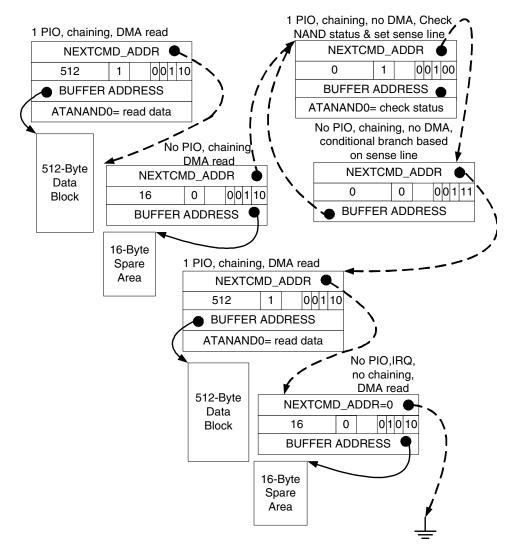

| 10.3                | Implementation Examples                                | 10-7           |

| 10.3.1              | NAND Read Status Polling Example                       | 10-7           |

| 10.4                | Behavior During Reset                                  | 10-9           |

| 10.5                | Programmable Registers                                 | 10-9           |

|                     | Chapter 11                                             |                |

|                     | AHB-to-APBX Bridge with DMA                            |                |

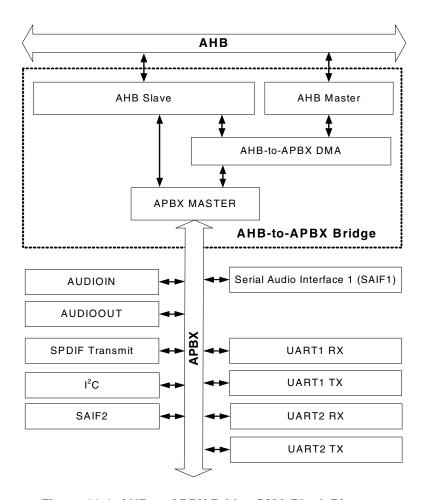

| 11.1                | Overview                                               | 11-1           |

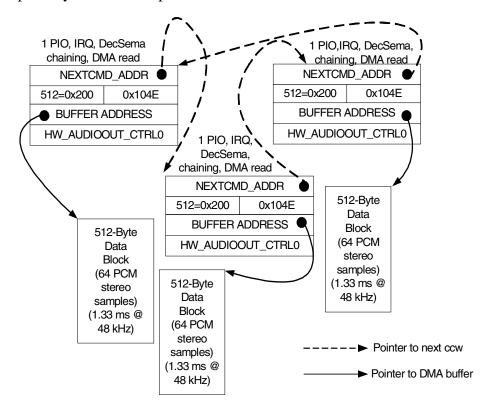

| 11.2                | APBX DMA                                               | 11-2           |

| 11.3                | DMA Chain Example                                      |                |

| 11.4                | Behavior During Reset                                  |                |

| 11.5                | Programmable Registers                                 | 11-8           |

|                     | Chapter 12                                             |                |

|                     | External Memory Interface (EMI)                        |                |

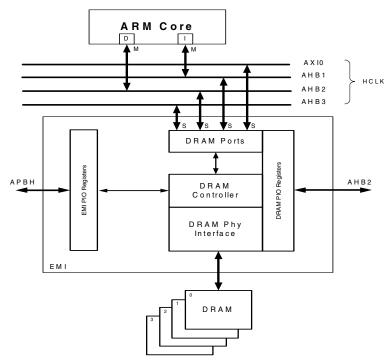

| 12.1                | Overview                                               | 12-1           |

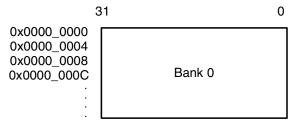

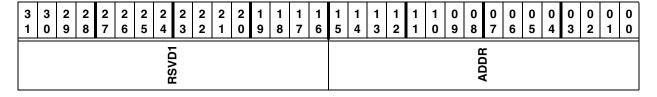

| 12.1.1              | AHB Address Ranges                                     | 12-2           |

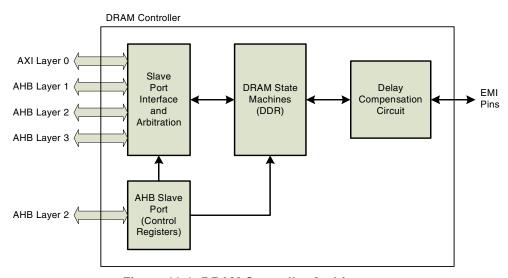

| 12.2                | DRAM Controller                                        | 12-3           |

| 12.2.1              | Delay Compensation Circuit (DCC)                       | 12-3           |

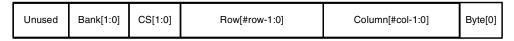

| 12.2.2              | Address Mapping                                        | 12-3           |

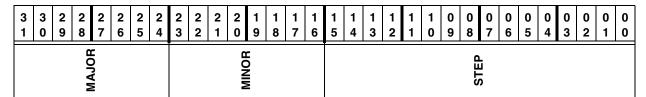

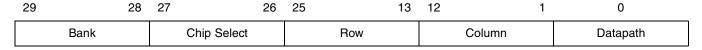

| 12.2.2.1            | DDR Address Mapping Options                            | 12-4           |

| 12.2.2.2            | Memory Controller Address Control                      | 12-5           |

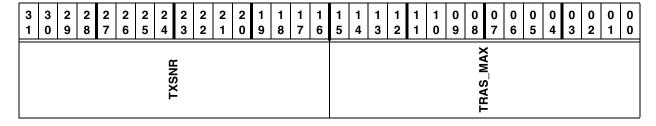

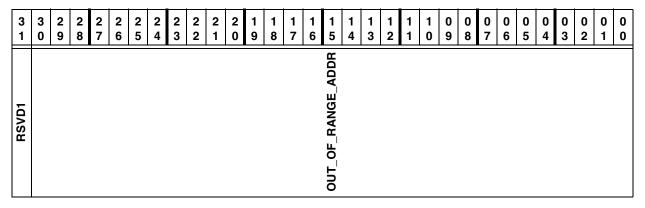

| 12.2.2.3            | Out-of-Range Address Checking                          |                |

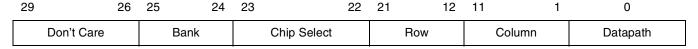

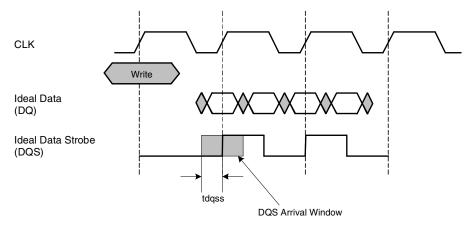

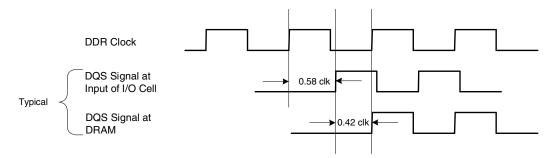

| 12.2.3              | Read Data Capture                                      |                |

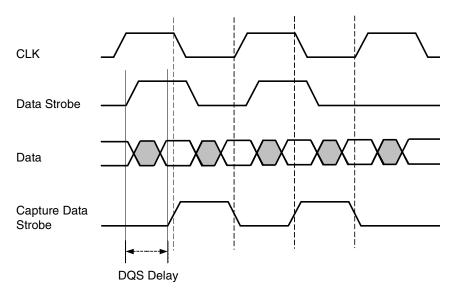

| 12.2.3.1            | DQS Gating Control                                     |                |

| 12.2.3.2            | mDDR Read Data Timing Registers                        |                |

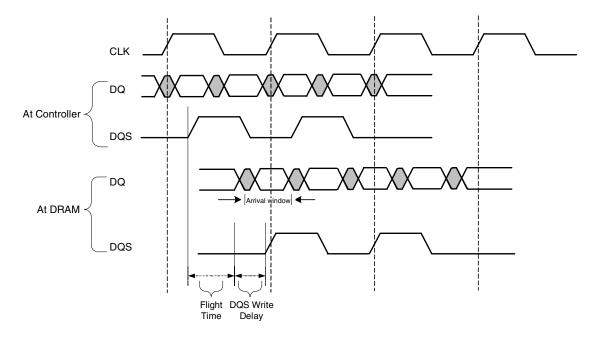

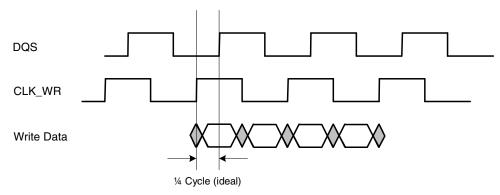

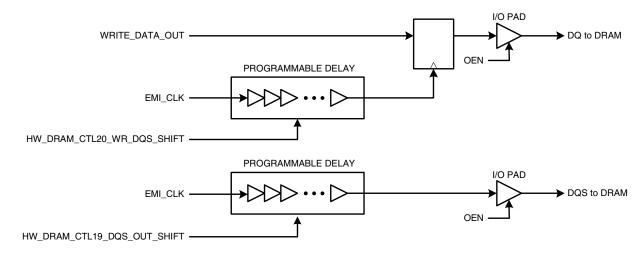

| 12.2.4              | Write Data Timing                                      | 12-9           |

| 12.2.5              | DRAM Clock Programmable Delay                          |                |

| 12.2.6              | Low-Power Operation                                    |                |

| 12.2.6.1            | Low-Power Modes                                        |                |

| 12.2.6.2            | Low-Power Mode Control                                 |                |

| 12.2.6.3            | Automatic Entry                                        |                |

| 12.2.6.4            | Manual "On-Demand" Entry                               |                |

| 12.2.6.5            | Register Programming                                   |                |

|                     | i.MX23 Applications Processor Reference Manual, Rev. 1 | 1              |

| Paragraph |                                                     | Page   |

|-----------|-----------------------------------------------------|--------|

| Number    | Title                                               | Number |

| 12.2.6.6  | Refresh Masking                                     |        |

| 12.2.6.7  | Mobile DDR Devices                                  |        |

| 12.2.6.8  | Partial Array Self-Refresh                          |        |

| 12.2.7    | EMI Clock Frequency Change Requirements             | 12-17  |

| 12.3      | Power Management                                    |        |

| 12.4      | AXI/AHB Port Arbitration                            |        |

| 12.4.1    | Legacy Timestamp Mode                               |        |

| 12.4.2    | Timestamp/write-priority Hybrid Mode                |        |

| 12.4.3    | Port Priority Mode                                  |        |

| 12.5      | Programmable Registers                              | 12-20  |

| 12.6      | EMI Memory Parameters and Register Settings         | 12-68  |

| 12.6.1    | Mobile DDR (5 nsec) Parameters                      | 12-68  |

| 12.6.1.1  | Bypass Cutoff                                       | 12-68  |

| 12.6.1.2  | Bypass Mode Enabled                                 | 12-68  |

| 12.6.1.3  | Bypass Mode Disabled                                |        |

| 12.6.1.4  | Example Register Settings                           | 12-69  |

| 12.6.2    | Mobile DDR (6 nsec)                                 |        |

| 12.6.2.1  | Bypass Cutoff                                       |        |

| 12.6.2.2  | Bypass Mode Enabled                                 |        |

| 12.6.2.3  | Bypass Mode Disabled                                |        |

| 12.6.2.4  | Example Register Settings                           |        |

| 12.6.3    | Mobile DDR (7.5 nsec)                               |        |

| 12.6.3.1  | Bypass Cutoff                                       |        |

| 12.6.3.2  | Bypass Mode Enabled                                 |        |

| 12.6.3.3  | Bypass Mode Disabled                                |        |

| 12.6.3.4  | Example Register Settings                           |        |

| 12.6.4    | DDR                                                 | 12-76  |

| 12.6.4.1  | Bypass Mode Disabled                                | 12-76  |

| 12.6.4.2  | Example Register Settings                           |        |

|           | Chapter 13 General-Purpose Media Interface (GPMI)   |        |

|           |                                                     |        |

| 13.1      | Overview                                            |        |

| 13.2      | GPMI NAND Flash Mode                                |        |

| 13.2.1    | Multiple NAND Flash Support                         |        |

| 13.2.2    | GPMI NAND Flash Timing and Clocking                 |        |

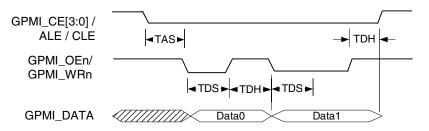

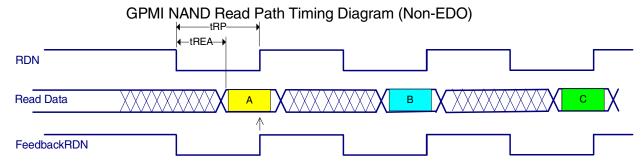

| 13.2.3    | Basic NAND Flash Timing                             |        |

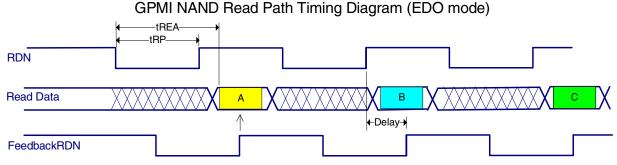

| 13.2.4    | High-Speed NAND Flash Timing                        |        |

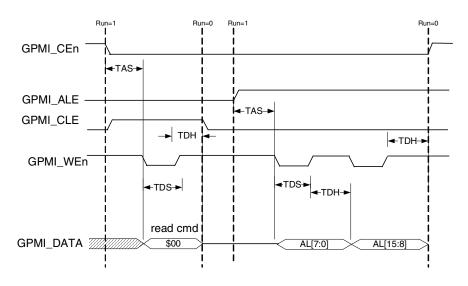

| 13.2.5    | NAND Flash Command and Address Timing Example       |        |

| 13.2.6    | Hardware BCH/ECC (ECC8) Interface                   |        |

|           | : MVOO Applications Duscossey Defenses Manual Day 1 |        |

| Paragraph<br>Number | Title                                                                     | Page<br>Number |

|---------------------|---------------------------------------------------------------------------|----------------|

| 13.3                | Behavior During Reset                                                     | 13-8           |

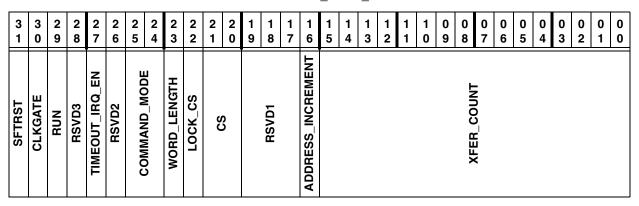

| 13.4                | Programmable Registers                                                    | 13-9           |

|                     | Chapter 14 8-Symbol Correcting ECC Accelerator (ECC8)                     |                |

| 14.1                | Overview                                                                  | 14-1           |

| 14.2                | Operation                                                                 | 14-4           |

| 14.2.1              | Reed-Solomon ECC Accelerator                                              | 14-8           |

| 14.2.2              | Reed-Solomon ECC Encoding for NAND Writes                                 | 14-11          |

| 14.2.2.1            | DMA Structure Code Example                                                | 14-15          |

| 14.2.2.2            | Using the ECC8 Encoder                                                    | 14-18          |

| 14.2.3              | Reed-Solomon ECC Decoding for NAND Reads                                  | 14-19          |

| 14.2.3.1            | DMA Structure Code Example                                                | 14-23          |

| 14.2.3.2            | Using the Decoder                                                         | 14-25          |

| 14.2.4              | Interrupts                                                                | 14-27          |

| 14.3                | Behavior During Reset                                                     | 14-28          |

| 14.4                | Programmable Registers                                                    | 14-28          |

|                     | Chapter 15                                                                |                |

|                     | 20-BIT Correcting ECC Accelerator (BCH)                                   |                |

| 15.1                | Overview                                                                  | 15-1           |

| 15.2                | Operation                                                                 | 15-3           |

| 15.2.1              | BCH Limitations and Assumptions                                           | 15-4           |

| 15.2.2              | Flash Page Layout                                                         | 15-4           |

| 15.2.3              | Determining the ECC layout for a device                                   | 15-6           |

| 15.2.3.1            | 4K+218 flash, 10 bytes metadata, 512 byte data blocks, separate metadata. | 15-6           |

| 15.2.3.2            | 4K+128 flash, 10 bytes metadata, 512 byte data blocks, separate metadata. | 15-6           |

| 15.2.4              | Data buffers in system memory                                             | 15-7           |

| 15.3                | Memory to Memory (Loopback) Operation                                     | 15-9           |

| 15.4                | Programming the BCH/GPMI Interfaces                                       | 15-10          |

| 15.4.1              | BCH Encoding for NAND Writes                                              | 15-10          |

| 15.4.1.1            | DMA Structure Code Example                                                | 15-13          |

| 15.4.1.2            | Using the BCH Encoder                                                     | 15-16          |

| 15.4.2              | BCH Decoding for NAND Reads                                               | 15-17          |

| 15.4.2.1            | DMA Structure Code Example                                                | 15-20          |

| 15.4.2.2            | Using the Decoder                                                         | 15-23          |

| 15.4.3              | Interrupts                                                                | 15-25          |

| 15.5                | Behavior During Reset                                                     | 15-26          |

| 15.6                | Programmable Registers                                                    | 15-26          |

|                     |                                                                           |                |

i.MX23 Applications Processor Reference Manual, Rev. 1

| Paragraph<br>Number | Title                                                  | Page<br>Number |

|---------------------|--------------------------------------------------------|----------------|

|                     | Chapter 16                                             |                |

|                     | Data Co-Processor (DCP)                                |                |

| 16.1                | Overview                                               | 16-1           |

| 16.1.1              | DCP Limitations for Software                           | 16-3           |

| 16.2                | Operation                                              | 16-4           |

| 16.2.1              | Memory Copy, Blit, and Fill Functionality              | 16-4           |

| 16.2.2              | Advanced Encryption Standard (AES)                     | 16-5           |

| 16.2.2.1            | Key Storage                                            | 16-5           |

| 16.2.2.2            | OTP Key                                                | 16-5           |

| 16.2.2.3            | Encryption Modes                                       | 16-5           |

| 16.2.3              | Hashing                                                |                |

| 16.2.4              | Managing DCP Channel Arbitration and Performance       | 16-7           |

| 16.2.4.1            | DCP Arbitration                                        | 16-8           |

| 16.2.4.2            | Channel Recovery Timers                                | 16-8           |

| 16.2.5              | Programming Channel Operations                         | 16-9           |

| 16.2.5.1            | Virtual Channels                                       | 16-9           |

| 16.2.5.2            | Context Switching                                      | 16-10          |

| 16.2.5.3            | Working with Semaphores                                | 16-11          |

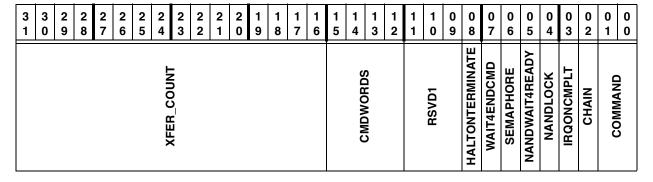

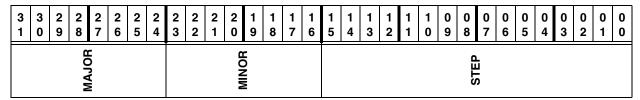

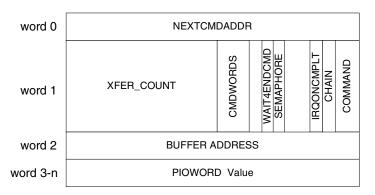

| 16.2.5.4            | Work Packet Structure                                  | 16-11          |

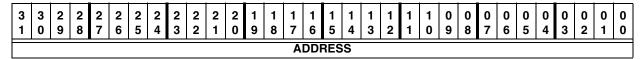

| 16.2.5.4.1          | Next Command Address Field                             | 16-12          |

| 16.2.5.4.2          | Control0 Field                                         | 16-12          |

| 16.2.5.4.3          | Control1 Field                                         | 16-14          |

| 16.2.5.4.4          | Source Buffer                                          | 16-15          |

| 16.2.5.4.5          | Destination Buffer                                     | 16-15          |

| 16.2.5.4.6          | Buffer Size Field                                      | 16-15          |

| 16.2.5.4.7          | Payload Pointer                                        | 16-16          |

| 16.2.5.4.8          | Status                                                 | 16-16          |

| 16.2.5.4.9          | Payload                                                | 16-17          |

| 16.2.6              | Programming Other DCP Functions                        | 16-17          |

| 16.2.6.1            | Basic Memory Copy Programming Example                  | 16-17          |

| 16.2.6.2            | Basic Hash Operation Programming Example               | 16-18          |

| 16.2.6.3            | Basic Cipher Operation Programming Example             | 16-20          |

| 16.2.6.4            | Multi-Buffer Scatter/Gather Cipher and Hash            |                |

|                     | Operation Programming Example                          | 16-21          |

| 16.3                | Programmable Registers                                 |                |

|                     | Chapter 17                                             |                |

|                     | Pixel Pipeline (PXP)                                   |                |

| 17.1                | Overview                                               | 17-1           |

|                     | i.MX23 Applications Processor Reference Manual, Rev. 1 |                |

viii

| Paragraph  |                                                 | Page   |

|------------|-------------------------------------------------|--------|

| Number     | Title                                           | Number |

| 17.1.1     | Image Support                                   | 17-2   |

| 17.1.2     | PXP Limitations/Issues                          | 17-3   |

| 17.2       | Operation                                       | 17-3   |

| 17.2.1     | Pixel Handling                                  | 17-4   |

| 17.2.2     | S0 Cropping/Masking                             | 17-5   |

| 17.2.3     | Scaling                                         | 17-7   |

| 17.2.3.1   | Scaling Operation                               | 17-8   |

| 17.2.3.1.1 | Bilinear Image Scaling Filter                   | 17-9   |

| 17.2.3.1.2 | YUV 4:2:2 Image Scaling                         | 17-10  |

| 17.2.3.1.3 | YUV 4:2:0 Image Scaling                         | 17-11  |

| 17.2.3.1.4 | Out-of-Range Image Access                       | 17-12  |

| 17.2.4     | Colorspace Conversion                           | 17-13  |

| 17.2.5     | Overlays                                        | 17-14  |

| 17.2.6     | Alpha Blending                                  | 17-16  |

| 17.2.7     | Color Key                                       | 17-16  |

| 17.2.8     | Raster Operations (ROPs)                        | 17-17  |

| 17.2.9     | Rotation                                        | 17-18  |

| 17.2.10    | In-place Rendering                              | 17-20  |

| 17.2.11    | Interlaced Video Support                        | 17-21  |

| 17.2.12    | Queueing Frame Operations                       | 17-21  |

| 17.3       | Examples                                        | 17-22  |

| 17.3.1     | Basic QVGA Example                              | 17-22  |

| 17.3.2     | Basic QVGA with Overlays                        | 17-24  |

| 17.3.3     | Cropped QVGA Example                            | 17-25  |

| 17.3.4     | Upscale QVGA to VGA with Overlays               | 17-27  |

| 17.3.5     | Downscale VGA to WQVGA (480x272) to fill screen | 17-29  |

| 17.3.6     | Downscale VGA to QVGA with Overlapping Overlays | 17-31  |

| 17.4       | Programmable Registers                          | 17-33  |

|            | Chapter 18<br>LCD Interface (LCDIF)             |        |

| 10.1       | ,                                               | 10 1   |

| 18.1       | Overview                                        |        |

| 18.2       | Operation                                       |        |

| 18.2.1     | Bus Interface Mechanisms                        |        |

| 18.2.1.1   | PIO Operation                                   |        |

| 18.2.1.2   | Bus Master Operation                            |        |

| 18.2.2     | Write Datapath                                  |        |

| 18.2.3     | LCDIF Interrupts                                |        |

| 18.2.4     | Initializing the LCDIF                          |        |

| 18.2.5     | System Interface                                | 18-12  |

| Paragraph<br>Number | Title                                           | Page<br>Number |

|---------------------|-------------------------------------------------|----------------|

| 18.2.5.1            | Code Example to initialize LCDIF in System mode |                |

| 18.2.6              | VSYNC Interface                                 |                |

| 18.2.6.1            | Code Example to initialize LCDIF in VSYNC mode  |                |

| 18.2.7              | DOTCLK Interface                                |                |

| 18.2.7.1            | Code Example                                    |                |

| 18.2.8              | ITU-R BT.656 Digital Video Interface (DVI)      |                |

| 18.2.9              | LCDIF Pin Usage by Interface Mode               |                |

| 18.3                | Behavior During Reset                           |                |

| 18.4                | Programmable Registers                          |                |

|                     | Chapter 19                                      |                |

|                     | TV-Out NTSC/PAL Encoder                         |                |

| 19.1                | Implementation                                  |                |

| 19.2                | Unsupported DVE features                        |                |

| 19.3                | Programming Example                             |                |

| 19.4                | Programmable Registers                          | 19-4           |

|                     | Chapter 20<br>Video DAC                         |                |

| 20.1                | Overview                                        | 20-1           |

| 20.2                | Details of Operations                           | 20-1           |

|                     | Chapter 21<br>Synchronous Serial Ports (SSP)    |                |

| 21.1                | Overview                                        | 21-1           |

| 21.2                | External Pins                                   |                |

| 21.3                | Bit Rate Generation                             |                |

| 21.4                | Frame Format for SPI and SSI                    |                |

| 21.5                | Motorola SPI Mode                               |                |

| 21.5.1              | SPI DMA Mode                                    |                |

| 21.5.2              | Motorola SPI Frame Format                       |                |

| 21.5.2.1            | Clock Polarity                                  |                |

| 21.5.2.2            | Clock Phase                                     |                |

| 21.5.3              | Motorola SPI Format with Polarity=0, Phase=0    |                |

| 21.5.4              | Motorola SPI Format with Polarity=0, Phase=1    |                |

| 21.5.5              | Motorola SPI Format with Polarity=1, Phase=0    |                |

| 21.5.6              | Motorola SPI Format with Polarity=1, Phase=1    |                |

| 21.6                | Winbond SPI Mode                                |                |

|                     |                                                 |                |

| Paragraph<br>Number | Title                                                           | Page<br>Number |

|---------------------|-----------------------------------------------------------------|----------------|

| 21.7                | Texas Instruments Synchronous Serial Interface (SSI) Mode       | 21-9           |

| 21.8                | SD/SDIO/MMC Mode                                                | 21-10          |

| 21.8.1              | SD/MMC Command/Response Transfer                                | 21-11          |

| 21.8.2              | SD/MMC Data Block Transfer                                      | 21-12          |

| 21.8.2.1            | SD/MMC Multiple Block Transfers                                 | 21-13          |

| 21.8.2.2            | SD/MMC Block Transfer CRC Protection                            | 21-14          |

| 21.8.3              | SDIO Interrupts                                                 | 21-14          |

| 21.8.4              | SD/MMC Mode Error Handling                                      | 21-14          |

| 21.8.5              | SD/MMC Clock Control                                            | 21-17          |

| 21.9                | Behavior During Reset                                           | 21-18          |

| 21.10               | Programmable Registers                                          | 21-18          |

|                     | Chapter 22 Timers and Rotary Decoder                            |                |

| 22.1                | Overview                                                        | 22-1           |

| 22.2                | Timers                                                          | 22-2           |

| 22.2.1              | Using External Signals as Inputs                                | 22-4           |

| 22.2.2              | Timer 3 and Duty Cycle Mode                                     | 22-4           |

| 22.2.3              | Testing Timer 3 Duty Cycle Modes                                | 22-6           |

| 22.3                | Rotary Decoder                                                  | 22-6           |

| 22.3.1              | Testing the Rotary Decoder                                      | 22-9           |

| 22.3.2              | Behavior During Reset                                           | 22-9           |

| 22.4                | Programmable Registers                                          | 22-9           |

|                     | Chapter 23<br>Real-Time Clock, Alarm, Watchdog, Persistent Bits |                |

| 23.1                | Overview                                                        | 23-1           |

| 23.2                | Programming and Enabling the RTC Clock                          | 23-4           |

| 23.3                | RTC Persistent Register Copy Control                            |                |

| 23.4                | Real-Time Clock Function                                        | 23-6           |

| 23.4.1              | Behavior During Reset                                           | 23-7           |

| 23.5                | Millisecond Resolution Timing Function                          |                |

| 23.6                | Alarm Clock Function                                            |                |

| 23.7                | Watchdog Reset Function                                         | 23-8           |

| 23.8                | Programmable Registers                                          | 23-8           |

|                     |                                                                 |                |

| Paragraph | <b>T</b> '11.                                     | Page   |

|-----------|---------------------------------------------------|--------|

| Number    | Title                                             | Number |

|           | Chapter 24 Pulse-Width Modulator (PWM) Controller |        |

| 24.1      | Overview                                          | 24-1   |

| 24.2      | Operation                                         | 24-1   |

| 24.2.1    | Multi-Chip Attachment Mode                        | 24-4   |

| 24.2.2    | Channel 2 Analog Enable Function                  | 24-5   |

| 24.2.3    | Channel Output Cutoff Using Module Clock Gate     | 24-5   |

| 24.3      | Behavior During Reset                             |        |

| 24.4      | Programmable Registers                            | 24-6   |

|           | Chapter 25<br>I <sup>2</sup> C Interface          |        |

| 25.1      | Overview                                          | 25-1   |

| 25.2      | Operation                                         |        |

| 25.2.1    | I <sup>2</sup> C Interrupt Sources                |        |

| 25.2.2    | I <sup>2</sup> C Bus Protocol                     |        |

| 25.2.2.1  | Simple Device Transactions                        |        |

| 25.2.2.2  | Typical EEPROM Transactions                       |        |

| 25.2.2.3  | Master Mode Protocol                              |        |

| 25.2.2.4  | Clock Generation                                  |        |

| 25.2.2.5  | Master Mode Operation                             |        |

| 25.2.3    | Programming Examples                              |        |

| 25.2.3.1  | Five Byte Master Write Using DMA                  |        |

| 25.2.3.2  | Reading 256 Bytes from an EEPROM                  |        |

| 25.3      | Behavior During Reset                             |        |

| 25.3.1    | Pinmux Selection During Reset                     |        |

| 25.3.1.1  | Correct and Incorrect Reset Examples              |        |

| 25.4      | Programmable Registers                            |        |

|           | Chapter 26                                        |        |

|           | Application UART                                  |        |

| 26.1      | Overview                                          |        |

| 26.2      | Operation                                         |        |

| 26.2.1    | Fractional Baud Rate Divider                      |        |

| 26.2.2    | UART Character Frame                              |        |

| 26.2.3    | DMA Operation                                     |        |

| 26.2.4    | Data Transmission or Reception                    |        |

| 26.2.5    | Error Bits                                        | 26-4   |

|           |                                                   |        |

|                                                  | Page                                   |

|--------------------------------------------------|----------------------------------------|

| Title                                            | Number                                 |

| Overrun Bit                                      | 26-4                                   |

| Disabling the FIFOs                              | 26-5                                   |

| Behavior During Reset                            | 26-5                                   |

| Programmable Registers                           | 26-5                                   |

| Chapter 27 Debug UART                            |                                        |

| Overview                                         | 27-1                                   |

| Operation                                        | 27-2                                   |

| Fractional Baud Rate Divider                     |                                        |

| UART Character Frame                             | 27-3                                   |

| Data Transmission or Reception                   | 27-3                                   |

| Error Bits                                       |                                        |

| Overrun Bit                                      | 27-4                                   |

|                                                  |                                        |

| Programmable Registers                           |                                        |

| Chapter 28<br>AUDIOIN/ADC                        |                                        |

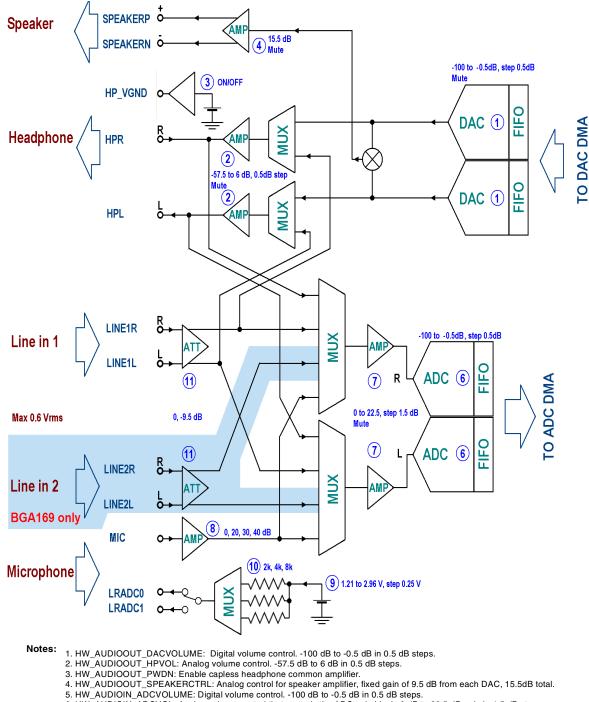

| Overview                                         | 28-1                                   |

| Operation                                        | 28-2                                   |

| AUDIOIN DMA                                      |                                        |

| ADC Sample Rate Converter and Internal Operation | 28-5                                   |

| Line-In                                          | 28-8                                   |

| Microphone                                       | 28-8                                   |

| Behavior During Reset                            | 28-9                                   |

| Programmable Registers                           | 28-9                                   |

| Chapter 29<br>AUDIOOUT/DAC                       |                                        |

| Overview                                         | 29-1                                   |

|                                                  |                                        |

| <u>-</u>                                         |                                        |

|                                                  |                                        |

|                                                  |                                        |

| <u> </u>                                         |                                        |

| Board Components                                 |                                        |

|                                                  | ······································ |

|                                                  | Overrun Bit                            |

i.MX23 Applications Processor Reference Manual, Rev. 1

| Paragraph<br>Number | Title                                                     | Page<br>Number |

|---------------------|-----------------------------------------------------------|----------------|

| 29.2.5              | Speaker Amplifier                                         | 29-11          |

| 29.2.5.1            | Overview                                                  |                |

| 29.2.5.2            | Details of Operations                                     |                |

| 29.3                | Behavior During Reset                                     |                |

| 29.4                | Programmable Registers                                    |                |

|                     | Chapter 30<br>SPDIF Transmitter                           |                |

| 30.1                | Overview                                                  | 30-1           |

| 30.2                | Operation                                                 | 30-1           |

| 30.2.1              | Interrupts                                                | 30-4           |

| 30.2.2              | Clocking                                                  |                |

| 30.2.3              | DMA Operation                                             |                |

| 30.2.4              | PIO Debug Mode                                            |                |

| 30.3                | Programmable Registers                                    |                |

|                     | Chapter 31<br>Serial Audio Interface (SAIF) (BGA169 Only) |                |

| 31.1                | Overview                                                  | 31-1           |

| 31.2                | Operation                                                 | 31-2           |

| 31.2.1              | Sample Rate Programming and Codec Clocking Operation      | 31-3           |

| 31.2.2              | Transmit Operation                                        | 31-6           |

| 31.2.3              | Receive Operation                                         | 31-7           |

| 31.2.4              | DMA Interface                                             | 31-8           |

| 31.2.5              | PCM Data FIFO                                             | 31-8           |

| 31.2.6              | Serial Frame Formats                                      | 31-9           |

| 31.2.7              | Pin Timing                                                | 31-10          |

| 31.3                | Programmable Registers                                    | 31-10          |

|                     | Chapter 32<br>Power Supply                                |                |

| 32.1                | Overview                                                  | 32-1           |

| 32.2                | DC-DC Converters                                          |                |

| 32.2.1              | DC-DC Operation                                           |                |

| 32.2.1.1            | Brownout/Error Detection                                  |                |

| 32.2.1.2            | DC-DC Extended Battery Life Features                      |                |

| 32.3                | Linear Regulators                                         |                |

| 32.3.1              | USB Compliance Features                                   |                |

|                     |                                                           |                |

| Paragraph<br>Number | Title                                         | Page<br>Number |

|---------------------|-----------------------------------------------|----------------|

|                     |                                               |                |

| 32.3.2              | 5V to Battery Power Interaction               |                |

| 32.3.2.1            | Battery Power to 5-V Power                    |                |

| 32.3.2.2            | 5-V Power to Battery Power                    |                |

| 32.3.2.3            | 5-V Power and Battery Power                   |                |

| 32.3.3              | Power-Up Sequence                             |                |

| 32.3.4              | Power-Down Sequence                           |                |

| 32.3.4.1            | Powered-Down State                            |                |

| 32.3.5              | Reset Sequence                                |                |

| 32.4                | PSWITCH Pin Functions                         |                |

| 32.4.1              | Power On                                      | 32-10          |

| 32.4.2              | Power Down                                    | 32-10          |

| 32.4.3              | Software Functions/Recovery Mode              | 32-10          |

| 32.5                | Battery Monitor                               |                |

| 32.6                | Battery Charger                               | 32-12          |

| 32.7                | Silicon Speed Sensor                          | 32-13          |

| 32.8                | Interrupts                                    | 32-14          |

| 32.9                | Proper Power Supply Protection                | 32-14          |

| 32.9.1              | Power Supply Protection Goal                  | 32-14          |

| 32.9.2              | Power Supply Input Voltage Protection         | 32-15          |

| 32.9.3              | PWDN_BATTBRNOUT and PWDN_5VBRNOUT Details     | 32-15          |

| 32.9.4              | VDD5V Input Protection                        |                |

| 32.9.5              | DCDC Input Protection                         |                |

| 32.9.6              | DCDC Output Protection                        |                |

| 32.9.7              | PWD_OFF Bit Usage                             |                |

| 32.9.8              | Power Supply Protection Summary               |                |

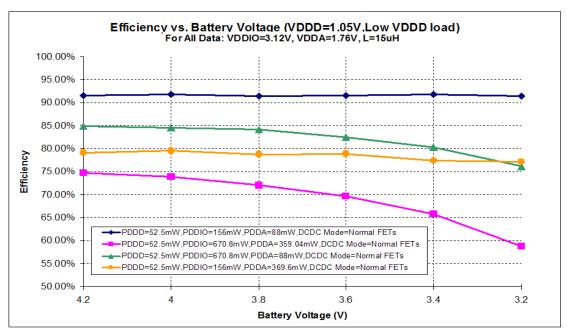

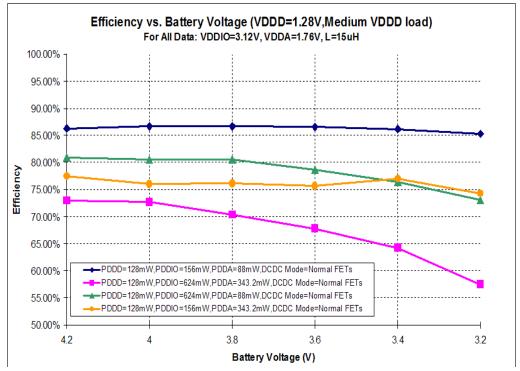

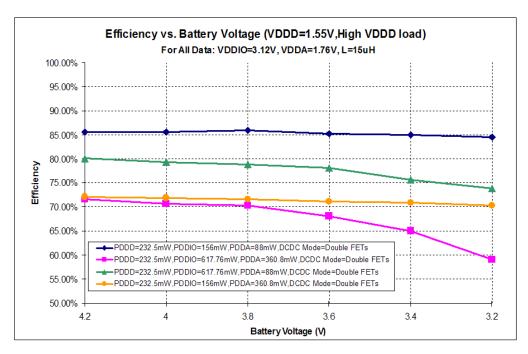

| 32.10               | DC-DC Converter Efficiency                    |                |

| 32.11               | Programmable Registers                        |                |

|                     | Chapter 33                                    |                |

|                     | Low-Resolution ADC and Touch-Screen Interface |                |

| 33.1                | Overview                                      | 33-1           |

| 33.2                | Operation                                     |                |

| 33.2.1              | External Temperature Sensing with a Diode     |                |

| 33.2.2              | Internal Die Temperature Sensing              |                |

| 33.2.3              | Scheduling Conversions                        |                |

| 33.2.4              | Delay Channels                                |                |

| 33.3                | Behavior During Reset                         |                |

| 33.4                | Programmable Registers                        |                |

| 22.1                | 1.09.44.44.40.00.00.00.00.00.00.00.00.00.00.  |                |

| Title           Chapter 34           Serial JTAG (SJTAG)           34.1         Overview                                                                                                                                          | Number   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Serial JTAG (SJTAG)  34.1 Overview                                                                                                                                                                                                |          |

| 34.2.1 Debugger Async Start Phase                                                                                                                                                                                                 |          |

| 34.2.1 Debugger Async Start Phase                                                                                                                                                                                                 | 34-1     |

| 34.2.2 i.MX23 Timing Mark Phase                                                                                                                                                                                                   | 34-2     |

| 34.2.3 Debugger Send TDI, Mode Phase                                                                                                                                                                                              | 34-3     |

| i.MX23 Wait For Return Clock Phase i.MX23 Sends TDO and Return Clock Timing Phase i.MX23 Terminate Phase j.MX23 Terminate Phase SJTAG External Pin Selecting Serial JTAG or Six-Wire JTAG Mode  Chapter 35 Boot Modes  Boot Modes | 34-3     |

| 34.2.5 34.2.6 34.2.7 34.2.7 SJTAG External Pin                                                                                                                                                                                    | 34-4     |

| 34.2.6 34.2.7 34.2.8 SJTAG External Pin Selecting Serial JTAG or Six-Wire JTAG Mode  Chapter 35 Boot Modes  Boot Modes                                                                                                            | 34-4     |

| 34.2.7 SJTAG External Pin                                                                                                                                                                                                         | 34-4     |

| 34.2.8 Selecting Serial JTAG or Six-Wire JTAG Mode                                                                                                                                                                                | 34-5     |

| Chapter 35 Boot Modes  Boot Modes                                                                                                                                                                                                 |          |

| Boot Modes Boot Modes                                                                                                                                                                                                             | 34-6     |

| 35.1 Boot Modes                                                                                                                                                                                                                   |          |

|                                                                                                                                                                                                                                   |          |

| 0                                                                                                                                                                                                                                 |          |

| 35.1.1 Boot Pins Definition and Mode Selection                                                                                                                                                                                    |          |

| 35.1.2 Boot Mode Selection Map                                                                                                                                                                                                    |          |

| 35.2 OTP eFuse and Persistent Bit Definitions                                                                                                                                                                                     |          |

| 35.2.1 OTP eFuse                                                                                                                                                                                                                  |          |

| 35.2.2 Persistent Bits                                                                                                                                                                                                            |          |

| 35.3 Memory Map                                                                                                                                                                                                                   |          |

| 35.4 General Boot Procedure                                                                                                                                                                                                       |          |

| 35.4.1 Preparing Bootable Images                                                                                                                                                                                                  |          |

| Constructing Image to Be Loaded by Boot Loader                                                                                                                                                                                    |          |

| 35.5 I <sup>2</sup> C Boot Mode                                                                                                                                                                                                   |          |

| 35.6 SPI Boot Mode                                                                                                                                                                                                                |          |

| 35.6.1 Media Format                                                                                                                                                                                                               |          |

| 35.6.2 SSP                                                                                                                                                                                                                        |          |

| 35.7 SD/MMC Boot Mode                                                                                                                                                                                                             |          |

| 35.7.1 Boot Control Block (BCB)                                                                                                                                                                                                   |          |

| 35.7.2 Master Boot Record (MBR)                                                                                                                                                                                                   |          |

| 35.7.3 Device Identification                                                                                                                                                                                                      |          |

| 35.8 NAND Boot Mode                                                                                                                                                                                                               |          |