## LLCC68 Datasheet

Long Range, Low Power, sub-GHz RF Transceiver

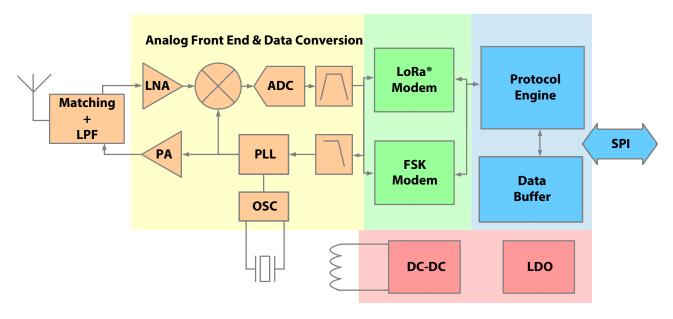

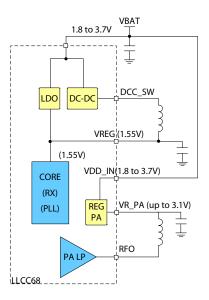

Figure A: LLCC68 Block Diagram

#### **General Description**

The LLCC68 sub-GHz radio transceiver is ideal for long range wireless applications. It is designed for long battery life with just 4.2mA of active receive current consumption. The LLCC68 can transmit up to +22dBm with highly efficient integrated power amplifiers.

The LLCC68 supports LoRa® modulation for LPWAN use cases and (G)FSK modulation for legacy use cases. The device is highly configurable to meet different application requirements utilizing the global LoRaWAN® standard or proprietary protocols.

The device is designed to comply with the physical layer requirements of the LoRaWAN specification released by the LoRa Alliance®.

The radio is suitable for systems targeting compliance with radio regulations including but not limited to ETSI EN 300 220, FCC CFR 47 Part 15, China regulatory requirements and the Japanese ARIB T-108. Continuous frequency coverage from 150MHz to 960MHz allows the support of all major sub-GHz ISM bands around the world.

#### **Applications**

The level of integration and the low consumption of the LLCC68 enable a new generation of Internet of Things applications.

- Smart meters

- Supply chain and logistics

- Building automation

- Agricultural sensors

- Smart cities

- Retail store sensors

- Asset tracking

- Street lights

- Parking sensors

- Environmental sensors

- Healthcare

- Safety and security sensors

- Remote control applications

## **Ordering Information**

| Part Number Package Type |     | Delivery    | Minimum Order Quantity |

|--------------------------|-----|-------------|------------------------|

| LLCC68IMLTRT             | QFN | Tape & Reel | 3,000 pieces           |

QFN 24 Package, Pb-free, Halogen free, RoHS/WEEE compliant product.

### **Revision History**

| Version | ECO    | Date      | Modifications                                                                    |

|---------|--------|-----------|----------------------------------------------------------------------------------|

| 1.0     | 047881 | July 2019 | First Release                                                                    |

|         |        |           | Modified Max val of BR_F to 500kb/s, FDA to 300kHz and updated Note Table 3-7    |

|         |        |           | Modified the Min value of ATCXO Table 3-7                                        |

|         |        |           | Reformatted Note in Max value of BW_F Table 3-8                                  |

|         |        |           | Added 500kb/s condition to RXS_2FB, BI_F and Note Table 3-8                      |

|         |        |           | Trimming capacitors cannot be deactivated Section 4.1.3                          |

|         |        |           | Added OCP max value Section 5.1                                                  |

|         |        |           | GMSK is supported Section 6.                                                     |

|         |        |           | Modified LoRa Time-on-air Section 6.1.4                                          |

|         |        |           | Added RSSI Calibration Section 6.1.6                                             |

|         |        |           | Added BW1000 to FSK packet bandwidth definitions and Note Table 6-5              |

|         |        |           | Added DIO3 as a Manual Switch Section 8.6                                        |

| 1.1     | 067443 | Doc 2024  | Added pseudo-code for image calibration Section 9.2.1                            |

| 1.1     | 067443 | Dec 2024  | Added Rx gain details when entering sleep with retention Section 9.6             |

|         |        |           | Added registers to Table 12-1 between 0x0805 and 0x0891 for BW1000 usage, & LoRa |

|         |        |           | Coding Rate RX and LoRa CRC Configuration Registers                              |

|         |        |           | Removed Wake-up on RTC timeout Section 13.1.1                                    |

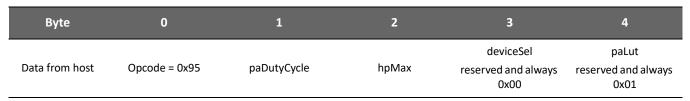

|         |        |           | Modified paDutyCycle description Section 13.1.14                                 |

|         |        |           | SetDio3AsTcxoCtrl min value Section 13.3.6                                       |

|         |        |           | GFSK Sync Word alignment information Section 13.4.6.1                            |

|         |        |           | Added SetLoRaSymbNumTimeout valid values Section 13.4.9                          |

|         |        |           | GetPacketStatus Section 13.5.3                                                   |

|         |        |           | Added Settling time to GetRSSIInst Section 13.5.4                                |

|         |        |           | Added LoRa coding rates with long interleave Table 13-49                         |

|         |        |           | Added Tape and Reel Section 16.5                                                 |

# **Table of Contents**

| 1. Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2. Pin Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12                                                       |

| 2.1 I/O Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                                       |

| 2.2 Package View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13                                                       |

| 3. Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14                                                       |

| 3.1 ESD Notice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14                                                       |

| 3.2 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14                                                       |

| 3.3 Operating Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14                                                       |

| 3.4 Crystal Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                       |

| 3.5 Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15                                                       |

| 3.5.1 Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                       |

| 3.5.2 General Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18                                                       |

| 3.5.3 Receive Mode Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19                                                       |

| 3.5.4 Transmit Mode Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21                                                       |

| 3.5.5 Digital I/O Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21                                                       |

| 4. Circuit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22                                                       |

| 4.1 Clock References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

| 4.1.1 RC Frequency References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |

| 4.1.2 High-Precision Frequency Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22                                                       |

| 4.1.3 XTAL Control Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23                                                       |

| 4.4 A TOVO Construct Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24                                                       |

| 4.1.4 TCXO Control Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

| 4.1.4 TCXO Control Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24                                                       |

| 4.2 Phase-Locked Loop (PLL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24<br>25                                                 |

| 4.2 Phase-Locked Loop (PLL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24<br>25<br>25                                           |

| 4.2 Phase-Locked Loop (PLL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24<br>25<br>25<br>27                                     |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                    | 24<br>25<br>25<br>27<br>28                               |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter  4.4.1 Power Amplifier Specifics                                                                                                                                                                                                                                                                                                                                                                                   | 24<br>25<br>25<br>27<br>28                               |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter  4.4.1 Power Amplifier Specifics  4.4.2 Power Amplifier Summary                                                                                                                                                                                                                                                                                                                                                    | 24<br>25<br>25<br>27<br>28<br>30                         |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter  4.4.1 Power Amplifier Specifics  4.4.2 Power Amplifier Summary  5. Power Distribution  5.1 Selecting DC-DC Converter or LDO Regulation  5.1.1 Option A: DC-DC Regulator                                                                                                                                                                                                                                           | 24<br>25<br>25<br>27<br>28<br>30<br>31<br>31             |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter  4.4.1 Power Amplifier Specifics  4.4.2 Power Amplifier Summary  5. Power Distribution  5.1 Selecting DC-DC Converter or LDO Regulation                                                                                                                                                                                                                                                                            | 24<br>25<br>25<br>27<br>28<br>30<br>31<br>31             |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter  4.4.1 Power Amplifier Specifics  4.4.2 Power Amplifier Summary  5. Power Distribution  5.1 Selecting DC-DC Converter or LDO Regulation  5.1.1 Option A: DC-DC Regulator  5.1.2 Option B: LDO Regulator  5.1.3 Consideration on the DC-DC Inductor Selection                                                                                                                                                       | 24<br>25<br>25<br>27<br>30<br>31<br>31<br>32<br>32       |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter  4.4.1 Power Amplifier Specifics  4.4.2 Power Amplifier Summary  5. Power Distribution  5.1 Selecting DC-DC Converter or LDO Regulation  5.1.1 Option A: DC-DC Regulator  5.1.2 Option B: LDO Regulator                                                                                                                                                                                                            | 24<br>25<br>25<br>27<br>30<br>31<br>31<br>32<br>32       |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter  4.4.1 Power Amplifier Specifics  4.4.2 Power Amplifier Summary  5. Power Distribution  5.1 Selecting DC-DC Converter or LDO Regulation  5.1.1 Option A: DC-DC Regulator  5.1.2 Option B: LDO Regulator  5.1.3 Consideration on the DC-DC Inductor Selection                                                                                                                                                       | 24 25 25 27 28 30 31 32 32 33 33                         |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter  4.4.1 Power Amplifier Specifics  4.4.2 Power Amplifier Summary.  5. Power Distribution  5.1 Selecting DC-DC Converter or LDO Regulation  5.1.1 Option A: DC-DC Regulator  5.1.2 Option B: LDO Regulator  5.1.3 Consideration on the DC-DC Inductor Selection  5.2 Flexible DIO Supply                                                                                                                             | 24<br>25<br>25<br>27<br>30<br>31<br>32<br>32<br>33       |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter  4.4.1 Power Amplifier Specifics  4.4.2 Power Amplifier Summary  5. Power Distribution  5.1 Selecting DC-DC Converter or LDO Regulation  5.1.1 Option A: DC-DC Regulator  5.1.2 Option B: LDO Regulator  5.1.3 Consideration on the DC-DC Inductor Selection  5.2 Flexible DIO Supply  6. Modems                                                                                                                   | 24<br>25<br>25<br>27<br>30<br>31<br>32<br>32<br>33<br>33 |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter  4.4.1 Power Amplifier Specifics  4.4.2 Power Amplifier Summary.  5. Power Distribution  5.1 Selecting DC-DC Converter or LDO Regulation  5.1.1 Option A: DC-DC Regulator.  5.1.2 Option B: LDO Regulator.  5.1.3 Consideration on the DC-DC Inductor Selection  5.2 Flexible DIO Supply  6. Modems  6.1 LoRa® Modem                                                                                               | 24 25 25 27 28 30 31 32 33 33 34 34 34                   |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter  4.4.1 Power Amplifier Specifics  4.4.2 Power Amplifier Summary.  5. Power Distribution  5.1 Selecting DC-DC Converter or LDO Regulation  5.1.1 Option A: DC-DC Regulator  5.1.2 Option B: LDO Regulator  5.1.3 Consideration on the DC-DC Inductor Selection  5.2 Flexible DIO Supply  6. Modems  6.1 LoRa® Modem  6.1.1 Modulation Parameter                                                                     | 24 25 25 27 30 31 31 32 33 34 34 34 34 36                |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter  4.4.1 Power Amplifier Specifics  4.4.2 Power Amplifier Summary.  5. Power Distribution  5.1 Selecting DC-DC Converter or LDO Regulation  5.1.1 Option A: DC-DC Regulator  5.1.2 Option B: LDO Regulator  5.1.3 Consideration on the DC-DC Inductor Selection  5.2 Flexible DIO Supply  6. Modems  6.1 LoRa® Modem  6.1.1 Modulation Parameter  6.1.2 LoRa Packet Engine  6.1.3 LoRa Frame  6.1.4 LoRa Time-on-Air | 24 25 25 27 30 31 32 33 33 34 34 34 36 36 37             |

| 4.2 Phase-Locked Loop (PLL)  4.3 Receiver  4.3.1 Intermediate Frequencies  4.4 Transmitter  4.4.1 Power Amplifier Specifics  4.4.2 Power Amplifier Summary  5. Power Distribution  5.1 Selecting DC-DC Converter or LDO Regulation  5.1.1 Option A: DC-DC Regulator  5.1.2 Option B: LDO Regulator  5.1.3 Consideration on the DC-DC Inductor Selection  5.2 Flexible DIO Supply  6. Modems  6.1 LoRa® Modem  6.1.1 Modulation Parameter  6.1.2 LoRa Packet Engine  6.1.3 LoRa Frame                          | 24 25 27 28 30 31 32 32 33 34 34 34 34 34 37             |

| 6.2 FSK Modem                                           | 39 |

|---------------------------------------------------------|----|

| 6.2.1 Modulation Parameter                              | 39 |

| 6.2.2 FSK Packet Engine                                 | 41 |

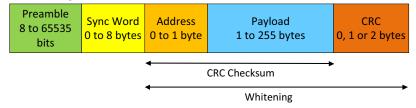

| 6.2.3 FSK Packet Format                                 | 42 |

| 6.2.4 Special Settings for BRF= 0.6kbps and 1.2kbps     | 45 |

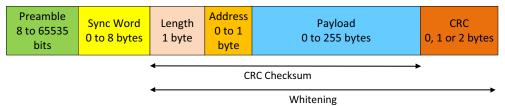

| 7. Data Buffer                                          | 46 |

| 7.1 Principle of Operation                              | 46 |

| 7.2 Data Buffer in Receive Mode                         | 47 |

| 7.3 Data Buffer in Transmit Mode                        | 47 |

| 7.4 Using the Data Buffer                               | 47 |

| 8. Digital Interface and Control                        | 48 |

| 8.1 Reset                                               | 48 |

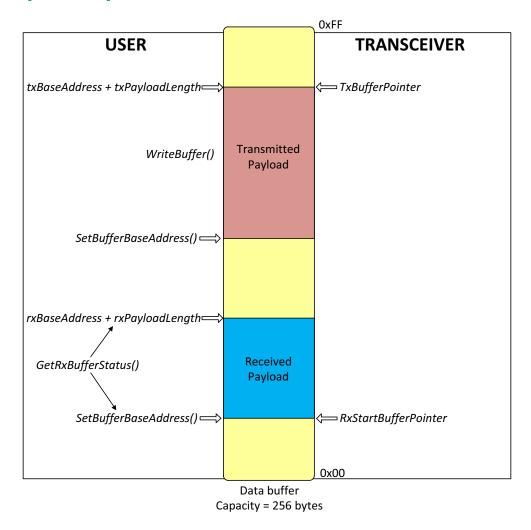

| 8.2 SPI Interface                                       | 48 |

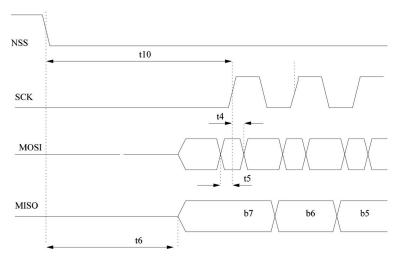

| 8.2.1 SPI Timing When the Transceiver is in Active Mode | 48 |

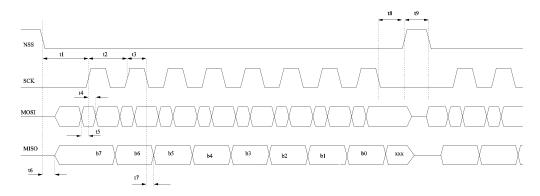

| 8.2.2 SPI Timing When the Transceiver Leaves Sleep Mode | 49 |

| 8.3 Multi-Purpose Digital Input/Output (DIO)            | 50 |

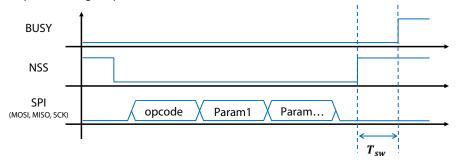

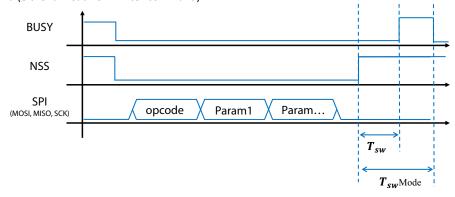

| 8.3.1 BUSY Control Line                                 | 50 |

| 8.3.2 Digital Input/Output                              | 52 |

| 8.4 Digital Interface Status versus Chip modes          | 52 |

| 8.5 IRQ Handling                                        | 53 |

| 8.6 DIO3 as a Manual Switch Control                     | 54 |

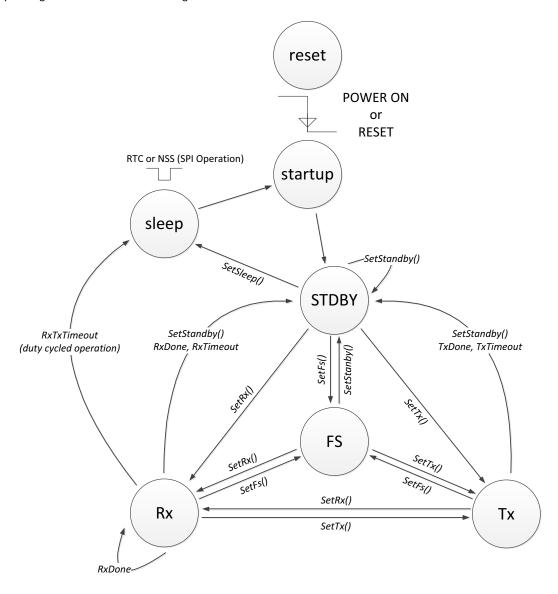

| 9. Operational Modes                                    | 55 |

| 9.1 Startup                                             | 55 |

| 9.2 Calibration                                         | 55 |

| 9.2.1 Image Calibration for Specific Frequency Bands    | 56 |

| 9.3 Sleep Mode                                          | 56 |

| 9.4 Standby (STDBY) Mode                                | 57 |

| 9.5 Frequency Synthesis (FS) Mode                       | 57 |

| 9.6 Receive (RX) Mode                                   | 57 |

| 9.7 Transmit (TX) Mode                                  | 58 |

| 9.7.1 PA Ramping                                        | 58 |

| 9.8 Active Mode Switching Time                          | 58 |

| 9.9 Transceiver Circuit Modes Graphic                   | 59 |

| 10. Host Controller Interface                           | 60 |

| 10.1 Command Structure                                  | 60 |

| 10.2 Transaction Termination                            | 60 |

| 11. List of Commands                                    | 61 |

| 11.1 Operational Modes Commands                         | 61 |

| 11.2 Register and Buffer Access Commands                | 62 |

| 11.3 DIO and IRQ Control                                | 62 |

| 11.4 RF, Modulation and Packet Commands                 | 62 |

| 11.5 Status Commands                                    |    |

| 12. Register Map                                        | 64 |

| 13. Commands Interface                                  | 66 |

| 13.1 Operational Modes Functions                | 66 |

|-------------------------------------------------|----|

| 13.1.1 SetSleep                                 | 66 |

| 13.1.2 SetStandby                               | 67 |

| 13.1.3 SetFs                                    | 67 |

| 13.1.4 SetTx                                    | 68 |

| 13.1.5 SetRx                                    | 69 |

| 13.1.6 StopTimerOnPreamble                      | 70 |

| 13.1.7 SetRxDutyCycle                           | 71 |

| 13.1.8 SetCAD                                   | 73 |

| 13.1.9 SetTxContinuousWave                      | 73 |

| 13.1.10 SetTxInfinitePreamble                   | 73 |

| 13.1.11 SetRegulatorMode                        | 74 |

| 13.1.12 Calibrate Function                      | 74 |

| 13.1.13 CalibrateImage                          | 75 |

| 13.1.14 SetPaConfig                             | 75 |

| 13.1.15 SetRxTxFallbackMode                     | 76 |

| 13.2 Registers and Buffer Access                | 77 |

| 13.2.1 WriteRegister Function                   | 77 |

| 13.2.2 ReadRegister Function                    | 77 |

| 13.2.3 WriteBuffer Function                     | 77 |

| 13.2.4 ReadBuffer Function                      | 78 |

| 13.3 DIO and IRQ Control Functions              | 78 |

| 13.3.1 SetDioIrqParams                          | 78 |

| 13.3.2 IrqMask                                  | 78 |

| 13.3.3 GetlrqStatus                             | 79 |

| 13.3.4 ClearIrqStatus                           | 79 |

| 13.3.5 SetDIO2AsRfSwitchCtrl                    | 80 |

| 13.3.6 SetDIO3AsTCXOCtrl                        | 81 |

| 13.4 RF Modulation and Packet-Related Functions | 82 |

| 13.4.1 SetRfFrequency                           | 82 |

| 13.4.2 SetPacketType                            | 82 |

| 13.4.3 GetPacketType                            | 83 |

| 13.4.4 SetTxParams                              | 83 |

| 13.4.5 SetModulationParams                      | 84 |

| 13.4.6 SetPacketParams                          | 87 |

| 13.4.7 SetCadParams                             | 92 |

| 13.4.8 SetBufferBaseAddress                     | 93 |

| 13.4.9 SetLoRaSymbNumTimeout                    | 93 |

| 13.5 Communication Status Information           | 94 |

| 13.5.1 GetStatus                                | 94 |

| 13.5.2 GetRxBufferStatus                        | 95 |

| 13.5.3 GetPacketStatus                          | 95 |

| 13.5.4 GetRssiInst                              | 96 |

| 13.5.5 GetStats                                 | 97 |

|       | 13.5.6 ResetStats                                           | 97  |

|-------|-------------------------------------------------------------|-----|

|       | 13.6 Miscellaneous                                          | 98  |

|       | 13.6.1 GetDeviceErrors                                      | 98  |

|       | 13.6.2 ClearDeviceErrors                                    | 98  |

| 14.   | Application                                                 | 99  |

|       | 14.1 HOST API Basic Read Write Function                     | 99  |

|       | 14.2 Circuit Configuration for Basic Tx Operation           | 99  |

|       | 14.3 Circuit Configuration for Basic Rx Operation           | 100 |

|       | 14.4 Issuing Commands in the Right Order                    | 100 |

|       | 14.5 Application Schematics                                 | 101 |

|       | 14.5.1 Application Design of the LLCC68 with RF Switch      | 101 |

| 15. I | Known Limitations                                           | 102 |

|       | 15.1 Modulation Quality with 500kHz LoRa Bandwidth          | 102 |

|       | 15.1.1 Description                                          | 102 |

|       | 15.1.2 Workaround                                           | 102 |

|       | 15.2 Better Resistance of the LLCC68 Tx to Antenna Mismatch | 103 |

|       | 15.2.1 Description                                          | 103 |

|       | 15.2.2 Workaround                                           | 103 |

|       | 15.3 Implicit Header Mode Timeout Behavior                  | 104 |

|       | 15.3.1 Description                                          | 104 |

|       | 15.3.2 Workaround                                           | 104 |

|       | 15.4 Optimizing the Inverted IQ Operation                   | 104 |

|       | 15.4.1 Description                                          | 104 |

|       | 15.4.2 Workaround                                           | 104 |

| 16. I | Packaging Information                                       | 105 |

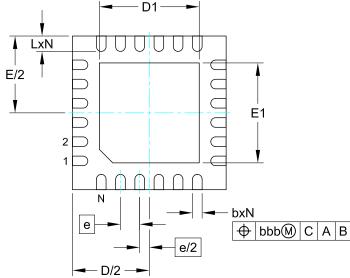

|       | 16.1 Package Outline Drawing                                | 105 |

|       | 16.2 Package Marking                                        | 106 |

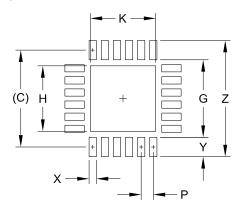

|       | 16.3 Land Pattern                                           | 106 |

|       | 16.4 Reflow Profiles                                        | 107 |

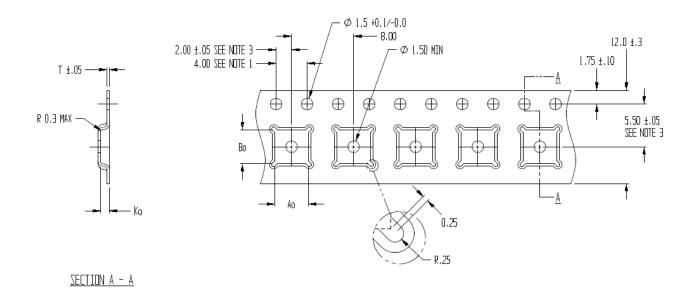

|       | 16.5 Tane and Real Information                              | 107 |

# **List of Figures**

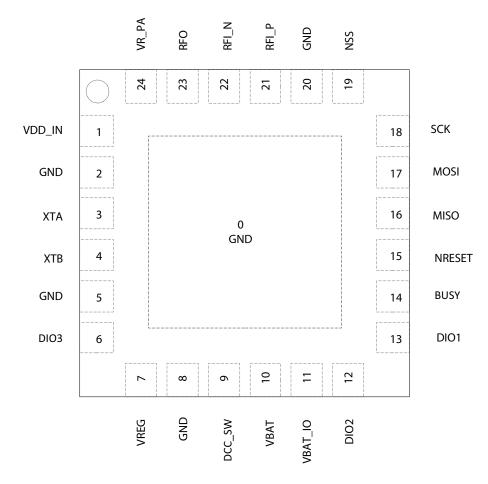

| Figure 2-1: LLCC68 Top View Pin Location QFN 4x4 24L              | 13  |

|-------------------------------------------------------------------|-----|

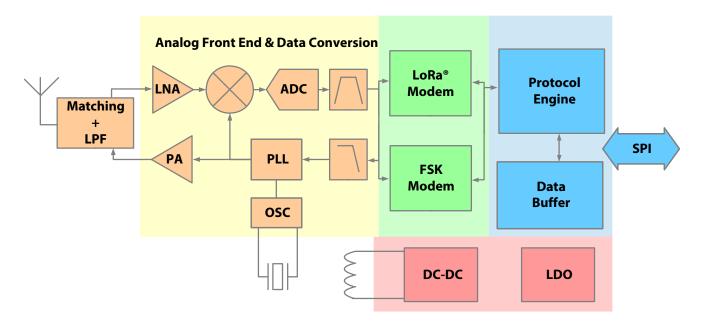

| Figure 4-1: LLCC68 Block Diagram                                  | 22  |

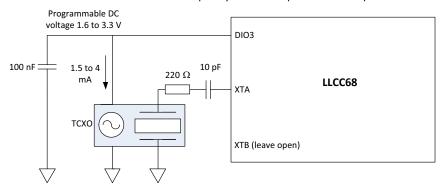

| Figure 4-2: TCXO Control Block                                    | 24  |

| Figure 4-3: PA Supply Scheme in DC-DC Mode                        | 27  |

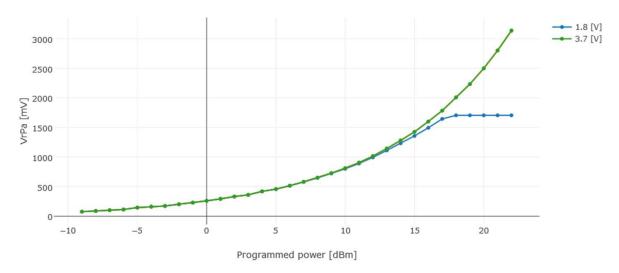

| Figure 4-4: VR_PA versus Output Power on the LLCC68               | 28  |

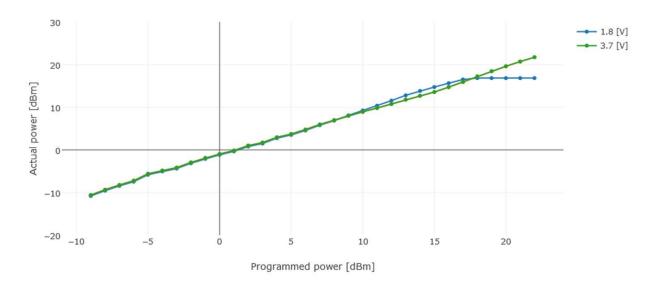

| Figure 4-5: Power Linearity on the LLCC68                         | 29  |

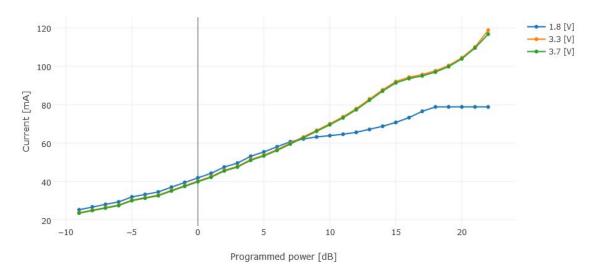

| Figure 4-6: Current versus Programmed Output Power on the LLCC68  | 29  |

| Figure 5-1: LLCC68 Diagram with the DC-DC Regulator Power Option  | 32  |

| Figure 5-2: LLCC68 Diagram with the LDO Regulator Power Option    | 32  |

| Figure 5-3: Separate DIO Supply                                   | 33  |

| Figure 6-1: LoRa® Signal Bandwidth                                |     |

| Figure 6-2: LoRa Packet Format                                    | 36  |

| Figure 6-3: Fixed-Length Packet Format                            | 42  |

| Figure 6-4: Variable-Length Packet Format                         | 42  |

| Figure 6-5: Data Whitening LFSR                                   | 43  |

| Figure 7-1: Data Buffer Diagram                                   | 46  |

| Figure 8-1: SPI Timing Diagram                                    | 48  |

| Figure 8-2: SPI Timing Transition                                 |     |

| Figure 8-3: Switching Time Definition                             | 50  |

| Figure 8-4: Switching Time Definition in Active Mode              |     |

| Figure 9-1: Transceiver Circuit Modes                             | 59  |

| Figure 13-1: Stopping Timer on Preamble or Header Detection       | 70  |

| Figure 13-2: RX Duty Cycle Energy Profile                         |     |

| Figure 13-3: RX Duty Cycle when Receiving                         | 72  |

| Figure 14-1: Application Schematic of the LLCC68 with RF Switch 1 | 01  |

| Figure 16-1: QFN 4x4mm Package Outline Drawing 1                  | 05  |

| Figure 16-2: LLCC68 Marking 1                                     | 06  |

| Figure 16-3: QFN 4x4mm Land Pattern Drawing 1                     | 06  |

| Figure 16-4: Tape and Reel Drawing 1                              | .07 |

# **List of Tables**

| Table 2-1: LLCC68 Pinout In QFN 4x4 24L                            | 12 |

|--------------------------------------------------------------------|----|

| Table 3-1: ESD and Latch-up Notice                                 | 14 |

| Table 3-2: Absolute Maximum Ratings                                | 14 |

| Table 3-3: Operating Range                                         | 14 |

| Table 3-4: Crystal Specifications                                  | 15 |

| Table 3-5: Power Consumption                                       | 16 |

| Table 3-6: Power Consumption in Transmit Mode                      | 17 |

| Table 3-7: General Specifications                                  | 18 |

| Table 3-8: Receive Mode Specifications                             | 19 |

| Table 3-9: Transmit Mode Specifications                            | 21 |

| Table 3-10: Digital I/O Specifications                             | 21 |

| Table 4-1: Internal Foot Capacitor Configuration                   | 23 |

| Table 4-2: Intermediate Frequencies in FSK Mode                    | 25 |

| Table 4-3: Intermediate Frequencies in LoRa Mode                   | 26 |

| Table 4-4: Power Amplifier Summary                                 | 30 |

| Table 5-1: Regulation Type versus Circuit Mode                     | 31 |

| Table 5-2: OCP Configuration                                       | 31 |

| Table 5-3: Recommended 15µH Inductors                              | 33 |

| Table 6-1: Range of Spreading Factors (SF)                         | 35 |

| Table 6-2: Signal Bandwidth Setting in LoRa® Mode                  | 35 |

| Table 6-3: Coding Rate Overhead                                    | 36 |

| Table 6-4: Registers and Values                                    | 38 |

| Table 6-5: Bandwidth Definition in FSK Packet Type                 | 39 |

| Table 6-6: Whitening Initial Value                                 | 43 |

| Table 6-7: CRC Type Configuration                                  | 44 |

| Table 6-8: CRC Initial Value                                       | 44 |

| Table 6-9: CRC Polynomial                                          | 44 |

| Table 8-1: SPI Timing Requirements                                 | 49 |

| Table 8-2: Switching Time                                          | 51 |

| Table 8-3: Digital Pads Configuration for each Chip Mode           | 52 |

| Table 8-4: IRQ Status Registers                                    | 53 |

| Table 9-1: LLCC68 Operating Modes                                  | 55 |

| Table 9-2: Image Calibration Over the ISM Bands                    | 56 |

| Table 9-3: Rx Gain Configuration                                   | 57 |

| Table 10-1: SPI Interface Command Sequence                         | 60 |

| Table 11-1: Commands Selecting the Operating Modes of the Radio    | 61 |

| Table 11-2: Commands to Access the Radio Registers and FIFO Buffer | 62 |

| Table 11-3: Commands Controlling the Radio IRQs and DIOs           | 62 |

| Table 11-4: Commands Controlling the RF and Packets Settings       | 62 |

| Table 11-5: Commands Returning the Radio Status                    | 63 |

| Table 12-1: List of Registers                                      | 64 |

| Table 13-1: SetSleep SPI Transaction                               | 66 |

| Table 13-2: Sleep Mode Definition                                  | 66 |

| Table 13-3: SetConfig SPI Transaction                              | 67 |

| Table 13-4: STDBY Mode Configuration                               | 67 |

| Table 13-5: SetFs SPI Transaction                                  | 67 |

| Table 13-6: SetTx SPI Transaction                                  | 68 |

| Table 13-7: SetTx Timeout Duration                                 | 68 |

|                                                                    |    |

| Table 12.0. Cat D.: CDI Transportion                           | <b>CO</b> |

|----------------------------------------------------------------|-----------|

| Table 13-8: SetRx SPI Transaction                              |           |

| Table 13-10: StopTimerOnPreamble SPI Transaction               |           |

| Table 13-10: StopOnPreambleParam Definition                    |           |

|                                                                |           |

| Table 13-12: SetRxDutyCycle SPI Transaction                    |           |

| Table 13-13: SetCAD SPI Transaction                            |           |

| Table 13-14: SetTxContinuousWave SPI Transaction               |           |

| Table 13-15: SetTxInfinitePreamble SPI Transaction             |           |

| Table 13-16: SetRegulatorMode SPI Transaction                  |           |

| Table 13-17: Calibrate SPI Transaction                         |           |

| Table 13-18: Calibration Setting                               |           |

| Table 13-19: CalibrateImage SPI Transaction                    |           |

| Table 13-20: SetPaConfig SPI Transaction                       |           |

| Table 13-21: PA Operating Modes with Optimal Settings          |           |

| Table 13-22: SetRxTxFallbackMode SPI Transaction               |           |

| Table 13-23: FallbackMode Definition                           |           |

| Table 13-24: WriteRegister SPI Transaction                     |           |

| Table 13-25: ReadRegister SPI Transaction                      |           |

| Table 13-26: WriteBuffer SPI Transaction                       | 77        |

| Table 13-27: ReadBuffer SPI Transaction                        |           |

| Table 13-28: SetDioIrqParams SPI Transaction                   |           |

| Table 13-29: IRQ Registers                                     | 79        |

| Table 13-30: GetIrqStatus SPI Transaction                      | 79        |

| Table 13-31: ClearIrqStatus SPI Transaction                    | 79        |

| Table 13-32: SetDIO2AsRfSwitchCtrl SPI Transaction             | 80        |

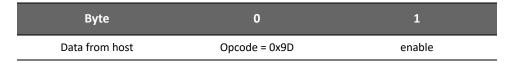

| Table 13-33: Enable Configuration Definition                   | 80        |

| Table 13-34: SetDIO3asTCXOCtrl SPI Transaction                 |           |

| Table 13-35: tcxoVoltage Configuration Definition              |           |

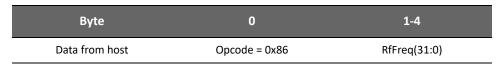

| Table 13-36: SetRfFrequency SPI Transaction                    |           |

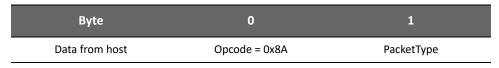

| Table 13-37: SetPacketType SPI Transaction                     |           |

| Table 13-38: PacketType Definition                             |           |

| Table 13-39: GetPacketType SPI Transaction                     |           |

| Table 13-40: SetTxParams SPI Transaction                       |           |

| Table 13-41: RampTime Definition                               |           |

| Table 13-42: SetModulationParams SPI Transaction               |           |

| Table 13-43: GFSK ModParam1, ModParam2 & ModParam3 - br        |           |

| Table 13-44: GFSK ModParam4 - PulseShape                       |           |

| Table 13-44. Gr SK ModParam5 - Bandwidth                       |           |

| Table 13-45: GFSK ModParam6, ModParam7 & ModParam8 - Fdev      |           |

| Table 13-46. Gran ModParam1- SF                                |           |

| Table 13-48: LoRa ModParam2 - BW                               |           |

|                                                                |           |

| Table 13-49: LoRa ModParam3 - CR                               |           |

| Table 13-50: LoRa ModParam4 - LowDataRateOptimize              |           |

| Table 13-51: SetPacketParams SPI Transaction                   |           |

| Table 13-52: GFSK PacketParam1 & PacketParam2 - PreambleLength |           |

| Table 13-53: GFSK PacketParam3 - PreambleDetectorLength        |           |

| Table 13-54: GFSK PacketParam4 - SyncWordLength                |           |

| Table 13-55: Sync Word Programming                             |           |

| Table 13-56: GFSK PacketParam5 - AddrComp                      |           |

| Table 13-57: Node Address Programming                          |           |

| Table 13-58: Broadcast Address Programming                     | 88        |

| Table 13-59: GFSK PacketParam6 - PacketType                    | 89 |

|----------------------------------------------------------------|----|

| Table 13-60: GFSK PacketParam7 - PayloadLength                 | 89 |

| Table 13-61: GFSK PacketParam8 - CRCType                       | 89 |

| Table 13-62: CRC Initial Value Programming                     | 89 |

| Table 13-63: CRC Polynomial Programming                        | 89 |

| Table 13-64: GFSK PacketParam9 - Whitening                     | 90 |

| Table 13-65: Whitening Initial Value                           | 90 |

| Table 13-66: LoRa PacketParam1 & PacketParam2 - PreambleLength | 91 |

| Table 13-67: LoRa PacketParam3 - HeaderType                    | 91 |

| Table 13-68: LoRa PacketParam4 - PayloadLength                 | 91 |

| Table 13-69: LoRa PacketParam5 - CRCType                       | 91 |

| Table 13-70: LoRa PacketParam6 - InvertIQ                      | 91 |

| Table 13-71: SetCadParams SPI Transaction                      | 92 |

| Table 13-72: CAD Number of Symbol Definition                   |    |

| Table 13-73: CAD Exit Mode Definition                          | 92 |

| Table 13-74: SetBufferBaseAddress SPI Transaction              | 93 |

| Table 13-75: SetLoRaSymbNumTimeout SPI Transaction             |    |

| Table 13-76: Status Bytes Definition                           | 94 |

| Table 13-77: GetStatus SPI Transaction                         | 94 |

| Table 13-78: GetRxBufferStatus SPI Transaction                 | 95 |

| Table 13-79: GetPacketStatus SPI Transaction                   | 95 |

| Table 13-80: Status Fields                                     | 95 |

| Table 13-81: GetRssiInst SPI Transaction                       |    |

| Table 13-82: RSSI Settling Time per Bandwidth                  | 96 |

| Table 13-83: GetStats SPI Transaction                          | 97 |

| Table 13-84: ResetStats SPI Transaction                        | 97 |

| Table 13-85: GetDeviceErrors SPI Transaction                   |    |

| Table 13-86: OpError Bits                                      | 98 |

| Table 13-87: ClearDeviceErrors SPI Transaction                 | 98 |

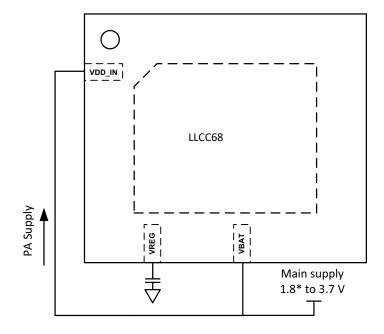

## 1. Architecture

The LLCC68 is a half-duplex transceiver capable of low power operation in the 150-960MHz ISM frequency band. The radio comprises four main blocks:

- 1. **Analog Front End**: The transmit and receive chains, as well as the data converter interface to ensuing digital blocks. The LLCC68 transceiver is capable of delivering up to +22dBm with the battery supply.

- 2. **Digital Modem Bank**: a range of modulation options is available in the LLCC68:

- ◆ LoRa Rx/Tx, BW = 125 -250 500kHz

- ◆ LoRa SF = 5 6 7 8 9 for BW = 125kHz

- ◆ LoRa SF = 5 6 7 8 9 10 for BW = 250kHz

- ◆ LoRa SF = 5 6 7 8 9 10 11 for BW = 500kHz

- (G)FSK Rx/Tx, with BR = 0.6 500kb/s

- 3. **Digital Interface and Control**: this comprises all payload data and protocol processing as well as access to configuration of the radio via the SPI interface.

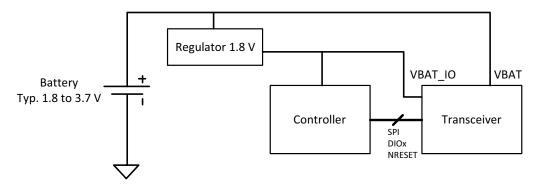

- 4. **Power Distribution**: two forms of voltage regulation, DC-DC or linear regulator LDO, are available depending upon the design priorities of the application.

# 2. Pin Connection

# 2.1 I/O Description

Table 2-1: LLCC68 Pinout In QFN 4x4 24L

| Pin<br>Number | Pin<br>Name | Type<br>(I = Input<br>O = Output) | Description                                                                  |

|---------------|-------------|-----------------------------------|------------------------------------------------------------------------------|

| 0             | GND         | -                                 | Exposed Ground pad                                                           |

| 1             | VDD_IN      | I                                 | Input voltage for power amplifier regulator, VR_PA: connected to pin 10      |

| 2             | GND         | -                                 | Ground                                                                       |

| 3             | XTA         | -                                 | Crystal oscillator connection, can be used to input external reference clock |

| 4             | ХТВ         | -                                 | Crystal oscillator connection                                                |

| 5             | GND         | -                                 | Ground                                                                       |

| 6             | DIO3        | I/O                               | Multi-purpose digital I/O - external TCXO supply voltage                     |

| 7             | VREG        | 0                                 | Regulated output voltage from the internal regulator LDO / DC-DC             |

| 8             | GND         | -                                 | Ground                                                                       |

| 9             | DCC_SW      | 0                                 | DC-DC Switcher Output                                                        |

| 10            | VBAT        | I                                 | Supply for the RFIC                                                          |

| 11            | VBAT_IO     | I                                 | Supply for the Digital I/O interface pins (except DIO3)                      |

| 12            | DIO2        | I/O                               | Multi-purpose digital I/O / RF Switch control                                |

| 13            | DIO1        | I/O                               | Multi-purpose digital IO                                                     |

| 14            | BUSY        | 0                                 | Busy indicator                                                               |

| 15            | NRESET      | I                                 | Reset signal, active low                                                     |

| 16            | MISO        | 0                                 | SPI slave output                                                             |

| 17            | MOSI        | I                                 | SPI slave input                                                              |

| 18            | SCK         | I                                 | SPI clock                                                                    |

| 19            | NSS         | I                                 | SPI Slave Select                                                             |

| 20            | GND         | -                                 | Ground                                                                       |

| 21            | RFI_P       | I                                 | RF receiver input                                                            |

| 22            | RFI_N       | I                                 | RF receiver input                                                            |

| 23            | RFO         | 0                                 | RF transmitter output                                                        |

| 24            | VR_PA       | -                                 | Regulated power amplifier supply                                             |

|               | •           | •                                 |                                                                              |

# 2.2 Package View

Figure 2-1: LLCC68 Top View Pin Location QFN 4x4 24L

# 3. Specifications

## 3.1 ESD Notice

The LLCC68 transceiver is a high-performance radio frequency device, with high ESD and latch-up resistance. The chip should be handled with all the necessary ESD precautions to avoid any permanent damage.

Table 3-1: ESD and Latch-up Notice

| Symbol  | Description                                                           | Min | Тур | Max  | Unit |

|---------|-----------------------------------------------------------------------|-----|-----|------|------|

| ESD_HBM | Class 2 of ANSI/ESDA/JEDEC Standard JS-001-2014<br>(Human Body Model) | -   | -   | 2.0  | kV   |

| ESD_CDM | ESD Charged Device Model, JEDEC standard JESD22-C101D, class III      | -   | -   | 1000 | V    |

| LU      | Latch-up, JEDEC standard JESD78 B, class I level A                    | -   | -   | 100  | mA   |

# 3.2 Absolute Maximum Ratings

Stresses above the values listed below may cause permanent device failure. Exposure to absolute maximum ratings for extended periods may affect device reliability, reducing product life time.

**Table 3-2: Absolute Maximum Ratings**

| Symbol | Description                                 | Min  | Тур | Max | Unit |

|--------|---------------------------------------------|------|-----|-----|------|

| VDDmr  | Supply voltage, applies to VBAT and VBAT_IO | -0.5 | -   | 3.9 | V    |

| Tmr    | Temperature                                 | -55  | -   | 125 | °C   |

| Pmr    | RF Input level                              | -    | -   | 10  | dBm  |

# 3.3 Operating Range

Operating ranges define the limits for functional operation and parametric characteristics of the device. Functionality outside these limits is not guaranteed.

Table 3-3: Operating Range

| Symbol | Description                                 | Min | Тур | Max  | Unit |

|--------|---------------------------------------------|-----|-----|------|------|

| VDDop  | Supply voltage, applies to VBAT and VBAT_IO | 1.8 | -   | 3.7  | V    |

| Тор    | Temperature under bias                      | -40 | -   | 85   | °C   |

| Clop   | Load capacitance on digital ports           | -   | -   | 20   | pF   |

| ML     | RF Input power                              | -   | -   | 0    | dBm  |

| VSWR   | Voltage Standing Wave Ratio at antenna port | -   | -   | 10:1 | -    |

# 3.4 Crystal Specifications

**Table 3-4: Crystal Specifications**

| Symbol | Description                  | Min | Тур  | Max | Unit |

|--------|------------------------------|-----|------|-----|------|

| FXOSC  | Crystal oscillator frequency | -   | 32   | -   | MHz  |

| CLOAD  | Crystal load capacitance     | -   | 10   | -   | pF   |

| COXTAL | Crystal shunt capacitance    | 0.3 | 0.6  | 2   | pF   |

| RSXTAL | Crystal series resistance    | -   | 30   | 60  | Ω    |

| CMXTAL | Crystal motional capacitance | 1.3 | 1.89 | 2.5 | fF   |

| DRIVE  | Drive level                  | -   | -    | 100 | μW   |

The reference frequency accuracy is defined by the complete system, and should take into account precision of the transmitter and the receiver, as well as environmental parameters such as extreme temperature limits. In a LoRaWAN system, the expected reference frequency accuracy on the end-device should be about +/- 30ppm under all operating conditions. This includes initial error, temperature drift and ageing over the lifetime of the product.

# 3.5 Electrical Specifications

The electrical specifications are given with the following conditions unless otherwise specified:

- VBAT IO = VBAT = 3.3V, all current consumptions are given for VBAT connected to VBAT IO

- Temperature = 25°C

- FXOSC = 32MHz, with specified crystal

- F<sub>RF</sub> = 434/490/868/915 MHz

- All RF impedances matched

- Transmit mode output power defined into a  $50\Omega$  load impedance

- FSK BER = 0.1%, 2-level FSK modulation without pre-filtering, BR = 4.8kb/s, FDA = ± 5kHz, BW F = 20kHz double-sided

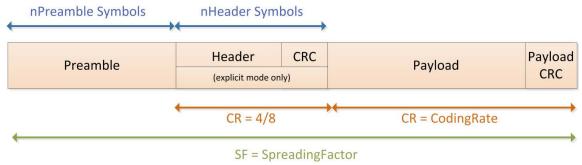

- LoRa PER = 1%, packet 64 bytes, preamble 8 symbols, CR = 4/5, CRC on payload enabled, explicit header mode

- RX/TX specifications given using default RX gain step and direct tie connection between Rx and Tx

- Blocking immunity, ACR and co-channel rejection are given for a single tone (CW) interferer and referenced to sensitivity +3dB

- Optional TCXO and RF Switch power consumption always excluded

#### Caution!

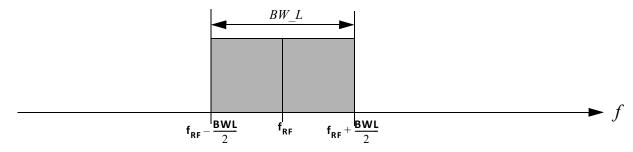

Throughout this document, all receiver bandwidths are expressed as "double-sideband". This is valid for LoRa and FSK modulations.

## 3.5.1 Power Consumption

**Table 3-5: Power Consumption**

| Symbol | Mode                                                        | Conditions                                                                                     | Min              | Тур                      | Max         | Unit           |

|--------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------|--------------------------|-------------|----------------|

| IDDOFF | OFF mode<br>(SLEEP mode<br>with cold start <sup>1</sup> )   | All blocks off                                                                                 | -                | 160                      | -           | nA             |

| IDDSL  | SLEEP mode<br>(SLEEP mode<br>with warm start <sup>2</sup> ) | Configuration retained Configuration retained + RC64k                                          |                  | 600<br>1.2               | -           | nA<br>μA       |

| IDDSBR | STDBY_RC mode                                               | RC13M, XOSC OFF                                                                                | -                | 0.6                      | -           | mA             |

| IDDSBX | STDBY_XOSC mode                                             | XOSC ON                                                                                        | -                | 0.8                      | -           | mA             |

| IDDFS  | Synthesizer mode                                            | DC-DC mode used LDO mode used                                                                  | -                | 2.1<br>3.55              | -           | mA<br>mA       |

|        | Receive mode<br>DC-DC mode used                             | FSK 4.8kb/s<br>LoRa 125kHz<br>Rx Boosted <sup>3</sup> , FSK 4.8kb/s<br>Rx Boosted, LoRa 125kHz | -<br>-<br>-<br>- | 4.2<br>4.6<br>4.8<br>5.3 | -<br>-<br>- | mA<br>mA<br>mA |

| IDDRX  |                                                             | LoRa 125kHz, VBAT = 1.8V                                                                       | -                | 8.2                      | -           | mA             |

| _      | Receive mode<br>LDO mode used                               | FSK 4.8kb/s<br>LoRa 125kHz<br>Rx Boosted, FSK 4.8kb/s<br>Rx Boosted, LoRa 125kHz               | -<br>-<br>-      | 8<br>8.8<br>9.3<br>10.1  | -<br>-<br>- | mA<br>mA<br>mA |

<sup>1.</sup> Cold start is equivalent to the device at POR or when it wakes up from Sleep mode with all blocks OFF, see Section 13.1.1 "SetSleep" on page 66

<sup>2.</sup> Warm start only happens when the device is woken from Sleep mode with its configuration retained, see Section 13.1.1 "SetSleep" on page 66

<sup>3.</sup> For more details on how to set the device in Rx Boosted gain mode, see Section 9.6 "Receive (RX) Mode" on page 57

**Table 3-6: Power Consumption in Transmit Mode**

| Symbol             | Frequency Band          | PA Match / Condition                   | Power Output | Typical | Unit |

|--------------------|-------------------------|----------------------------------------|--------------|---------|------|

|                    |                         |                                        | +22dBm       | 118     | mA   |

|                    |                         | +22dBm                                 | +20dBm       | 102     | mA   |

|                    |                         | +ZZUDIII                               | +17dBm       | 95      | mA   |

|                    | 000/0451411             |                                        | +14dBm       | 90      | mA   |

|                    | 868/915MHz <sup>-</sup> | +20dBm / optimal settings <sup>2</sup> | +20dBm       | 84      | mA   |

|                    |                         | +17dBm / optimal settings <sup>2</sup> | +17dBm       | 58      | mA   |

| IDDTV <sup>1</sup> |                         | +14dBm / optimal settings <sup>2</sup> | +14dBm       | 45      | mA   |

| IDDTX <sup>1</sup> |                         |                                        | +22dBm       | 107     | mA   |

|                    |                         | . 22 In                                | +20dBm       | 90      | mA   |

|                    |                         | +22dBm                                 | +17dBm       | 75      | mA   |

|                    | 42.4/4005411            |                                        | +14dBm       | 63      | mA   |

|                    | 434/490MHz -            | +20dBm / optimal settings <sup>2</sup> | +20dBm       | 65      | mA   |

|                    | _                       | +17dBm / optimal settings <sup>2</sup> | +17dBm       | 42      | mA   |

|                    | -                       | +14dBm / optimal settings <sup>2</sup> | +14dBm       | 32      | mA   |

<sup>1.</sup> DC-DC mode is used for the IC core but the PA is supplied from VBAT. For more details, see Section 5.1 "Selecting DC-DC Converter or LDO Regulation" on page 31

<sup>2.</sup> Optimal settings adapted to the specified output power. For more details, see Section 13.1.14.1 "PA Optimal Settings" on page 76

## 3.5.2 General Specifications

**Table 3-7: General Specifications**

| Symbol            | Description                                                                             | Conditions                                                                                                                    | Min   | Тур         | Max                                                  | Unit     |

|-------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|-------------|------------------------------------------------------|----------|

| FR                | Synthesizer frequency range                                                             |                                                                                                                               | 150   | -           | 960                                                  | MHz      |

| FSTEP             | Synthesizer frequency step                                                              | Bit 2 of TxModulation = 1 (main use) Bit 2 of TxModulation = 0 (see Section 15.)                                              | -     | 0.95<br>122 | -                                                    | Hz<br>Hz |

|                   |                                                                                         | 1kHz offset                                                                                                                   | -     | -75         | -                                                    | dBc/Hz   |

|                   | Synthesizer phase noise                                                                 | 10kHz offset                                                                                                                  | -     | -95         | -                                                    | dBc/Hz   |

| PHN <sup>12</sup> | (for 868 / 915MHz)                                                                      | 100kHz offset                                                                                                                 | -     | -100        | -                                                    | dBc/Hz   |

|                   | ,                                                                                       | 1MHz offset                                                                                                                   | -     | -120        | -                                                    | dBc/Hz   |

|                   |                                                                                         | 10MHz offset                                                                                                                  | -     | -135        | -                                                    | dBc/Hz   |

| TS_FS             | Synthesizer wake-up time                                                                | From STDBY_XOSC mode                                                                                                          | -     | 40          | -                                                    | μs       |

| TS_OSC            | Crystal oscillator<br>wake-up time                                                      | from STDBY_RC <sup>3</sup>                                                                                                    | -     | 150         | -                                                    | μs       |

| OSC_TRM           | Crystal oscillator trimming range for crystal frequency error compensation <sup>4</sup> |                                                                                                                               | +/-15 | +/-30       | -                                                    | ppm      |

| BR_F              | Bit rate, FSK                                                                           | Programmable Minimum modulation index is 0.5                                                                                  | 0.6   | -           | 500 <sup>5</sup>                                     | kb/s     |

| FDA               | Frequency deviation, FSK                                                                | Programmable                                                                                                                  | 0.6   | -           | 300                                                  | kHz      |

| BR_L              | Bit rate LoRa                                                                           | Min. for SF9, BW_L = 125kHz<br>Max. for SF5, BW_L = 500kHz                                                                    | 1.76  | -           | 62.5 <sup>6</sup>                                    | kb/s     |

| BW_L              | Signal BW, LoRa                                                                         | Programmable                                                                                                                  | 125   | -           | 500 <sup>6</sup>                                     | kHz      |

| SF                | Spreading factor for LoRa                                                               | Programmable, chips/symbol = 2^SF                                                                                             | 5     | -           | 9 <sup>7</sup><br>10 <sup>8</sup><br>11 <sup>9</sup> | -        |

| VTCXO             | Regulated voltage range for TCXO voltage supply                                         | Min/Max values in typical conditions,<br>Typ value for default setting<br>VDDop > VTCXO + 200mV                               | 1.6   | 1.7         | 3.3                                                  | V        |

| ILTCXO            | Load current for TCXO regulator                                                         |                                                                                                                               | -     | 1.5         | 4                                                    | mA       |

| TSVTCXO           | Start-up time for TCXO regulator                                                        | From enable to regulated voltage within 25mV from target                                                                      | -     | -           | 100                                                  | μs       |

| IDDTCXO           | Current consumption of the TCXO regulator                                               | Quiescent current<br>Relative to load current                                                                                 | -     | -<br>1      | 70<br>2                                              | μA<br>%  |

| ATCXO             | Amplitude voltage for external TCXO applied to XTA pin                                  | Provided through a 220 $\Omega$ resistor in series with a 10pF capacitance. See Section 4.1.4 "TCXO Control Block" on page 24 | 0.2   | 0.6         | 1.2                                                  | Vpk-pk   |

<sup>1.</sup> Phase Noise specifications are given for the recommended PLL BW to be used for the specific modulation/BR, optimized settings may be used for specific applications.

<sup>2.</sup> Phase Noise is not constant over frequency, due to the topology of the PLL, for two frequencies close to each other, the phase noise could change significantly.

<sup>3.</sup> Wake-up time till crystal oscillator frequency is within +/- 10ppm.

<sup>4.</sup> OSC\_TRIM is the available trimming range to compensate for crystal initial frequency error and to allow crystal temperature compensation implementation; the total available trimming range is higher and allows the compensation for all IC process variations.

## **3.5.3 Receive Mode Specifications**

Table 3-8: Receive Mode Specifications (Sheet 1 of 2)

| Symbol    | Description                                                                         | Conditions                                                | Min | Тур  | Max | Unit |

|-----------|-------------------------------------------------------------------------------------|-----------------------------------------------------------|-----|------|-----|------|

|           | Sensitivity 2-FSK,                                                                  | BR_F = 0.6kb/s, FDA = 0.8kHz, BW_F = 4kHz                 | -   | -125 | -   | dBm  |

|           | •                                                                                   | $BR_F = 1.2kb/s$ , $FDA = 5kHz$ , $BW_F = 20kHz$          | -   | -123 | -   | dBm  |

| RXS_2FB   | RX Boosted gain, see Section 9.6                                                    | $BR_F = 4.8kb/s$ , $FDA = 5kHz$ , $BW_F = 20kHz$          | -   | -118 | -   | dBm  |

| 1173_21 6 | "Receive (RX) Mode" on page 57, split                                               | BR_F = 38.4kb/s, FDA = 40kHz, BW_F = 160kHz               | -   | -109 | -   | dBm  |

|           | RF paths for Rx and Tx, RF switch insertion loss excluded                           | BR_F = 250kb/s, FDA = 125kHz, BW_F = 500kHz               | -   | -104 | -   | dBm  |

|           | insertion loss excluded                                                             | BR_F = 500kb/s, FDA = 300kHz, BW_F = 1000kHz <sup>1</sup> | -   | -94  | -   | dBm  |

|           | Sensitivity LoRa,                                                                   | BW_L = 125kHz, SF = 7                                     | -   | -124 | -   | dBm  |

|           | Rx Boosted gain, see Section 9.6                                                    | BW_L = 125kHz, SF = 9                                     | -   | -129 | -   | dBm  |

| RXS_LB    | "Receive (RX) Mode" on page 57, split                                               | $BW_L = 250kHz, SF = 7$                                   | -   | -121 | -   | dBm  |

| NX3_LD    |                                                                                     | $BW_L = 250kHz$ , $SF = 10$                               | -   | -129 | -   | dBm  |

|           | RF paths for Rx and Tx, RF switch                                                   | $BW_L = 500kHz, SF = 7$                                   | -   | -117 | -   | dBm  |

|           | insertion loss excluded                                                             | BW_L = 500kHz, SF = 11                                    | -   | -127 | -   | dBm  |

| RXS_2F    | Sensitivity 2-FSK Rx Power Saving gain with direct tie connection between Rx and Tx | BR_F = 4.8kb/s, FDA = 5kHz, BW_F = 20kHz                  | -   | -115 | -   | dBm  |

| RXS_L     | Sensitivity LoRa Rx Power Saving gain with direct tie connection between Rx and Tx  | BW_L = 125kHz, SF = 9                                     | -   | -125 | -   | dBm  |

| CCR_F     | Co-channel rejection, FSK                                                           |                                                           | -   | -9   | -   | dB   |

|           |                                                                                     | SF = 7                                                    | -   | 5    | -   | dB   |

| CCR_L     | Co-channel rejection, LoRa                                                          | SF = 11                                                   | -   | 16   | -   | dB   |

| ACR_F     | Adjacent channel rejection, FSK                                                     | Offset = +/- 50kHz                                        | -   | 45   | -   | dB   |

|           |                                                                                     | Offset = +/- 1.5 x BW_L                                   |     |      |     |      |

| ACR_L     | Adjacent channel rejection, LoRa                                                    | BW_L = 125kHz, SF = 7                                     | -   | 60   | -   | dB   |

|           |                                                                                     | $BW_L = 125kHz, SF = 9$                                   | -   | 65   | -   | dB   |

|           |                                                                                     | BR_F = 4.8kb/s, FDA = 5kHz, BW_F = 20kHz                  |     |      |     |      |

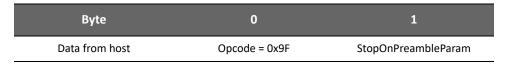

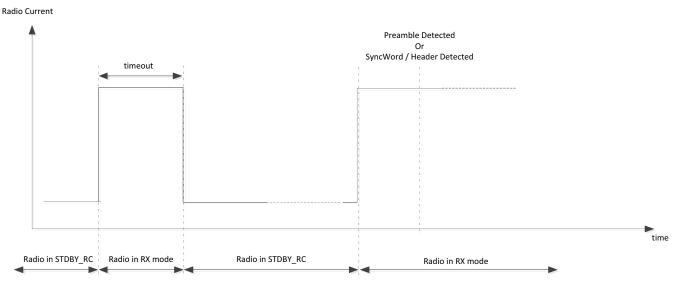

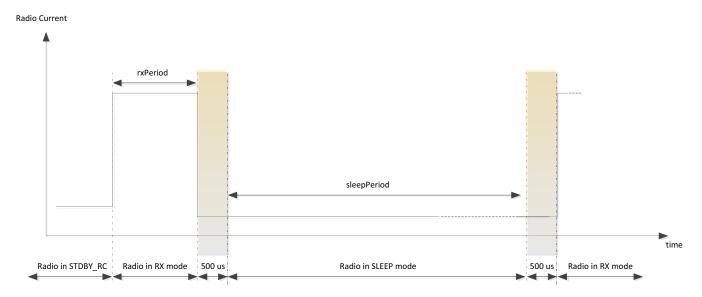

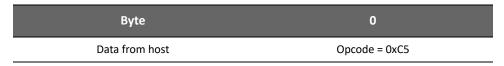

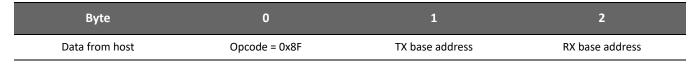

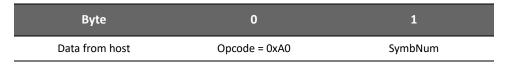

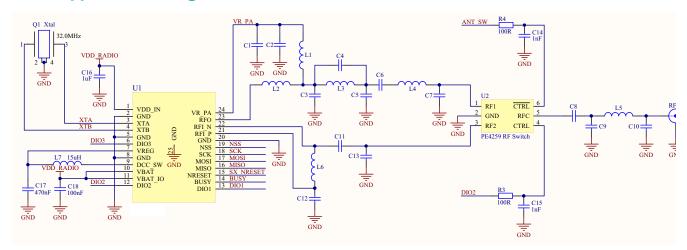

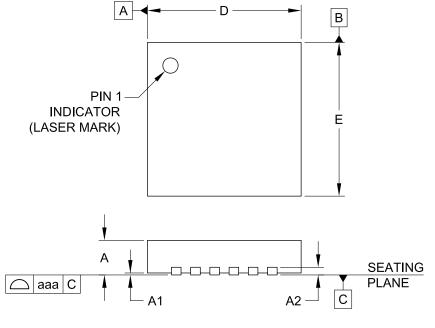

|           |                                                                                     | Offset = +/- 1MHz                                         | -   | 68   | -   | dB   |